# LOW-POWER OVERSAMPLED SIGNAL PROCESSING for DIGITAL RADIO RECEIVERS

by

HONG-KUI YANG, B.Eng., M.Eng.

A thesis submitted to

the Faculty of Graduate Studies and Research

in partial fulfillment of

the requirements for the degree of

Doctor of Philosophy

Department of Electronics

Carleton University Ottawa, Ontario March 22, 1998 © copyright 1998, Hong-Kui Yang

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-32351-X

## The undersigned hereby recommend to the Faculty of Graduate Studies and Research acceptance of the thesis,

## "LOW-POWER OVERSAMPLED SIGNAL PROCESSING for DIGITAL RADIO RECEIVERS"

submitted by HONG-KUI YANG, B.ENG., M.ENG.

in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Chair, Department of Electronics

Thesis Supervisor

External Examiner

Carleton University May 5, 1998

#### **Abstract**

Three techniques for reducing power consumption in oversampled receivers are developed: a method for improving the SNR attainable in power-efficient double-sampled  $\Delta\Sigma$  modulators; a combination of polyphase and multistage techniques to minimize power in decimation filtering; and a method of re-timing decimation to avoid the need for a re-sampling filter in the timing recovery circuits that follow the oversampled ADC.

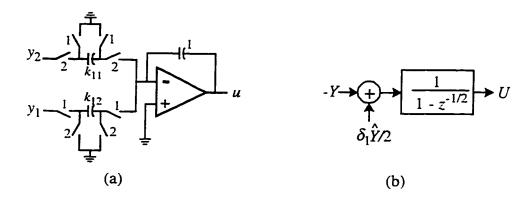

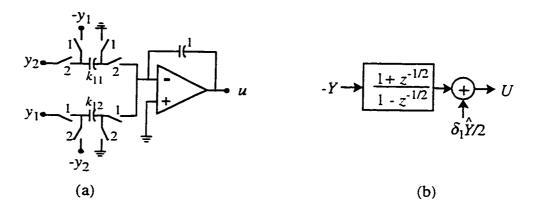

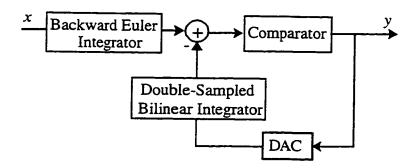

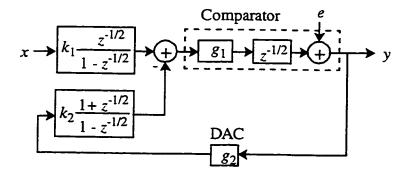

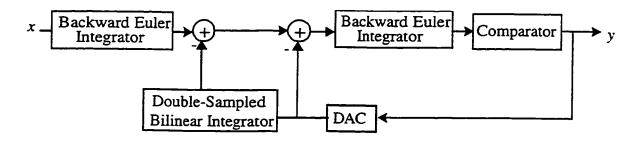

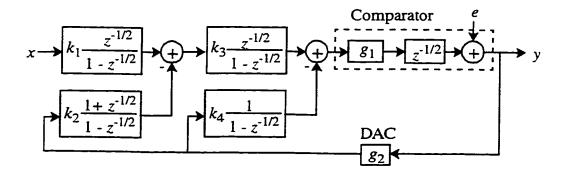

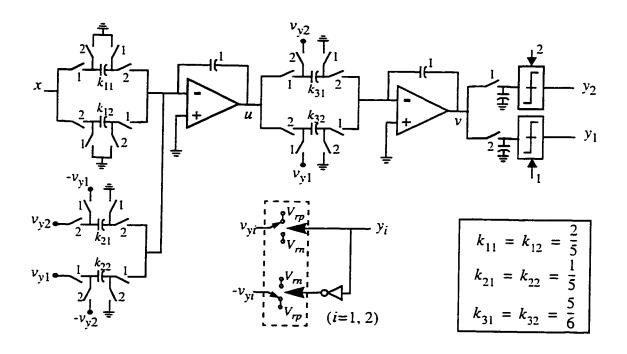

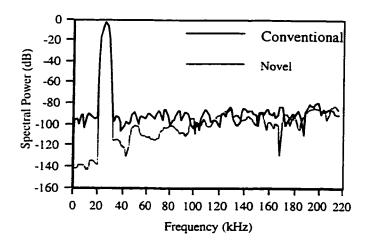

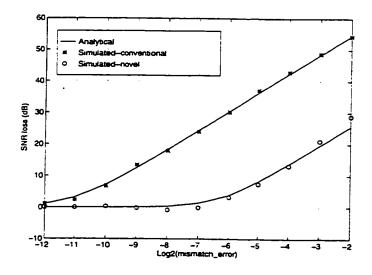

An analysis of mismatch effects in double-sampled SC  $\Delta\Sigma$  modulators shows that the feedback path from the quantizer to the first integrator is dominant, and we show how to use a bilinear integrator circuit to obtain first-order noise shaping of this error. While conventional double-sampled circuits are limited to 12-bit resolutions with typical components, the new circuit can go to 16-bit or better in the presence of the same mismatches.

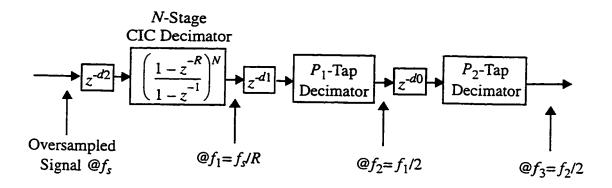

Cascaded accumulators (typical bit-width of 16~24 bits) in a CIC decimator often dominate power consumption and limit clock rates. Simply using multi-stage CIC decimators is not a solution. A combination of multi-stage CIC decimators with polyphase techniques mitigates these problems. We show how to design multi-stage polyphase CIC decimators by considering aliasing rejection for interference and quantization noise, and by budgeting the word-length in each stage. We provide a design scheme to simplify polyphase components again down to a handful of gates. An FPGA implementation of a 100-MHz digital downconverter using the new design shows a 5x power saving. The technique makes low-power and GHz-rate decimators practical by reducing the peak rate.

In an oversampled receiver, we show that moving timing recovery function into an existing decimator offers the fine resolution required at a much lower cost than interpolation method. This allows us to adjust timing by a typical 1/64 of a symbol period. Simply shifting this clock phase is not a solution, however, because it produces large "glitches" at the output. We show that the glitch settles out after N (typically 3 or 4) samples, so that it can be eliminated by using a dual-differentiator decimator. We analyze timing jitter and SNR bound due to interferer mixing with jitter and show a good fit with simulation. One experiment shows that the SNR bound result is within 1.5 dB of consistency with the estimate. We verify the stability and validity of the circuit by implementing an FPGA chip for BPSK.

### **Acknowledgments**

I owe special gratitude to my thesis supervisor Dr. Martin Snelgrove of Carleton University. Thank him for providing me the opportunity to continue my Ph.D. program at Carleton and giving me freedom to do what I am interested in. Thank him for his genuine guidance, remarkable insight into problems and valuable advice.

Part of the materials in Chapter 3 comes from my Ph.D. work conducted in the Technical University of Nova Scotia (TUNS, merged into Dalhousie University in 1997), Halifax, NS. I am very grateful to Dr. E.I. El-Masry of TUNS for all he did for me.

I acknowledge the following organizations for providing me financial support: OCRI/ NSERC Chair and Micronet program through Dr. Snelgrove, the Department of Electronics of Carleton University for teaching assistantships and scholarships, NSERC and Micronet program through Dr. El-Masry, TUNS for Rosetti Graduate Scholarships, and the Department of Electrical Engineering of TUNS for teaching assistantships.

I would like to thank many people in Dr. Snelgrove's high-speed IC lab. In particular, Nick Longo, research engineer, helped me build and test the FPGA chips. Phil and Theo, research engineers, prepared the test setup. Ash Swaminathan helped me build a double-sampled  $\Delta\Sigma$  modulator. Alana, research administrator, assisted in non-academic aspects.

Also, I would like to thank Drs. P. Edmonson, T. Aboulnasr, R. Hafez, M. Copeland, C. Plett, R. Mason and others to help further improve the quality of this thesis.

Finally and most importantly, thank my parents for their love, care and encouragement. Thank my wife for her loving support.

### **Table of Contents**

|                                                            | Page       |

|------------------------------------------------------------|------------|

| Abstract                                                   | i <b>v</b> |

| Acknowledgments                                            | V          |

| Table of Contents                                          | <b>vi</b>  |

| List of Tablesi                                            | x          |

| List of Figures                                            |            |

| List of Abbreviations                                      |            |

| List of Symbols x                                          |            |

| Chapter 1 Introduction                                     |            |

| Chapter 2 Background and Overview 8                        | ;          |

| 2.1 Digital Radio Receiver Architectures 8                 | !          |

| 2.2 (Double-Sampled) Delta-Sigma Modulators                | 5          |

| 2.3 Decimation and Digital Downconversion                  | 2          |

| 2.4 All-Digital Approaches to Symbol Timing Recovery       | 0          |

| 2.5 Summary                                                | 5          |

| Chapter 3 Double-Sampled Delta-Sigma Modulators            | 6          |

| 3.1 Analyses of Nonidealities                              | 7          |

| 3.1.1 Lowpass Delta-Sigma Modulators                       | 8          |

| 3.1.2 Bandpass Delta-Sigma Modulators                      | 3          |

| 3.2 A Novel Double-Sampling Technique                      | )          |

| 3.3 Novel Double-Sampled Lowpass Delta-Sigma Modulators 52 | 2          |

| 3.3.1 First-Order Modulator                                |            |

| 3.3.2 Second-Order Modulator 56                            |            |

| 3.3.3 Higher-Order Modulators 60                           |            |

| 3.4 Reduced Mismatch Requirements                          |            |

| 3.5 Implementation of a Second-Order Double-Sampled Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 3.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69                                          |

| Chapter 4 Design of Multi-Stage Polyphase CIC Decimators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71                                          |

| 4.1 Multi-Stage Polyphase Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72                                          |

| 4.2 Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75                                          |

| 4.2.1 Aliasing Attenuation and Droop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 75                                          |

| 4.2.2 Polyphase Components and Commutators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 82                                          |

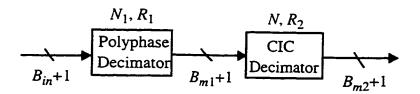

| 4.2.3 Word-Length Budget                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 86                                          |

| 4.2.4 Design Procedure Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 88                                          |

| 4.3 Decimation for Two Delta-Sigma Modulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89                                          |

| 4.4 FPGA Implementation of a DDC at 100 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 91                                          |

| 4.4.1 System and Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91                                          |

| 4.4.2 Test Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97                                          |

| 4.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |

| Chapter 5 Symbol Timing Recovery via Decimating Oversampled Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100                                         |

| Chapter 5 Symbol Timing Recovery via Decimating Oversampled Signals 5.1 Principle of Timing Adjustment by Decimating Oversampled Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 101                                         |

| 5.1 Principle of Timing Adjustment by Decimating Oversampled Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 101                                         |

| <ul> <li>5.1 Principle of Timing Adjustment by Decimating Oversampled Signals</li> <li>5.2 Adjustable-Timing-Phase Decimators</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 101                                         |

| <ul><li>5.1 Principle of Timing Adjustment by Decimating Oversampled Signals</li><li>5.2 Adjustable-Timing-Phase Decimators</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 101<br>104<br>109                           |

| <ul> <li>5.1 Principle of Timing Adjustment by Decimating Oversampled Signals</li> <li>5.2 Adjustable-Timing-Phase Decimators</li> <li>5.3 Practical Adjustable-Timing-Phase Decimators for Timing Recovery</li> <li>5.3.1 Spurious Transient Signals Created by Timing Phase Adjustment</li> </ul>                                                                                                                                                                                                                                                                                                  | 101<br>104<br>109<br>110                    |

| <ul> <li>5.1 Principle of Timing Adjustment by Decimating Oversampled Signals</li> <li>5.2 Adjustable-Timing-Phase Decimators</li> <li>5.3 Practical Adjustable-Timing-Phase Decimators for Timing Recovery</li> <li>5.3.1 Spurious Transient Signals Created by Timing Phase Adjustment</li> <li>5.3.2 Dual-Differentiator Adjustable Timing Phase CIC Decimators</li> <li>5.4 Performance Analysis</li> </ul>                                                                                                                                                                                      | 101<br>104<br>109<br>110<br>113             |

| <ul> <li>5.1 Principle of Timing Adjustment by Decimating Oversampled Signals</li> <li>5.2 Adjustable-Timing-Phase Decimators</li> <li>5.3 Practical Adjustable-Timing-Phase Decimators for Timing Recovery</li> <li>5.3.1 Spurious Transient Signals Created by Timing Phase Adjustment</li> <li>5.3.2 Dual-Differentiator Adjustable Timing Phase CIC Decimators</li> </ul>                                                                                                                                                                                                                        | 101 104 109 110 113 115                     |

| <ul> <li>5.1 Principle of Timing Adjustment by Decimating Oversampled Signals</li> <li>5.2 Adjustable-Timing-Phase Decimators</li> <li>5.3 Practical Adjustable-Timing-Phase Decimators for Timing Recovery</li> <li>5.3.1 Spurious Transient Signals Created by Timing Phase Adjustment</li> <li>5.3.2 Dual-Differentiator Adjustable Timing Phase CIC Decimators</li> <li>5.4 Performance Analysis</li> <li>5.4.1 Mean and Variance of Timing Jitter</li> </ul>                                                                                                                                    | 101 104 109 110 113 115 116                 |

| <ul> <li>5.1 Principle of Timing Adjustment by Decimating Oversampled Signals</li> <li>5.2 Adjustable-Timing-Phase Decimators</li> <li>5.3 Practical Adjustable-Timing-Phase Decimators for Timing Recovery</li> <li>5.3.1 Spurious Transient Signals Created by Timing Phase Adjustment</li> <li>5.3.2 Dual-Differentiator Adjustable Timing Phase CIC Decimators</li> <li>5.4 Performance Analysis</li> <li>5.4.1 Mean and Variance of Timing Jitter</li> <li>5.4.2 SNR Bound due to Tone interferer</li> </ul>                                                                                    | 101 104 109 110 113 115 116 122 128         |

| <ul> <li>5.1 Principle of Timing Adjustment by Decimating Oversampled Signals</li> <li>5.2 Adjustable-Timing-Phase Decimators</li> <li>5.3 Practical Adjustable-Timing-Phase Decimators for Timing Recovery</li> <li>5.3.1 Spurious Transient Signals Created by Timing Phase Adjustment</li> <li>5.3.2 Dual-Differentiator Adjustable Timing Phase CIC Decimators</li> <li>5.4 Performance Analysis</li> <li>5.4.1 Mean and Variance of Timing Jitter</li> <li>5.4.2 SNR Bound due to Tone interferer</li> <li>5.4.3 System Design Considerations</li> </ul>                                        | 101 104 109 110 113 115 116 122 128 128     |

| <ul> <li>5.1 Principle of Timing Adjustment by Decimating Oversampled Signals</li> <li>5.2 Adjustable-Timing-Phase Decimators</li> <li>5.3 Practical Adjustable-Timing-Phase Decimators for Timing Recovery</li> <li>5.3.1 Spurious Transient Signals Created by Timing Phase Adjustment</li> <li>5.3.2 Dual-Differentiator Adjustable Timing Phase CIC Decimators</li> <li>5.4 Performance Analysis</li> <li>5.4.1 Mean and Variance of Timing Jitter</li> <li>5.4.2 SNR Bound due to Tone interferer</li> <li>5.4.3 System Design Considerations</li> <li>5.5 Simulation and Experiment</li> </ul> | 101 104 109 110 113 115 122 128 128 134 134 |

| 5.7 Summary                                                        |

|--------------------------------------------------------------------|

| Chapter 6 Conclusions and Future Work                              |

| 6.1 Double-Sampling Techniques                                     |

| 6.2 Multi-Stage Polyphase CIC Techniques                           |

| 6.3 Re-Timing Decimation Techniques                                |

| 6.4 Future Work                                                    |

| Appendix A Equations for Double-Sampled Delta-Sigma Modulators 146 |

| Appendix B Polyphase DDCs and Circuit Designs                      |

| Appendix C Circuits Design for Symbol Timing Recovery              |

| Appendix D Adjustable-Delay Re-Timing CIC Decimators               |

| References                                                         |

## **List of Tables**

|           |                                                                 | Page |

|-----------|-----------------------------------------------------------------|------|

| Table 2.1 | Power consumption comparison in different SC techniques         | 20   |

|           | Polyphase components for $N_1 = 2$ and $N_1 = 3$                |      |

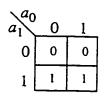

|           | Truth table for $-F_0(z)$                                       |      |

|           | Gate counts and power estimation in DDCs                        |      |

|           | Mean and variance values of timing jitter                       |      |

|           | Gate counts and power estimation in the timing recovery circuit |      |

|           | Coefficients in halfband and RRC filters                        |      |

## **List of Figures**

| Figure | Description                                                                                                                     | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Digital architecture for a modern digital radio receiver                                                                        | 1    |

| 1.2    | An oversampled re-timing scheme                                                                                                 | 3    |

| 2.1    | A typical superheterodyne receiver with baseband digitization                                                                   | 9    |

| 2.2    | A typical direct-conversion receiver                                                                                            | 11   |

| 2.3    | A superheterodyne radio receiver with IF digitization                                                                           | 12   |

| 2.4    | A wideband IF-digitization radio receiver                                                                                       | 14   |

| 2.5    | An ideal RF-digitization receiver                                                                                               | 15   |

| 2.6    | (a) A generic delta-sigma ADC and (b) its linear model                                                                          | 16   |

| 2.7    | Noise shaping in delta-sigma modulators                                                                                         | 18   |

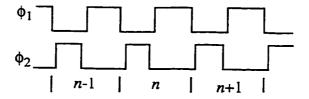

| 2.8    | A first-order double-sampled SC delta-sigma modulator                                                                           | 20   |

| 2.9    | A CIC decimator                                                                                                                 | 23   |

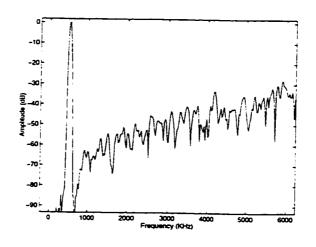

| 2.10   | Frequency response of a CIC decimator                                                                                           | 25   |

| 2.11   | Time misalignment in a narrowband DDC                                                                                           | 28   |

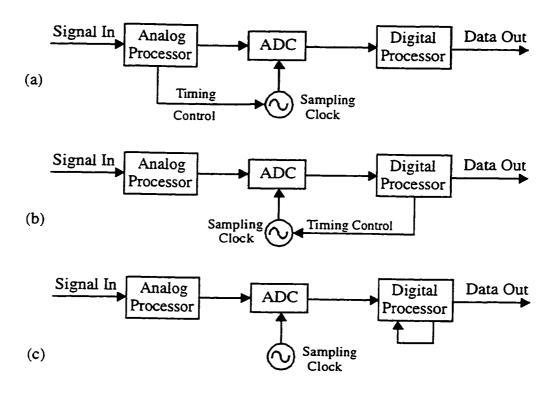

| 2.12   | Three categories for timing recovery: (a) analog method, (b) mixed method, and (c) all-digital method                           | 31   |

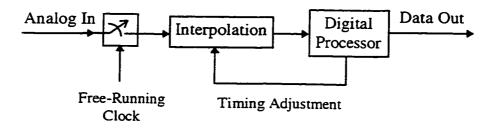

| 2.13   | Interpolation method for timing recovery                                                                                        | 32   |

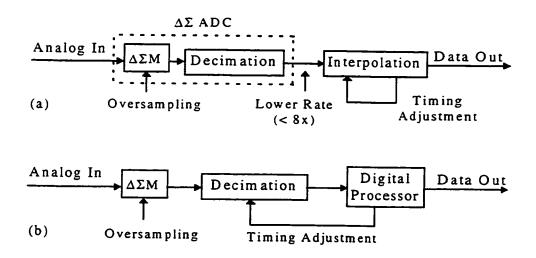

| 2.14   | All-digital timing recovery for delta-sigma modulated oversampled signals (> 64x): (a) interpolation and (b) decimation methods | 34   |

| 3.1    | A first-order double-sampled SC delta-sigma modulator                                                                           | 39   |

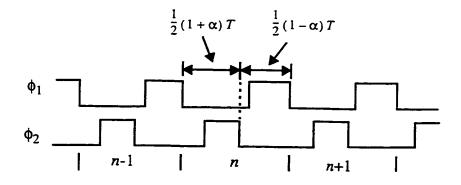

| 3.2    | A non-overlapping sampling clock scheme                                                                                         | 39   |

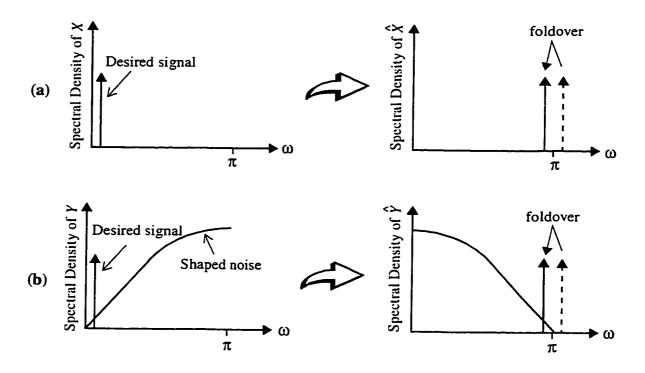

| 3.3    | A second-order double-sampled SC delta-sigma modulator                                                                          | 42   |

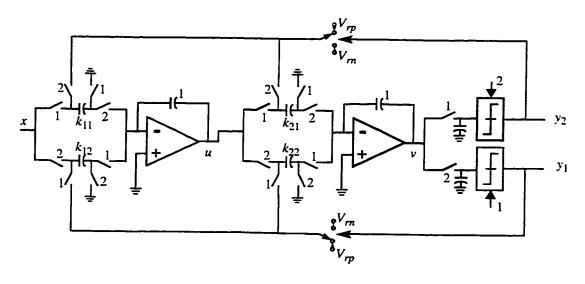

| 3.4    | Mismatch is a mixing process                                                                                                    | 43   |

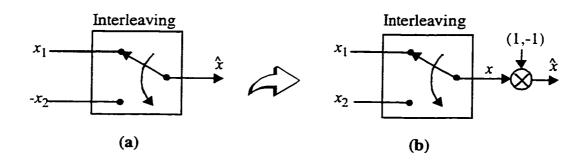

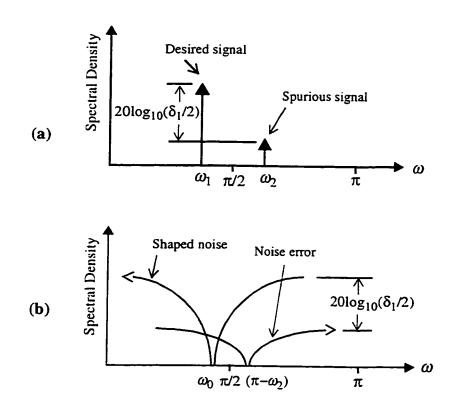

| 3.5    | Spectral translation due to mismatch                                                                                            | 44   |

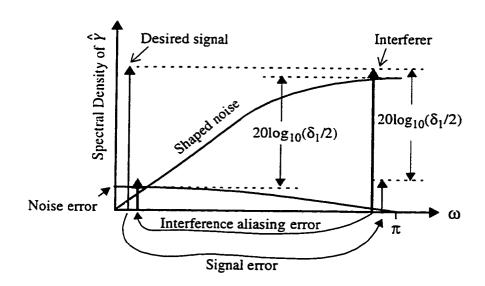

| 3.6    | Effects due to mismatch                                                                                                         | 45   |

| 3.7    | Non-uniform sampling clocks                                                                                                     | 46   |

| 3.8    | Errors generated by mismatch in a bandpass modulator: (a) the signal error and (b) the noise error                              | 49   |

| Figure | Description                                                                                                          | Page |

|--------|----------------------------------------------------------------------------------------------------------------------|------|

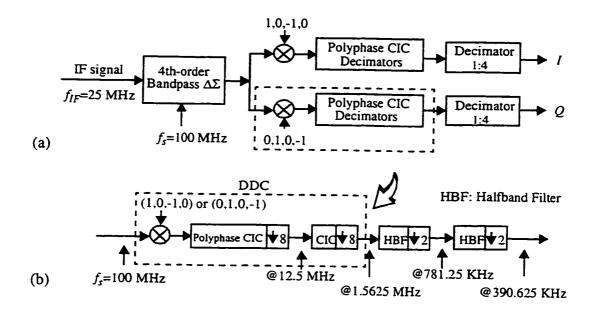

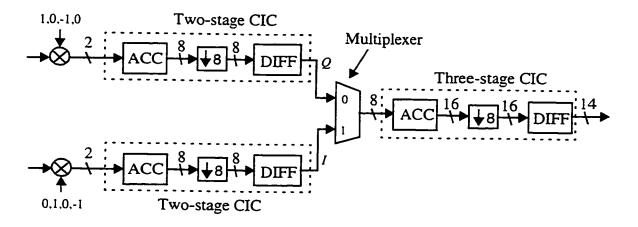

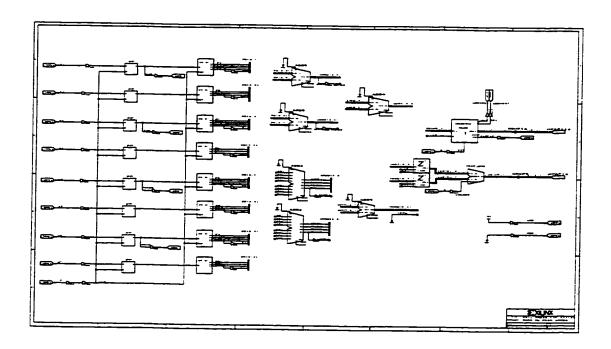

| 4.10   | An DDC using a multi-stage polyphase CIC decimator                                                                   | 92   |

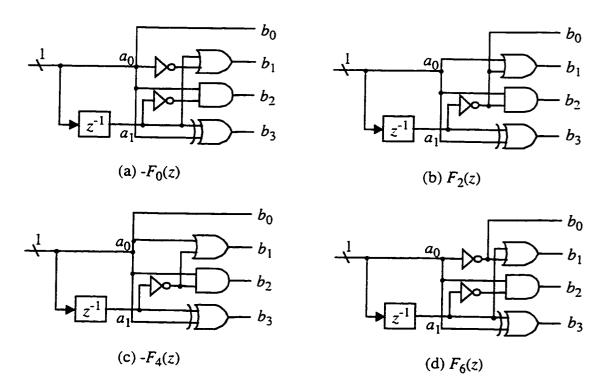

| 4.11   | Karnaugh maps for -F0(z)                                                                                             | 94   |

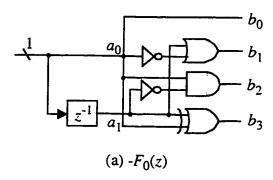

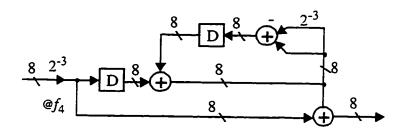

| 4.12   | Circuit of polyphase component                                                                                       | 94   |

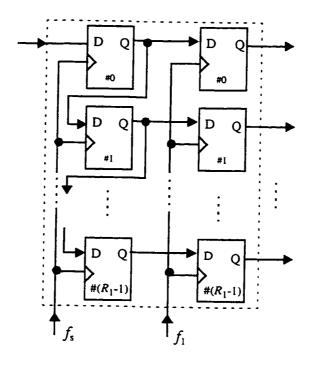

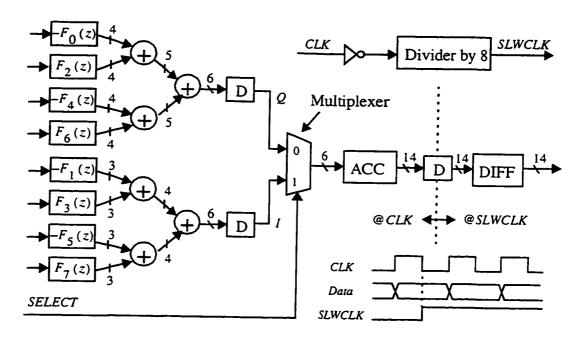

| 4.13   | FPGA architecture for a polyphase DDC                                                                                | 96   |

| 4.14   | A conventional DDC architecture                                                                                      | 97   |

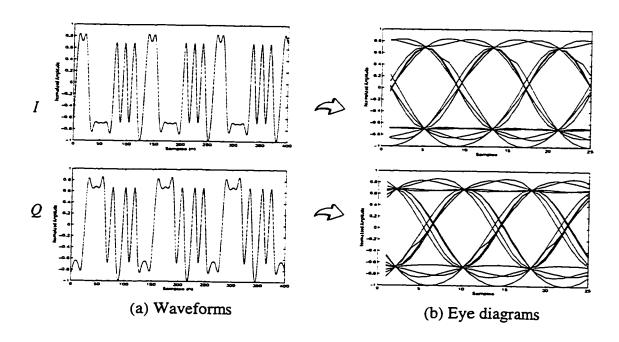

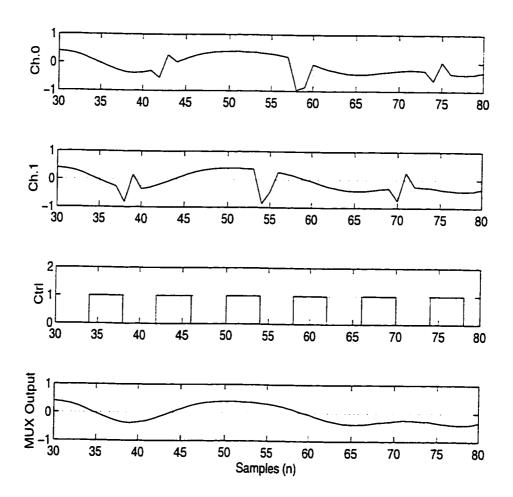

| 4.15   | The measured I and Q signals at the outputs of the DDC chip: (a) the l and Q waveforms, and (b) their eye diagrams   | 98   |

| 5.1    | Timing recovery by decimating an oversampled signal                                                                  | 102  |

| 5.2    | An N-stage adjustable-timing-phase CIC decimator                                                                     | 104  |

| 5.3    | Timing diagram for a nonuniform re-sampling                                                                          | 104  |

| 5.4    | Block diagram of symbol timing recovery using an adjustable-timing-phase CIC decimator                               | 106  |

| 5.5    | Timing diagram in the timing phase adjustment                                                                        | 108  |

| 5.6    | Spurious transient signal created by clock adjustment                                                                | 110  |

| 5.7    | Timing phase adjustment                                                                                              | 111  |

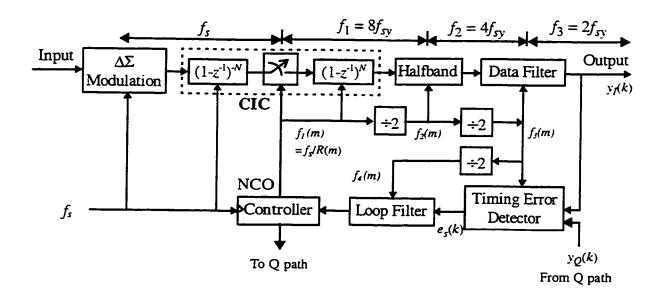

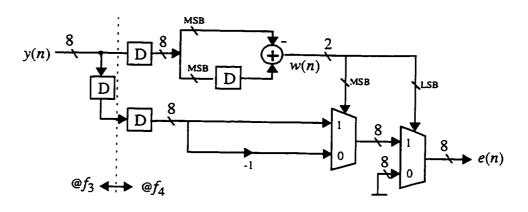

| 5.8    | A practical timing recovery loop with a dual-differentiator adjustable-timing-phase CIC decimator                    | 114  |

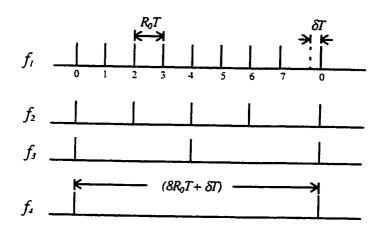

| 5.9    | Timing diagram in a dual-differentiator adjustable-timing-phase CIC decimator                                        | 114  |

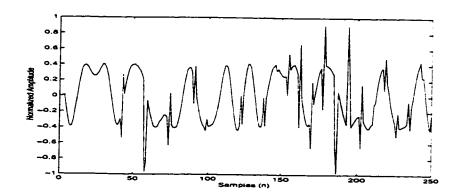

| 5.10   | Simulated waveforms                                                                                                  | 115  |

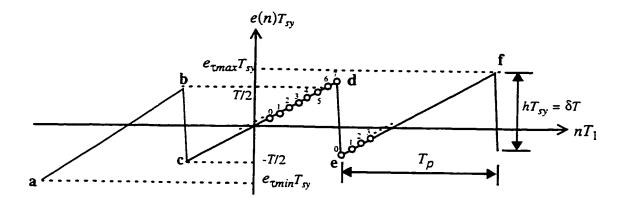

| 5.11   | Saw-tooth timing phase error                                                                                         | 118  |

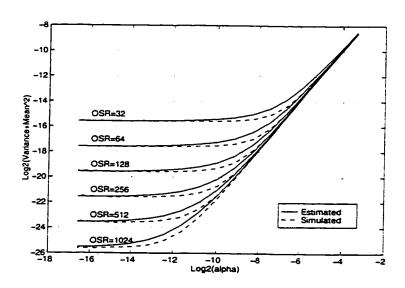

| 5.12   | Timing jitter variance versus alpha as a function of OSR                                                             | 121  |

| 5.13   | (Variance + mean^2) versus alpha as a function of OSR                                                                | 121  |

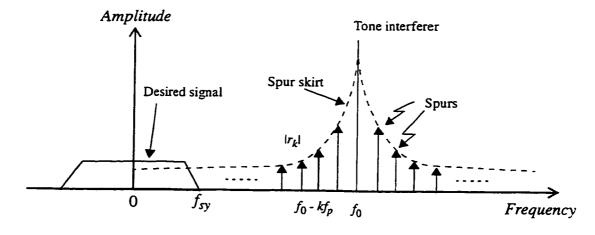

| 5.14   | Phase noise of a tone interferer due to timing adjustment                                                            | 123  |

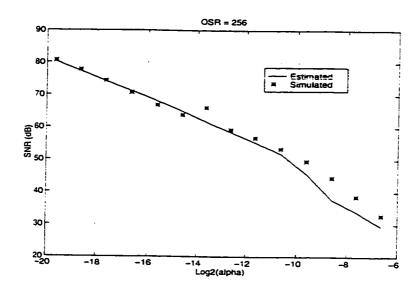

| 5.15   | SNR versus alpha for OSR = 256. A 0 dBc tone located at alternate channel                                            | 127  |

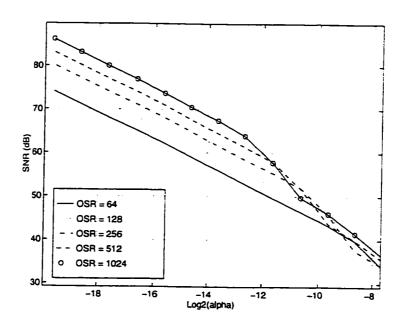

| 5.16   | SNR versus alpha as a function of OSR. A 0 dBc tone located at alternate channel                                     | 127  |

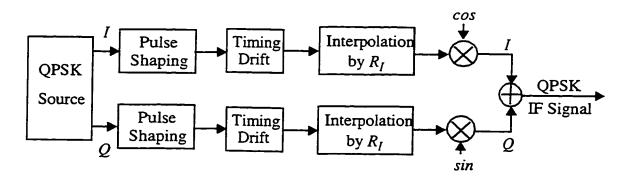

| 5.17   | A block diagram for generating an IF QPSK signal in SPW                                                              | 129  |

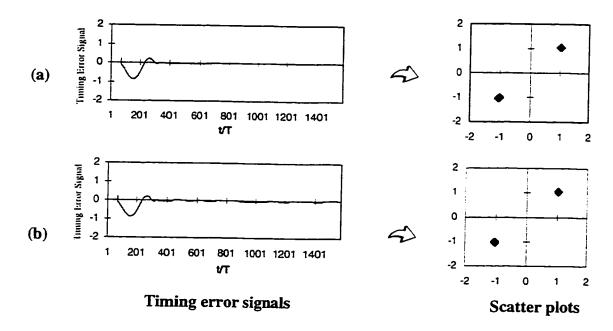

| 5.18   | Timing error signals (left) and scatter plots (right) for training sequence: (a) phase shift and (b) frequency drift | 131  |

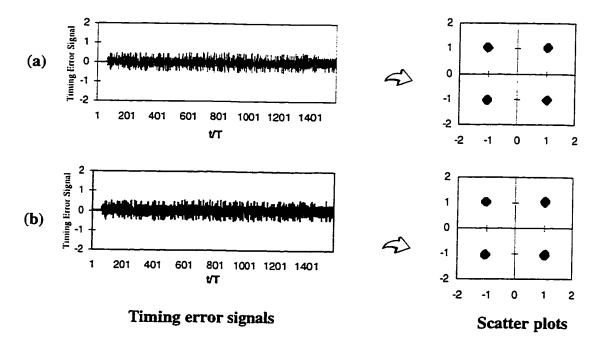

| 5.19   | Timing error signals (left) and scatter plots (right) for random data: (a) phase shift and (b) frequency shift       | 131  |

| Figure | Description                                                                      | Page |

|--------|----------------------------------------------------------------------------------|------|

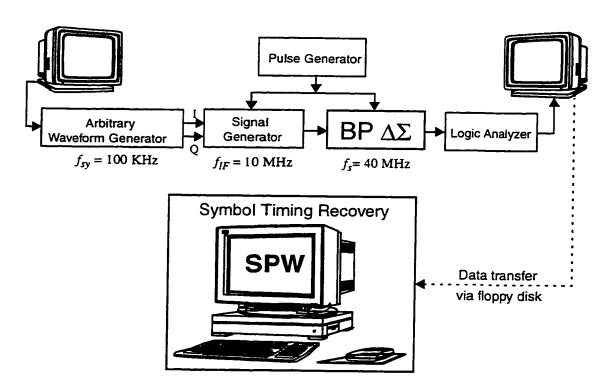

| 5.20   | Experiment setup for timing recovery of an QPSK IF system                        | 133  |

| 5.21   | Output scatter plots for two different cases                                     | 134  |

| 5.22   | A block diagram for the timing recovery via decimation                           | 135  |

| 5.23   | Timing diagram in the timing recovery circuit                                    | 136  |

| 5.24   | Measured results: timing errors and eye diagrams                                 | 139  |

| B.1    | A narrowband quadrature demodulator with IF digitization                         | 151  |

| B.2    | Narrowband DDCs using (a) two-phase, and (b) four-phase polyphase CIC decimators | 151  |

| B.3    | A wideband DDC based on a polyphase CIC decimation filter                        | 152  |

| B.4    | Circuits of polyphase components for the Q channel                               | 153  |

| B.5    | Circuits of polyphase components for the I channel                               | 154  |

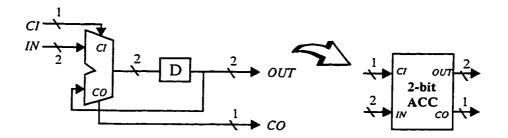

| B.6    | A 2-bit accumulator and its symbol                                               | 154  |

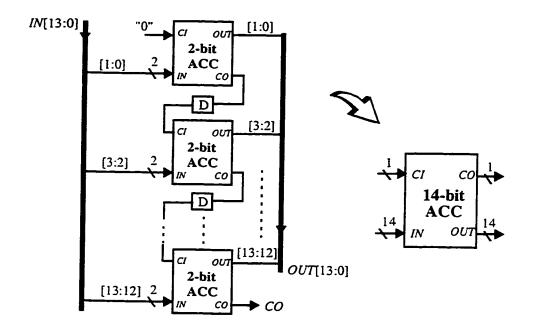

| B.7    | A 14-bit pipelined accumulator and its symbol                                    | 155  |

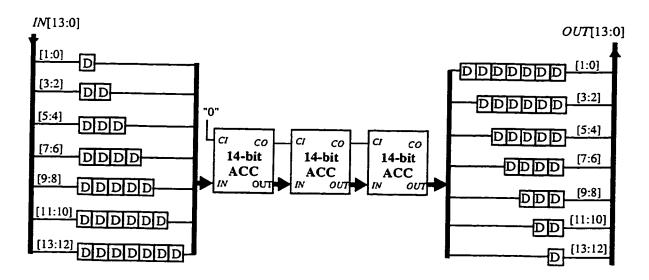

| B.8    | A cascaded 3-stage, 14-bit pipelined accumulator                                 | 155  |

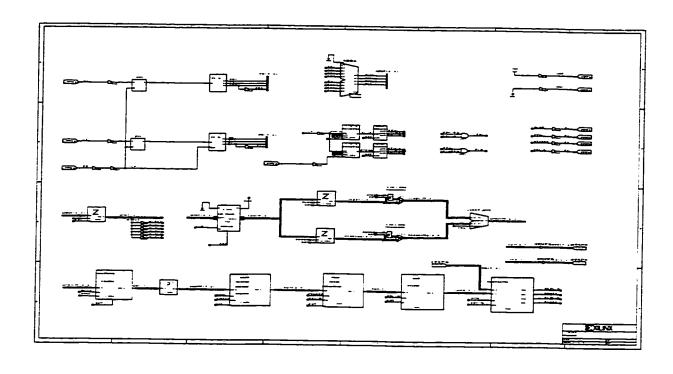

| B.9    | Schematic diagram for the proposed polyphase DDC                                 | 156  |

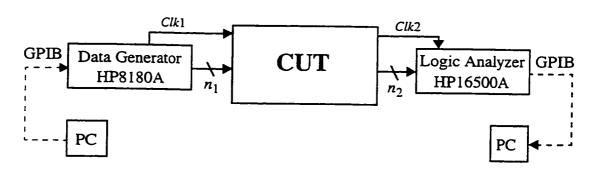

| B.10   | Test setup for the CUT                                                           | 157  |

| C.1    | Polyphase components in the 4-phase DDC for the channel                          | 158  |

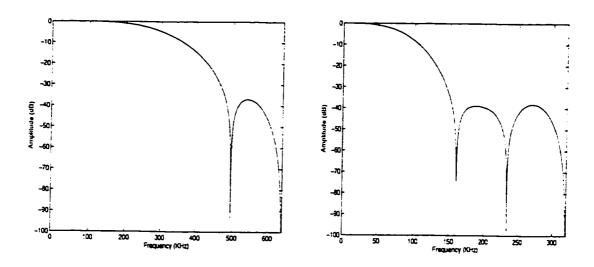

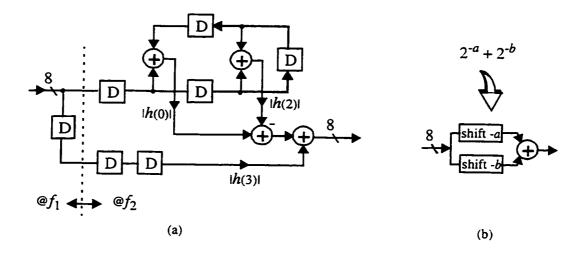

| C.2    | Frequency responses of (a) the halfband filter and (b) the RRC filter            | 160  |

| C.3    | (a) The halfband filter and (b) its coefficient implementation                   | 160  |

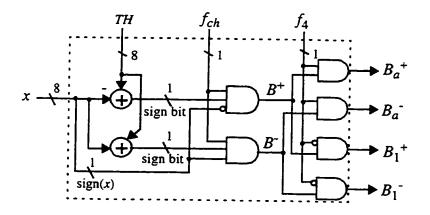

| C.4    | Circuit for the timing error detector                                            | 161  |

| C.5    | Circuit for the loop filter                                                      | 162  |

| C.6    | Circuit for the comparator                                                       | 162  |

| C.7    | Circuit for the 7/8/9 variable counter                                           | 163  |

| C.8    | Schematic diagram for the proposed timing recovery Circuit                       | 164  |

| D.1    | An adjustable-delay CIC decimator                                                | 166  |

| D.2    | A variable delay implemented using a circular buffer                             | 168  |

### **List of Abbreviations**

ADC Analog to Digital Converter

ACC Accumulator

ASIC Application Specific Integrated Circuit

BER Bit Error Rate

BiCMOS Bipolar and Complementary Metal Oxide Semiconductor

BPSK Binary Phase Shift Keying

CDMA Code Division Multiple Access

CIC Cascaded Integrator and Comb

CMOS Complementary Metal Oxide Semiconductor

CSD Canonical Signed-Digit

CUT Circuit Under Test

DC Direct Current

DAC Digital to Analog Converter

DDC Digital Down Converter

DDS Digital Direct Synthesis

DSP Digital Signal Processing

ΔΣM Delta-Sigma Modulator

EOSR Effective Oversampling Ratio.

FIR Finite Impulse Response

FM Frequency Modulation

FPGA Field Programmable Gate Array

FSM Finite State Machine

GHz Giga Hertz

GPIB General Purpose Interface Bus

GSM Global System for Mobile Communications

GMSK Gaussian Minimum Shift Keying

HBT Heterojunction Bipolar Transistor

IC Integrated Circuit

VCO

VLSI

Voltage Controlled Oscillator

Very Large Scale Integration

IF Intermediate Frequency I In-phase **IOSR** Intermediate Oversampling Ratio KHz Kilo Hertz LF Lowpass Filter or Loop Filter LNA Low Noise Amplifier ISDN Integrated Service Digital Network LO Local Oscillator MHz Mega Hertz NCO Numerically Controlled Oscillator OSR Oversampling Ratio PC Personal Computer PCS Personal Communication Services PLL Phase Locked Loop Q Quadrature QAM Quadrature Amplitude Modulation Quadrature Phase Shift Keying QPSK RF Radio Frequency ROM Read Only Memory RRC Root Raised Cosine SAW Surface Acoustic Wave SC Switched Capacitor SFDR Spurious Free Dynamic Range SNR Signal to Noise Ratio TDMA Time Division Multiple Access

| $\Delta y(n)$                         | transient error signal                                                             |

|---------------------------------------|------------------------------------------------------------------------------------|

| $\delta_{i}$                          | mismatch error between path gains $k_{i1}$ and $k_{i2}$ , $i = 1, 2, 3$            |

| e(n)                                  | quantization noise or the normalized timing error in timing recovery               |

| $e_s(n)$                              | timing error signal from a timing error detector                                   |

| $e_{\tau}(n)$                         | timing error normalized to the symbol rate                                         |

| e <sub>tmax</sub> , e <sub>tmin</sub> | maximum and minimum timing error, respectively                                     |

| e <sub>rms</sub>                      | rms quantization error                                                             |

| <i>E</i> (.)                          | mean value                                                                         |

| E(f)                                  | spectral density of quantization noise                                             |

| $E_1, E_2$                            | discrete-time quantization noise on phases 1 and 2 in the z-domain                 |

| $E_{di}$                              | quantization noise in the decimation stage, $i = 1, 2, 3, 4$                       |

| $E_{m1}$ , $E_{m1}$                   | error introduced by mismatch in the first and second integrators in double-        |

|                                       | sampled $\Delta\Sigma$ modulators                                                  |

| EOSR                                  | effective OSR                                                                      |

| f                                     | frequency variable                                                                 |

| $f_c$                                 | clock rate ( $f_s = f_c$ for single-sampling and $f_s = 2f_c$ for double-sampling) |

| $f_{s0}$                              | clock for the implemented timing-phase-adjustable CIC decimator                    |

| $f_{l}$                               | clock for differentiator 0 in a dual-differentiator CIC decimator                  |

| $f_{	exttt{la}}$                      | clock for differentiator 1 in a dual-differentiator CIC decimator                  |

| $f_2$                                 | clock at the output of halfband filter in the timing recovery loop                 |

| $f_3$                                 | clock at the output of data filter in the timing recovery loop                     |

| $f_4$                                 | clock for the loop filter in the timing recovery loop                              |

| $f_0$                                 | cutoff frequency                                                                   |

| $f_{ch}$                              | control signal used in gating the comparator in timing recovery                    |

| $f_{IF}f_{IFI}, f_{IF2}$              | IF carrier frequencies                                                             |

| $f_{P}$                               | frequency of the saw-tooth timing error waveform, $f_P = 1/T_P$                    |

| $f_s$                                 | sampling rate or sampling frequency, $f_s = 1/T$                                   |

| $f_{sy}$                              | symbol rate, $f_{sy} = 1/T_{sy}$                                                   |

| $F_i(z)$                              | the $i^{th}$ polyphase component, $i = 0, 1, 2,$                                   |

|                                       |                                                                                    |

| $\phi_1, \phi_2$            | two-phase non-overlapping clocks                                                       |

|-----------------------------|----------------------------------------------------------------------------------------|

| $\phi_{1b}, \phi_{2b}$      | inverted versions of $\phi_1$ , $\phi_2$ respectively                                  |

| $\phi_{1db}$ , $\phi_{2db}$ | delayed versions of $\phi_1$ , $\phi_2$ respectively                                   |

| $\phi_{1d}, \phi_{2d}$      | delayed versions of $\phi_{1db}$ , $\phi_{2db}$ respectively                           |

| 81                          | comparator gain in a $\Delta\Sigma$ modulator                                          |

| 82                          | DAC gain in a $\Delta\Sigma$ modulator                                                 |

| h                           | timing phase adjustment step size                                                      |

| $h_{i}(n)$                  | coefficients in the impulse response of a FIR filter                                   |

| H(z)                        | transfer function in the z-domain                                                      |

| $H_1(z)$                    | the first transfer function in a cascaded structure                                    |

| $H_2(z)$                    | the second transfer function in a cascaded structure                                   |

| $H_X(z)$                    | the signal transfer function in a $\Delta\Sigma$ modulator                             |

| $H_{E}(z)$                  | the noise transfer function in a $\Delta\Sigma$ modulator                              |

| i                           | integer variable                                                                       |

| in+, in-                    | differential inputs                                                                    |

| IOSR                        | intermediate oversampling ratio                                                        |

| k                           | integer variable                                                                       |

| $k_i$                       | path gain in a linear double sampling $\Delta\Sigma$ modulator model, $i = 1, 2, 3, 4$ |

| $k_{i1}, k_{i2}$            | a pair of path gains in a double sampling SC circuit, $i = 1, 2, 3, 4$                 |

| $k_s$                       | bit reduction due to the design scheme for polyphase components                        |

| $m_{	au}$                   | mean timing error                                                                      |

| M                           | $\Delta\Sigma$ modulator order                                                         |

| $M_i$                       | MOS transistors, $i = 1, 2,$                                                           |

| $M_P$                       | number of subfilters in implementing the re-timing interpolator                        |

| $M_L$                       | number of taps in a polyphase component                                                |

| MSB(.)                      | most significant bit                                                                   |

| MIN(x,y)                    | minimum value of $x$ and $y$                                                           |

| n                           | integer variable                                                                       |

| N <sub>conven</sub>         | rms noise power in the desired band of the conventional double-sampled                 |

|                             |                                                                                        |

|                   | $\Delta\Sigma$ modulator due to capacitor mismatch                                  |

|-------------------|-------------------------------------------------------------------------------------|

| $N_{novel}$       | rms noise power in the desired band of the novel double-sampled $\Delta\Sigma$ mod- |

|                   | ulator due to capacitor mismatch                                                    |

| $n_1, n_2$        | word-lengths in the input and output of the CUT                                     |

| $N$ , $N_1$       | $N$ -stage or $N_1$ -stage CIC decimator (the order of a CIC decimator)             |

| $N_h, N_d$        | numbers of taps in the halfband and data filters respectively                       |

| $N_s$             | total spur power in the desired band introduced by interferer mixing                |

| N(f)              | spectral density of shaped modulation noise                                         |

| outp, outn        | differential outputs                                                                |

| out+, out-        | differential outputs                                                                |

| OSR               | oversampling ratio                                                                  |

| $P_0(M)$          | rms noise power in the desired band in an $M^{th}$ order $\Delta\Sigma$ modulator   |

| $P_i$             | quantization noise power at different decimation stage, $i = 1, 2, 3, 4$            |

| $P_s$             | power consumption in a single-sampled SC circuit                                    |

| $r_i$             | coefficients in the Fourier transform, i is an integer.                             |

| $R, R_1, R_2$     | downconversion or upconversion factor where $R = R_1 R_2$                           |

| $\overline{R}$    | average downsampling factor of R due to timing adjustment                           |

| $R_{\mathrm{I}}$  | up-sampling ratio                                                                   |

| SNR               | signal to noise ratio                                                               |

| $\sigma_{	au}$    | rms value of timing jitter                                                          |

| T                 | sampling period, $T = 1/f_s$                                                        |

| $T_{P}$           | period of the saw-tooth timing error waveform                                       |

| TH                | threshold for the comparator in timing recovery                                     |

| $	au$ and $	au_e$ | the actual and estimated delays in timing recovery loop                             |

| $u_1(n), u_2(n)$  | discrete-time signals on phases 1 and 2 at $f_s/2$                                  |

| $U_1, U_2$        | discrete-time signals on phases 1 and 2 in the z-domain                             |

| Ù                 | $\bar{U} = U_1 z^{-1/2} - U_2$                                                      |

| $V_{dd}$          | positive power supply                                                               |

| $v_1(n), v_2(n)$  | discrete-time signals on phases 1 and 2 at $f_c = f_s/2$                            |

|                   |                                                                                     |

| $v_{y1}, v_{y2}$      | analog signals converted from outputs $y_1$ and $y_2$ .                               |

|-----------------------|---------------------------------------------------------------------------------------|

| $V_1, V_2$            | discrete-time signals on phases 1 and 2 in the z-domain                               |

| $V_{rn}, V_{rp}$      | negative and positive reference voltages in double sampling $\Delta\Sigma$ modulators |

| $V_r$                 | $V_r = \frac{V_{rp} - V_{rn}}{2}$ , the effective reference voltage                   |

| $\Delta V_r$          | $\Delta V_r = \frac{V_{rp} + V_{rn}}{2}$ , the common-mode reference voltage          |

| <b>V</b>              | $\hat{V} = V_1 z^{-1/2} - V_2$                                                        |

| w(n)                  | an intermediate variable used in deriving the timing error detector circuit           |

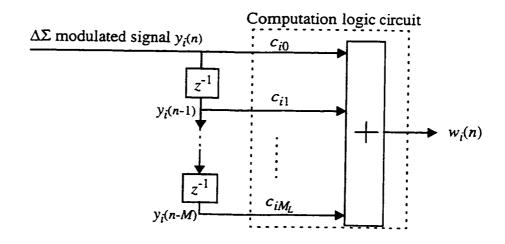

| $w_i(n)$              | the output of $i^{th}$ polyphase component, $i = 0, 1, 2,$                            |

| $\omega$ , $\omega_i$ | radian frequency, $i = 0, 1, 2$                                                       |

| x(n)                  | discrete-time input signal at $f_s$                                                   |

| $x_1(n), x_2(n)$      | inputs on phases 1 and 2 at $f_s/2$ in double-sampled $\Delta\Sigma$ modulators       |

| X                     | input signal at $f_s$ in the z-domain                                                 |

| $X_1, X_2$            | inputs on phases 1 and 2 in the z-domain in double-sampled $\Delta\Sigma$ modulators  |

| â                     | variable of $\hat{X}$ in the time-domain                                              |

| Ż                     | $\hat{X} = X_1 z^{-1/2} - X_2$                                                        |

| y(n)                  | discrete-time output signal                                                           |

| $y_1(n), y_2(n)$      | output signals in double-sampled $\Delta\Sigma$ modulators                            |

| $y_d(n)$              | hard-decision value (1 or 0) based on $y(n)$ , in the timing recovery circuit         |

| $y_I(n), y_Q(n)$      | outputs of the $I$ and $Q$ channels in timing recovery                                |

| Y(z)                  | output in the z-domain                                                                |

| $Y_1, Y_2$            | outputs on phases 1 and 2 in the z-domain                                             |

| ŷ                     | variable of ? in the time-domain                                                      |

| Ÿ                     | $Y = Y_1 z^{-1/2} - Y_2$                                                              |

| z, z <sub>1</sub>     | variables in the z-transform, $z = e^{j\omega T}$ and $z_1 = z^{R1}$                  |

## Chapter 1 Introduction

Personal communication services (PCS) are growing rapidly due to advances in digital wireless communication theory, Very Large Scale Integration (VLSI) technology, and Digital Signal Processing (DSP) techniques [Skla88], [Padg95], [Rapp96]. To accommodate this tremendous growth, engineers specializing in radio systems, DSP and VLSI are teaming up to define new architectures and methods for digital radio receivers.

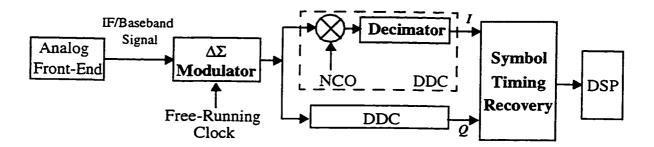

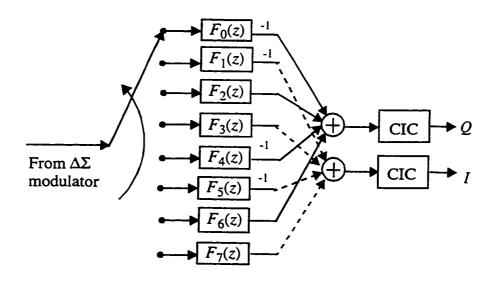

Modern radio receivers digitize input signals early [Meyr95], [Mito95], often with an oversampled Analog-to-Digital Converter (ADC) [Thur95]. A typical architecture of a digital radio receiver is shown in Figure 1.1. The receiver consists of an analog front-end, a delta-sigma ( $\Delta\Sigma$ ) modulator ADC, Digital Downconverters (DDCs), symbol timing recovery and other DSP functions. The front-end output may be an Intermediate Frequency (IF) signal or a baseband signal. In an IF-digitization receiver, a bandpass  $\Delta\Sigma$  modulator digitizes the IF signal and I/Q signals are separated by two DDCs which consist of decimators and Numerically Controlled Oscillators (NCOs). In a baseband-digitization variation, two lowpass  $\Delta\Sigma$  modulators digitize the I and Q signals and DDCs are simply decimators.

Figure 1.1 Digital architecture for a modern digital radio receiver

#### A. Motivations

Traditionally, power for cellular telephony has been dominated by the transmitter, but for modern portable applications it is often of key importance to reduce power consumption in receiver: receivers defines standby time, which is of increasing importance as decreasing

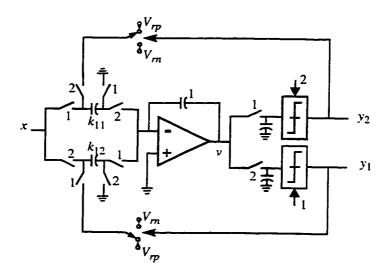

- with typical components and SNR degradation is negligible compared to the improvement that can be obtained by double-sampling.

- 3- We verify the proposed architecture by a low power implementation. The HSPICE simulation shows that the SNR is 81 dB with an effective OSR of 100. The estimated power is 1 mW at 50 MHz clock rate compared to a low power second-order  $\Delta\Sigma$  modulator consuming 2.5 mW at 4 MHz clock rate [Rabi97].

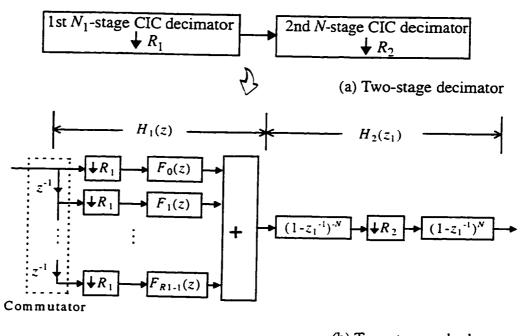

- 4- CIC decimators are used in  $\Delta\Sigma$  ADCs. The high-speed part of a CIC decimator typically consist of three or four 16~24-bit accumulators which often dominate power consumption and limit clock rates. Simply using a multi-stage CIC decimator is not a solution. We show that these problems can be mitigated by combining multi-stage CIC decimators with polyphase techniques. We derive architectures for the multi-stage polyphase decimators and show that this technique makes decimation possible in micropower and GHz  $\Delta\Sigma$  ADCs.

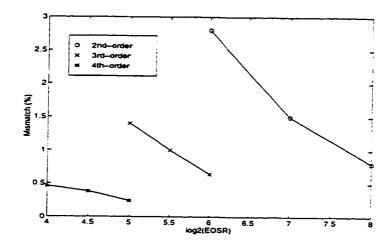

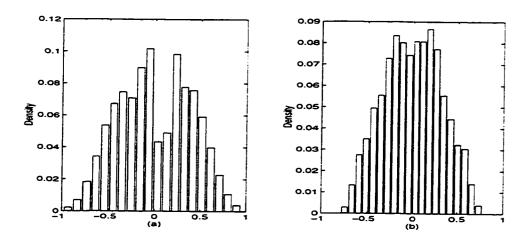

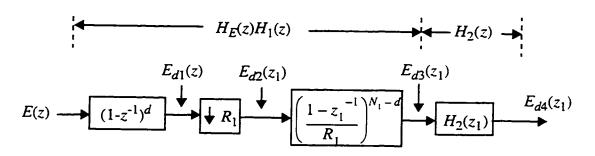

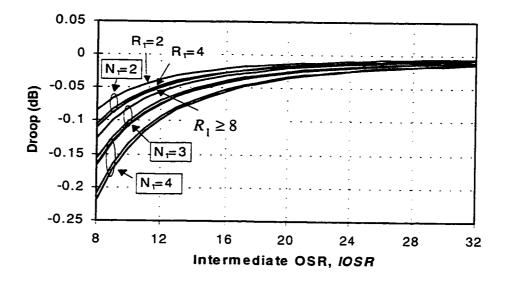

- 5- We advance the art of design for multi-stage polyphase CIC decimators and develop design methods to simplify circuits. We show that the order of the first full-rate polyphase decimator can be equal to the order of the  $\Delta\Sigma$  modulator. This saves  $\log_2(R_1)$  bits, where  $R_1$  is the first downsampling ratio. The SNR loss is insignificant in comparison to the actual SNR obtained by a high speed  $\Delta\Sigma$  modulator. A design scheme to simplify the realization of polyphase components without using adders for a  $\Delta\Sigma$  modulated signal is proposed. It further reduces the word-lengths of the polyphase components and the subsequent CIC decimator by 2~3 bits. We also show how to design a multi-stage polyphase decimator by budgeting the word-length in each stage.

- 6- We demonstrate the above technique for high speed and low power by implementing a Field Programmable Gate Array (FPGA) DDC chip which consists of a multi-stage polyphase CIC decimator. This chip is able to downconvert an IF signal modulated by a Quadrature Phase Shift Keyed (QPSK) scheme at 100 MHz. We show that it achieves a 5x power saving compared with a conventional multi-stage version. The measured output SNR is 56 dB (80.1 dB in the desired band) and the measured eye diagram shows a negligible Eb/No loss (< 0.1 db), which are in agreement with theoretical results.

- 7- A technique to move the timing recovery function into the CIC decimation in a  $\Delta\Sigma$  mod-

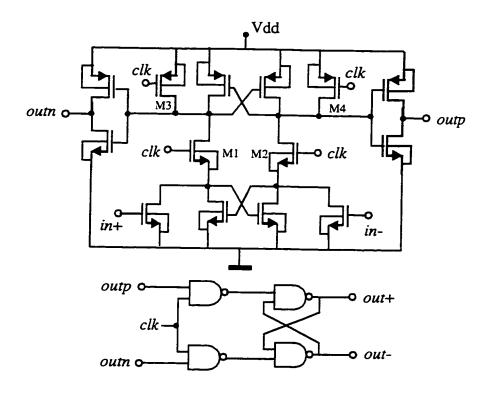

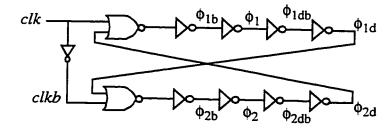

ulation based receiver is proposed. The timing resolution is 1/(2\*OSR) of a symbol period, where the OSR is typically 64 or higher. Simply changing the re-sampling clock in a CIC decimator, however, creates glitches at the output which settle out after N (typically three or four) samples. The glitches affect the timing error detection. We propose a solution to eliminate the "glitches" by a dual-differentiator CIC decimator. In the scheme, the signal is re-sampled by two different clocks into two differentiators where timing changes are separated by four samples. The output is taken alternately from those two differentiators. The proposed method offers the fine resolution required in modulation schemes such as high-order QAM at a much lower cost than interpolation method.

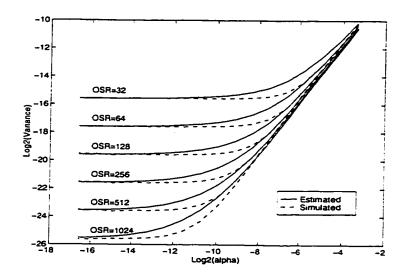

- 8- We derive for the mean and variance of the timing jitter introduced by this method. We show that an interferer at the out-of-band channel creates in-band spur noise due to its mixing with timing jitter, which limits the SNR. We present curves that can be used for system design in the specific practical case of an alternate-channel interferer. We show a good fit between theory and simulation. The performance is determined by  $\alpha$  (the transmitter and receiver clock rate difference) and OSR: (a) for a small  $\alpha < \frac{1}{7OSR}$ , the rms timing jitter is dominated by OSR and its slope is -3 dB per octave of OSR. The slope of SNR bound for interferer mixing is -3 dB per octave of  $\alpha$  or 3 dB per octave of OSR. (b) for a large  $\alpha > \frac{4}{7OSR}$ , the rms timing jitter and SNR bound are dominated by the frequency difference  $\alpha$ . Their slopes are 3 dB and 6 dB per octave of  $\alpha$  respectively.

- 9- One experiment demonstrates that the method works in the presence of alternate interferer and in conjunction with carrier recovery. The measured SNR bound is within 1.5 dB of consistency with the estimate. The low complexity and stability of the technique is demonstrated by implementing an FPGA chip. The chip is able to do re-timing for a Binary Phase Shift Keying (BPSK) IF signal. It is functional and stable. The measured eye diagram shows that an Eb/No degradation bound of about 0.75 dB is introduced by the timing recovery loop.

#### C. Thesis Organization

This thesis is organized as follows:

Chapter 1 presents the motivations, contributions and organizations of this thesis.

Chapter 2 provides necessary background on digital radio receiver architectures, in-

imators to wideband and narrowband DDCs are discussed. Detailed circuit designs for an 100 MHz FPGA DDC are also described. In **Appendix C**, detailed circuit designs for the symbol timing recovery FPGA chip are given. A preliminary study on a re-timing scheme based on adjusting delays in the loop is presented in **Appendix D**.

## Chapter 2 Background and Overview

Digital techniques play a key role in building high performance, low cost and low power receiver subsystems for cellular and PCS communications [Brod92], [Meyr95], [Bain95], [Wepm95]. Many modern radio receiver architectures utilizing digital techniques have been developed [Coy92], [Ches94], [Abid95], [Mito95], [Thur95] and they can be categorized as baseband and IF digitization receivers. The key components in these architectures are ADCs, decimators or DDCs, re-timing circuits and other DSP functions.

One of the major concerns in handset devices is power consumption. The key to success is developing low power circuits such as  $\Delta\Sigma$  ADCs, high-rate decimators and all-digital baseband processing such as symbol timing recovery. Many methods have been developed to minimize power at different levels such as at architecture, circuit and IC technology levels.

This section provides background knowledge and overviews of digital radio architectures, (double-sampled)  $\Delta\Sigma$  modulation ADCs, low power decimators (and DDCs), and digital re-timing techniques. The section is organized as follows: an overview of modern digital radio receiver architectures is given in Section 2.1.  $\Delta\Sigma$  modulators are reviewed and various double-sampling techniques to mitigate the mismatch effects on  $\Delta\Sigma$  modulators are presented in Section 2.2. In Section 2.3, the well-known CIC decimators are reviewed. Issues of power consumption and speed limitations with conventional architectures and their multi-stage variations are discussed. In Section 2.4, we review three all-digital symbol timing recovery techniques. Comparisons among these techniques are given in terms of complexity and DSP computation. Finally, a summary is given in Section 2.5.

#### 2.1 Digital Radio Receiver Architectures

Modern radio receivers have advanced to take advantage of digital techniques. Their architectures are greatly influenced by current VLSI technologies, especially by high speed ADCs, Application Specific Integrated Circuits (ASICs) and DSPs. The key to the

choice of digital receiver architectures is determined by high performance and low power ADCs, DDCs, re-timing circuits, etc. In the following, two kinds of digital receiver architectures are reviewed. They are categorized in terms of where to digitize the received signals, that is, baseband and IF digitization.

#### 2.1.1 Receivers with Baseband Digitization

In baseband-digitization receiver architectures, the Radio Frequency (RF) signals are quadrature-downconverted in several stages to I/Q baseband where digitization occurs. They can be further categorized as superheterodyne and direct-conversion receivers.

#### A. Superheterodyne Receivers

The superheterodyne receiver was introduced by Armstrong in 1918 [Abid95] and has been considered as the radio receiver of choice due to its high selectivity and sensitivity. The idea is to translate the RF signal by several mixing stages down to I/Q baseband signals where the signals are digitized.

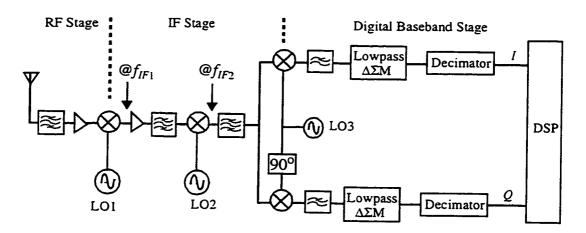

Figure 2.1 A typical superheterodyne receiver with baseband digitization

A typical double-conversion superheterodyne digital radio receiver is depicted in Figure 2.1 [Coy92], [Meyr95]. It is called a baseband-digitization radio receiver. The received RF signal is first filtered and low-noise amplified by a Low Noise Amplifier (LNA). It is then mixed with a variable local oscillator LO1 to an IF signal centered at  $f_{IF1}$ . This IF frequency is fixed for the entire reception band to ensures consistent performance across

- DC offset It results from: (1) I and Q mismatch, (2) LO leakage to the antenna, reflected back to the mixer, (3) a large near-channel interferer and second-order harmonic signals leaking into the LO port of the mixer and self-downconverting to DC.

- 1/f noise This noise in the mixers and amplifiers degrades the SNR.

- high dynamic range for analog front-end (e.g., mixers) high dynamic range due to strong interferers and weak desired signals.

- high Spurious Free Dynamic Range (SFDR) for ADCs channel selectivity is preferably achieved by digital filtering and requires a high SFDR for ADCs to handle strong interferers. SFDR is defined as the ratio of the tone signal power to the peak power of the largest spurious signal in the ADC output spectrum.

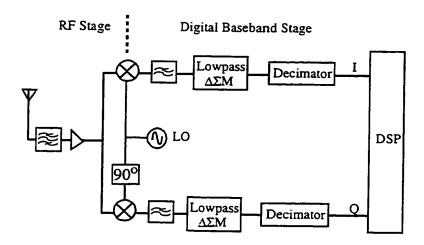

Figure 2.2 A typical direct-conversion receiver

#### 2.1.2 Receivers with IF Digitization

There are some problems with baseband-digitization receiver architectures such as I/Q mismatch, 1/f noise, DC offset, etc. To solve these problems, architectures with IF digitization have been proposed, where the incoming analog signal is digitized at an early stage. The key components in the architecture are high speed ADCs and DDCs. The ADC may be a bandpass  $\Delta\Sigma$  [Thur95] or a wideband Nyquist ADC [Wepm95]. Digital techniques are used extensively to achieve high performance and high integration. The receivers can be further categorized as narrowband and wideband receivers [Mito95], [Thur95].

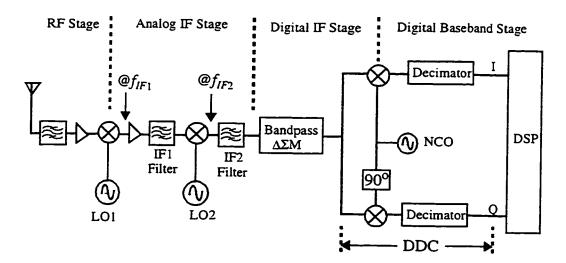

#### A. Narrowband IF-Digitization Receivers

Narrowband IF-digitization receivers shown in Figure 2.3 are designed to demodulate only one frequency channel at one time [Coy92], [Meyr95], [Thur95] and are suitable in a handset design. The bandwidth in a handset device is 200 KHz for GSM in Europe or 30 KHz for IS-54 in North America. Low power consumption is often required (typically below 10 mW).

LO1 is variable and is tuned to the desired band. The first intermediate frequency  $f_{IF1}$  is fixed. A fixed LO2 is used to further downconvert the signal centered at  $f_{IF1}$  to  $f_{IF2}$ . Note that the IF2 filter is often a SAW (surface acoustic wave) filter which does anti-aliasing and help channel selection. The combination of analog filters and digital filters provides the selectivity.

The IF signal at  $f_{IF2}$  is digitized by a bandpass  $\Delta\Sigma$  ADC. A DDC is used to digitally translate the signal at  $f_{IF2}$  into baseband I and Q signals. The DDC consists of a Numerically Controlled Oscillator, digital mixers and decimators as shown in the figure. Decimators downsample the high data rate to Nyquist rate and suppress the unwanted signals (quantization noise and adjacent interferers). The lower-rate digital I and Q signals are then processed by DSP for timing recovery and other functions.

Figure 2.3 A superheterodyne radio receiver with IF digitization

The interferers may be at high levels after the SAW filter but can be removed by subse-

quent high performance digital filters. According to the Nyquist sampling criterion, the sampling rate must be at least twice the signal bandwidth but not its absolute frequency. Therefore, the sampling rate can be lower than  $f_{IF2}$ . The sampling rate  $f_s$  is commonly chosen such that the signal at  $f_{IF2}$  is aliased by the IF sampling process down to a digital IF frequency of  $\frac{1}{4}f_s$  for odd k and  $\frac{3}{4}f_s$  for even k. Hence, the sampling rate should be

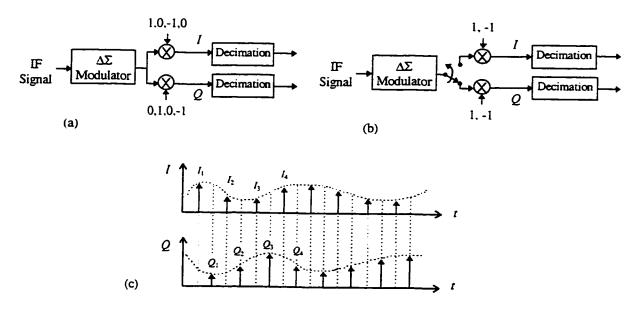

$$f_s = \frac{4f_{IF2}}{2k - 1} \tag{2.1}$$

where k is an integer [Cons83], [Meyr95]. The outputs of the NCO become simple sequences  $\{1,0,-1,0,...\}$  and  $\{0,1,0,-1,...\}$  respectively. The spectrum is phase-reversed when k is even. The simplest implementation is when k = 1 and it relaxes requirements for sampling aperture jitter and IF2 filter. Undersampling occurs when  $k \ge 2$  [Gros91].

The receiver dynamic range will be greatly limited by the SFDR of ADCs. A bandpass  $\Delta\Sigma$  ADC is a good candidate for this application due to its inherent linearity and high SFDR [Schr89], [Thur95]. In Figure 2.3, the ADC may be replaced by a  $\Delta\Sigma$  based frequency discriminator which directly digitizes the phase of the IF2 signal [Bear94]. This approach is suitable for a phase-modulated signal, such as signals using Gaussian Minimum Shift Keying (GMSK) and QPSK modulation.

#### B. Wideband Receivers

The idea of the wideband receiver is to share the common RF / IF front end, including a wideband ADC, to demodulate multiple frequency channels at the same time in the DSP stage. Thus, this architecture is suitable for basestation receivers. Figure 2.4 shows the architecture where all the analog local oscillators (LO1 and LO2) are fixed, and a DDC is used to tune to the desired channel. The ideal wideband receiver should accommodate simultaneously all, or a large fraction, of the downlink band (824~849 MHz and 1850~1910 MHz for North America cellular and PCS, respectively).

Wideband ADCs and low power DDCs are critical in this architecture. The wideband ADC should have a high enough conversion rate (e.g., 65 MHz for a 20 MHz band) and a sufficient SFDR (e.g., > 80 dB for IS-54 in North America [Wepm95]). DDCs may be

SFDR and SNR (> 60 dB, typically 80 dB). Double-sampling SC implementation of a  $\Delta\Sigma$  modulator improves SNR by (6M+3) dB in an  $M^{th}$  order modulator almost for free. However the achievable SNR is limited to < 60 dB by capacitor mismatch. Solutions should be worked out to remove the limitation. In the following section, general  $\Delta\Sigma$  modulation techniques and the state-of-art of double-sampled  $\Delta\Sigma$  modulation techniques are reviewed.

# 2.2.1 Overview of Discrete-Time $\Delta\Sigma$ Modulation

Quantization of amplitude and sampling in discrete time are at the heart of all digital modulators. If the quantization error is treated as white noise having equal probability in the range  $\pm \Delta_q/2$ , its rms value is given by [Cand92],

$$e_{rms} = \frac{\Delta_q}{2\sqrt{3}},\tag{2.2}$$

where  $\Delta_q$  is the quantization level spacing. The spectral density of the quantization noise is given by [Cand92],

$$E(f) = e_{rms} \sqrt{\frac{2}{f_s}}, \ 0 \le f < f_s/2.$$

(2.3)

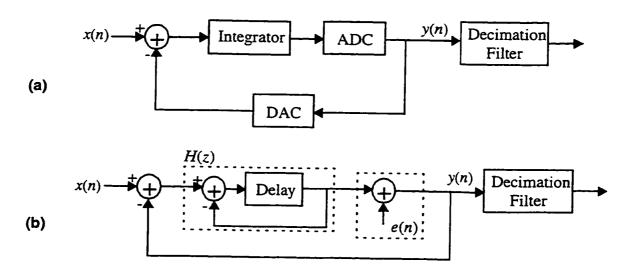

Figure 2.6 (a) A generic delta-sigma ADC and (b) its linear model

A block diagram of a generic  $\Delta\Sigma$  modulator is depicted in Figure 2.6 (a) where x(n) is an analog sampled input and y(n) is the digital output of the  $\Delta\Sigma$  modulator [Cand92], [Aziz96]. The input to the circuit is fed to the quantizer via an integrator, and the quantized output is fed back and subtracted from the input. This feedback forces the average value of the quantized signal to track the average input. Any difference between them accumulates in the integrator and is eventually corrected by feedback. Note that errors in the Digital-to-Analog Converter (DAC) may directly contribute to the output and degrade SNR. Therefore a one-bit quantizer is often preferred in a  $\Delta\Sigma$  modulator. In this implementation, the integrator can be a continuous-time or discrete-time circuit. A SC integrator is widely used in this configuration. The linearized sampled-data model is shown in Figure 2.6 (b), where the integrator has gain H(z) and the white quantization noise is e(n). The output in the z-domain can be expressed as,

$$Y(z) = H_X(z)X(z) + H_E(z)E(z), (2.4)$$

where  $z=e^{j2\pi\,(f/f_s)}$  and  $f_s$  is the sampling rate. The signal and noise transfer functions are given by  $H_X(z)=\frac{H(z)}{1+H(z)}$  and  $H_E(z)=\frac{1}{1+H(z)}$  respectively.

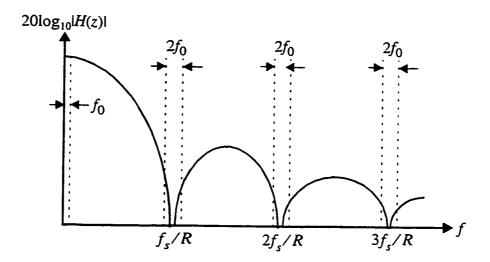

In a lowpass  $\Delta\Sigma$  modulator,  $H_X(z)$  and  $H_E(z)$  are a lowpass (or allpass) filter and a highpass filter respectively. The output quantization noise is shaped by  $H_E(z)$  in such a way that most of the energy resides outside the desired band. A decimator is used to remove the out-of-band noise, downsample the data rate, and increase the word length.

If the integrator in Figure 2.6(b) has gain  $H(z)=z^{-1}/(1-z^{-1})$ , then  $H_X(z)=z^{-1}$  and  $H_E(z)=(1-z^{-1})$ . This is a first-order  $\Delta\Sigma$  modulator. The spectral density of the shaped modulation noise  $N(z)=H_E(z)E(z)=(1-z^{-1})E(z)$  can be expressed as,

$$|N(f)| = |E(f)|(1 - e^{-j2\pi(f/f_s)})| = 2e_{rms}\sqrt{\frac{2}{f_s}}\sin(\frac{\pi f}{f_s})$$

(2.5)

$\Delta\Sigma$  ADC is the ideal candidate for the narrowband IF-digitization radio receiver. A band-pass  $\Delta\Sigma$  ADC has also been demonstrated in an RF-digitization radio receiver [Gao97].  $\Delta\Sigma$  ADCs are popular due to the following facts [Cand92], [Aziz96], [Nors97]:

- they are tolerant of analog component variations and hence can achieve higher resolution and higher linearity (or high SFDR) compared to Nyquist ADCs.

- · they alleviate the tough requirement for an anti-aliasing filter due to oversampling.

- they permit easy integration with other digital CMOS components since they do not require trimming and thus are suitable for standard CMOS VLSI processes.

## 2.2.2 Double-Sampled $\Delta\Sigma$ Modulation

In digital radio, a low power lowpass  $\Delta\Sigma$  ADC in a baseband-digitization receiver is critical and a low power, high speed bandpass  $\Delta\Sigma$  ADC is critical for an IF-digitization receiver, especially for a handset. Power consumption increases linearly with clock rate only up to a critical rate in a CMOS  $\Delta\Sigma$  modulator. Above this rate, power consumption increases quadratically with the clock rate [Malo95]. A general practice for low power would be to keep the clock rate as low as possible.

Parallelism allows a high OSR at a low clock and hence is power efficient in the quadratic case. Several techniques using parallelism have been proposed to reduce power consumption or increase the bandwidth of interest [Hurs90], [Aziz93], [Khoi93], [Galt95]. However, all those techniques suffer SNR loss due to mismatch between signal paths. Double-sampling is one of these techniques and will be focused in this work. We review the state-of-art of mismatch mitigation methods in double-sampled modulators.

# A. Conventional Double-Sampled ΔΣ Modulation

Double-sampling increases the effective sampling rate by a factor of 2 or reduces the clock rate (and the speed requirement for the op-amps) by a factor of 2. Only capacitors and switches are doubled. Double-sampling imposes no extra requirements for the opamps. Hence it is an efficient technique for low power applications. The double-sampled SC circuit for filtering applications was proposed in 1980 [Choi80]. A single-sampled SC circuit samples the input signal in one phase and transfers the charge to the output on another. Hence, it wastes op-amp on one of two phases. A double-sampled SC circuit sam-

ples the input on both phases, therefore doubling the sampling rate. Note that the double sampling is different from an "N-path" technique (N = 2) [Greg86]. In a double-sampled SC circuit, the op-amp is shared on both phases while two op-amps are required in the two-path case and each path has its own op-amp.

In a CMOS analog circuit, the bias current required to get adequate settling increases linearly with clock rate in the weak inversion region and quadratically in the strong inversion region. This is different from  $CV^2f$  formula for the digital circuit which describes saturated switching. Hence, there is a critical rate, above which power consumption increases quadratically [Malo95]. For the quadratic case, a power consumption comparison of three techniques mentioned above is listed in Table 2.1 where  $P_s$  is the power consumption of a single-sampling SC circuit at sampling rate  $f_s$ . As can be seen, double sampling is the most power efficient technique.

| Sampling rate | Single sampling | Two-path | Double sampling   |

|---------------|-----------------|----------|-------------------|

| $f_s$         | $P_s$           | $P_s/2$  | P <sub>s</sub> /4 |

| $2f_s$        | $4P_s$          | $2P_s$   | $P_s$             |

Table 2.1 Power consumption comparison in different SC techniques

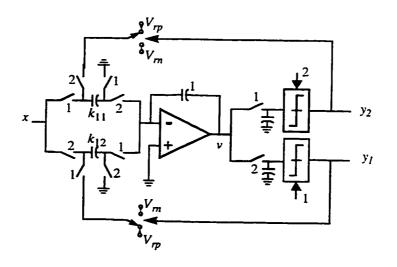

Figure 2.8 A first-order double-sampled SC delta-sigma modulator

with the adding of a pair of capacitors. Three input capacitors are connected to the op-amp during every sample period and hence limit the speed. Additionally, this scheme needs a complex finite state machine (FSM) to generate clocks which are required by the feedback loops. This makes the design more complex and consumes extra power.

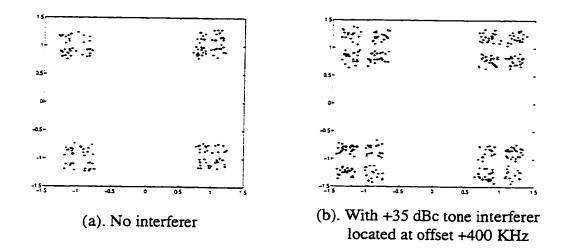

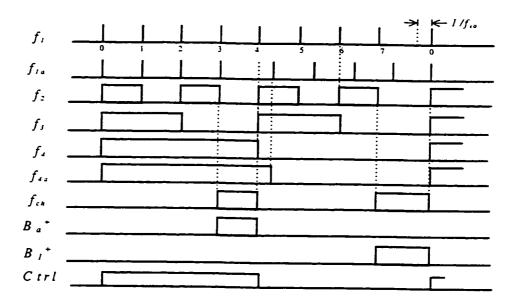

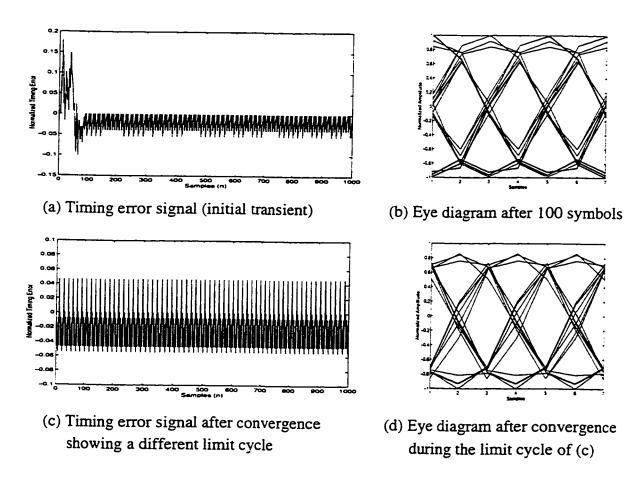

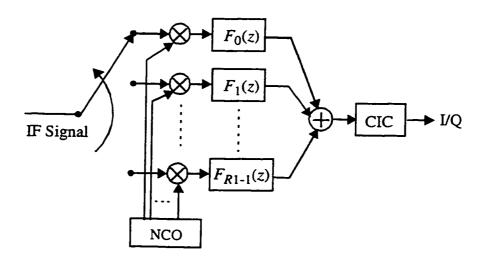

An improvement to the above scheme called individual-level averaging switching scheme was proposed in [Than97]. This method is quite similar to the above scheme. The improvements over the above scheme are: (1) three capacitors connected to the op-amp during every sample period are reduced to two; (2) the FSM circuits are simplified. The drawback of using FSM circuits still has not been eliminated.