Université d'Ottawa • University of Ottawa

# Visual Communications on a

# Memory-Embedded Array Processor:

# The Computational\*RAM

by

Thinh Minh Le, B.A.Sc, M.A.Sc

A thesis submitted to the

School of Graduate Studies and Research

in partial fulfillment of

the requirement for the degree of

**Doctor of Philosophy**

in

Computer Engineering

Ottawa-Carleton Institute of Electrical Engineering

School of Information Technology and Engineering

University of Ottawa

Ottawa, Ontario, Canada

Thinh M. Le, April, 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-79830-5

| I hereby declare that I am the sole author of this thesis.                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------|

| I authorize the University of Ottawa to lend this thesis to other institutions or individuals for the purpose of scholarly research. |

|                                                                                                                                      |

| Thinh M. Le                                                                                                                          |

|                                                                                                                                      |

| I further authorize the University of Ottawa to reproduce this thesis by photocopying or other                                       |

| means, in total or in part, at the request of other institutions or individuals for the purpose or                                   |

| scholarly research.                                                                                                                  |

|                                                                                                                                      |

Thinh M. Le

The University of Ottawa requires the signatures of all persons using or photocopying this thesis. Please sign and date below with your email and postal addresses.

### **Abstract**

In this thesis, image and video processing algorithms, especially the compression algorithms, are first studied in their natural formats to appreciate the needs for real-time operations and hence, parallel computing. The computational intense, memory-bound problems are next approached from two directions: algorithmic and architectural. Algorithmic approach tends to systematically analyze the flow independence and data independence of a program, while architectural approach tends to gain speed-up by resource multiplicity and time sharing.

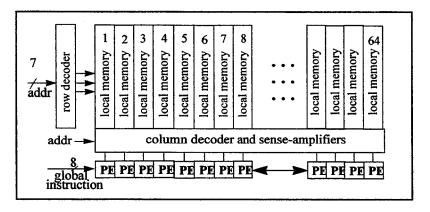

The majority of image and video processing algorithms are inherently data-parallel in nature. The vectorization of these algorithms requires consistent practices, and new challenge in parallel programming seems endless. The data-parallel nature of image/video processing algorithms map well onto the Single-Instruction stream, Multiple-Data stream (SIMD) of an increasingly popular Memory-Embedded Array Processor classified as the Intelligent RAMs, specifically, the Computational\*RAM (C\*RAM). C\*RAM is a SIMD-memory hybrid where the processing elements are pitch-matched to memory columns of a conventional computer RAM at the sense-amplifiers to take advantage of the inherently high memory bandwidth, and the emulation of the massively parallel processors.

Throughout the thesis, speed-ups from 1 to 3 orders of magnitude are obtained. Memory-bound algorithms such as Motion Estimation, and Mean-Absolute-Error for Nearest Neighbor Distortion Computation are among the most efficient implementations.

At its best, this thesis will, definitely, put forward the promising research direction which involves fast and efficient in-memory parallel computing for visual communications.

# Acknowledgements

First of all, I would like to thank Professor Sethuraman Panchanathan, formerly with the University of Ottawa, at the Arizona State University for his continuous supervision and encouragement. I am also grateful of Professor Ralph Mason and Professor Martin Snelgrove at Carleton University for their advice, guidance, and support. I also thank my colleague, Peter Nyasulu, for his cooperation throughout my research.

This work was made possible by the earlier supports from Microelectronics Network (MicroNet) under the Network Centers of Excellence (NCE) program of the Government of Canada, the School of Graduate Studies and Research and the School of Information Technology and Engineering (SITE) at the University of Ottawa.

My appreciation are also to Professor Tet Yeap for his valuable comments which have helped in the progress of this thesis; and the staffs: Ms. Lucette Lepage of SITE, and Mr. Nagui Mikhail of the Department of Electronics, Carleton University.

Finally, I would like to thank my parents, my family, and my loving fiancee for their continuous encouragement and understanding. It would not have been possible to accomplish this innovative and rewarding work without their love and supports.

# **Table of Contents**

| CHAP               | TER 1 Introduction                                                                |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------|--|--|--|--|

| 1.1 T              | nesis outline                                                                     |  |  |  |  |

| 1.2 T              | nesis contributions                                                               |  |  |  |  |

| CHAP               | TER 2 Overview of Image and Video Processing Algorithms and Compression Standards |  |  |  |  |

| 2.1 In             | nage Color Components                                                             |  |  |  |  |

| 2.2 G              | eneral Image Processing Techniques                                                |  |  |  |  |

| 2.2.1              | Bit Extraction                                                                    |  |  |  |  |

| 2.2.2              | Contrast Stretching, Clipping, and Thresholding14                                 |  |  |  |  |

| 2.2.3              | Image Subtraction                                                                 |  |  |  |  |

| 2.2.4              | Convolution                                                                       |  |  |  |  |

| 2.3 In             | nage Processing using Mathematical Morphology                                     |  |  |  |  |

| 2.3.1              | Erosion and Dilation                                                              |  |  |  |  |

| 2.3.2              | Opening and Closing                                                               |  |  |  |  |

| 2.3.3              | 2.3.3 Morphological Gradients                                                     |  |  |  |  |

| 2.3.4              | Edge Detection                                                                    |  |  |  |  |

| 2.4 D              | ata Compression Techniques                                                        |  |  |  |  |

| 2.5 S <sub>1</sub> | patial-Domain Compression Techniques                                              |  |  |  |  |

| 2.5.1              | Predictive Coding                                                                 |  |  |  |  |

| 2.5.2              | Run Length Coding (RLC)                                                           |  |  |  |  |

| 2.5.3              | Discrete Cosine Transform (DCT)                                                   |  |  |  |  |

| 2.6 To             | emporal-Domain Compression Techniques                                             |  |  |  |  |

| 2.6.1              | Interframe Transform Coding                                                       |  |  |  |  |

| 2.6.2              | Conditional Replenishment                                                         |  |  |  |  |

| 2.6.3              | Motion Estimation                                                                 |  |  |  |  |

|                    | Group 1: Reduction in the number of search locations                              |  |  |  |  |

|                    | Group 2: Reduction in the number of pixels involved                               |  |  |  |  |

|                    | Group 3: Reduction in the bit-depth of the pixel                                  |  |  |  |  |

| 2.7 V              | ector Quantization                                                                |  |  |  |  |

| 2.7.1              | Vector Formation                                                                  |  |  |  |  |

| 2.7.2   | Codebook Generation                                           | 39         |

|---------|---------------------------------------------------------------|------------|

| 2.7.3   | Quantization                                                  | 39         |

| 2.7.4   | Vector Quantization for Temporal Compression                  | 40         |

| 2.8 Im  | age and Video Compression Standards                           | 41         |

| 2.8.1   | The JPEG Image Compression Standard [ISO/IEC 10918-1]         | 41         |

| 2.8.2   | The MPEG Video Compression Standards                          |            |

|         | MPEG-1 [ISO/IEC 11172]                                        |            |

|         | MPEG-2 [ISO/IEC 1318-2]                                       |            |

|         | MPEG-4                                                        |            |

| 2.8.3   | The Teleconferencing Video Compression Standards              |            |

|         | H.263 standard [ITU-T rec. H.263]                             |            |

| 20 50   | mmary                                                         |            |

| 2.9 Su  | innary                                                        | <i>3</i> 1 |

| CHAP    | TER 3 C*RAMs and Other Logic-in-Memory SIMD Designs: A Review | 52         |

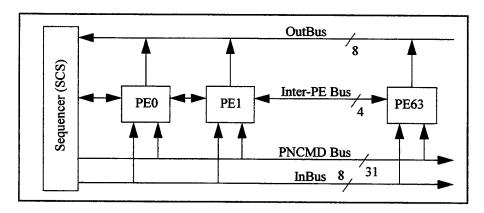

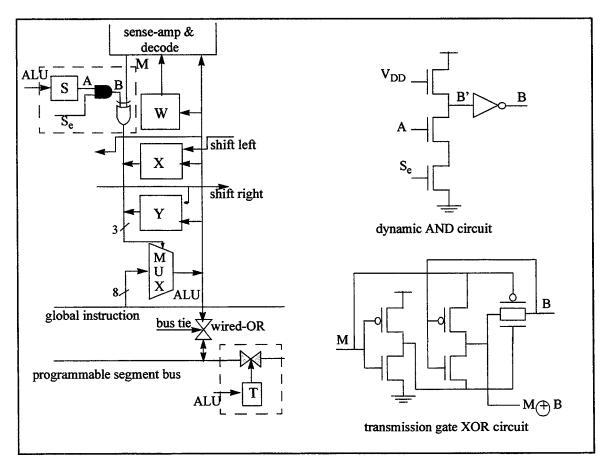

| 3.1 C*  | RAM (C*RAM92) [Elliott92]                                     | 53         |

| 3.2 Int | tegrated Memory Array Processor (IMAP94) [Yamashita94]        | 57         |

| 3.3 PC  | C-RAM [Cojocaru94]                                            | 58         |

| 3.4 SR  | C-PIM [Gokhale95]                                             | 60         |

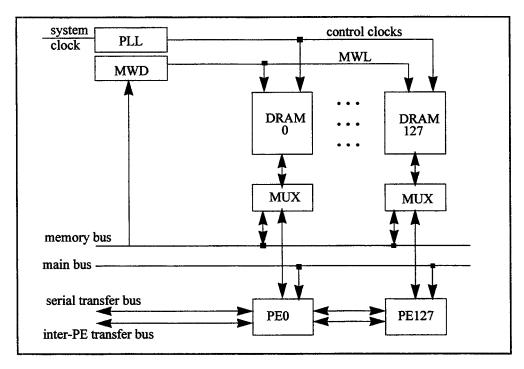

| 3.5 CN  | NAPS [Hammerstrom96]                                          | 61         |

| 3.6 EX  | KECUBE [Sunaga96]                                             | 62         |

| 3.7 Pa  | rallel Image Processing RAM (PIP-RAM) [Aimoto96]              | 63         |

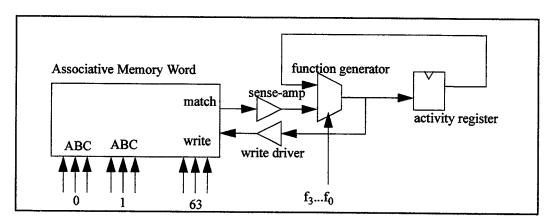

| 3.8 CA  | APP/HDPP [Gealow96]                                           | 64         |

| 3.9 Su  | mmary of Features                                             | 66         |

| CHAP    | TER 4 Proposed Enhancements to C*RAM and Its Instruction Set  | 70         |

| 4.1 Co  | ontributions to C*RAM Architecture                            | 71         |

| 4.1.1   | Parallel Addition / Subtraction Circuits                      | 71         |

|         | Programmable Segment Bus-tie (PSB)                            |            |

| 4.2 VI  | HDL Models                                                    | 76         |

| 4.3 Pro | ogramming Framework                                           | 78         |

| 4.4 C*  | RAM Assembler                                                 | 79         |

| 4.4.1  | Overview of C*RAM Cycles                                                                                     |

|--------|--------------------------------------------------------------------------------------------------------------|

| 4.4.2  | Data Format                                                                                                  |

| 4.4.3  | Instruction Derivation for an User-Defined Operation: An Example                                             |

| 4.4.4  | C*RAM Instructions                                                                                           |

| 4.5 C* | RAM Macros                                                                                                   |

| 4.5.1  | Design of the Assembler to Machine Code Translator                                                           |

| 4.6 Co | onclusions                                                                                                   |

| СНАР   | TER 5 C*RAM Implementations of Image Processing Algorithms                                                   |

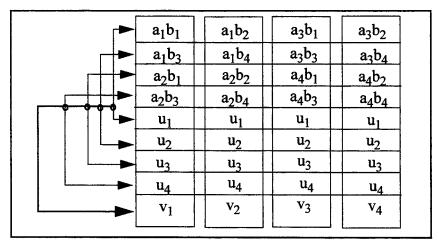

| 5.1 Im | nage Data Arrangement                                                                                        |

| 5.2 Ge | eneral/Morphological Image Processing Techniques90                                                           |

| 5.2.1  | Sub-pixel Operations                                                                                         |

| 5.2.2  | Row-wide Minimum / Maximum Search92                                                                          |

| 5.2.3  | Contrast Stretching, Clipping, and Thresholding92                                                            |

| 5.2.4  | Image Subtraction93                                                                                          |

| 5.2.5  | Filtering                                                                                                    |

|        | Edge Detection Filters                                                                                       |

| 5.2.6  | Performance Comparisons                                                                                      |

| 5.3 D  | CT99                                                                                                         |

| 5.3.1  | General Considerations                                                                                       |

| 5.3.2  | Implementation of Lee's Algorithm [Lee84]99Precision102The n x n Configuration104The 1 x n² Configuration104 |

| 5.3.3  | Implementation of Cho's algorithm [Cho91]                                                                    |

| 5.3.4  | Implementations on the Enhanced C*RAM                                                                        |

| 5.3.5  | Memory Requirements                                                                                          |

| 5.3.6  | Summary of DCT Implementations                                                                               |

| 5.4 E  | ntropy Coding                                                                                                |

| 5.4.1  | Differential Coding of Quantized DC Coefficients                                                             |

| 5.4.2  | Run-Length Coding of Zig-Zag Scanned, Quantized AC Coefficients                                              |

| 5.4.3  | Variable-Length Coding for Run-Length Coded Coefficients                            | 111           |

|--------|-------------------------------------------------------------------------------------|---------------|

| 5.5 St | ub-Codebook VQ for Image Compression                                                | 111           |

| 5.5.1  | Implementation Procedure                                                            | 112           |

| 5.5.2  | Coding Performances                                                                 | 113           |

| 5.5.3  | Theoretical Speed-up Analysis                                                       | 119           |

| 5.5.4  | Experimental Speed-ups                                                              |               |

| 5.6 C  | onclusions                                                                          | 120           |

| CHAP   | TER 6 A New Low-Complexity Motion Estimation Algorithm and Its C*RAM Implementation | 122           |

| 6.1 M  | Iotion Estimation using Feature Extraction and XOR Operation                        | 122           |

| 6.1.1  | Description of the Algorithm                                                        | 125           |

| 6.1.2  | Simulation Results                                                                  | 125           |

| 6.1.3  | Implementation of Dynamic Thresholding                                              | 129           |

| 6.1.4  | Speed-up Analysis                                                                   | 130           |

| 6.2 C  | *RAM Implementation of ME Algorithms                                                | . 132         |

| 6.2.1  | Data Arrangement  Maximum Transfer Distance  Control Complexity                     | . 133         |

|        | PE Utilization                                                                      |               |

| 6.2.2  | Memory Requirement.                                                                 |               |

| 6.2.3  | C*RAM's Implementation of a Single MAE Computation                                  |               |

| 6.2.4  | Implementation of FBMA                                                              |               |

| 6.2.5  | The TSS Algorithm                                                                   | . 142         |

| 6.2.6  | Implementation of Pixel Decimation                                                  | . 143         |

| 6.2.7  | Implementation of FEXOR                                                             | . 144         |

| 6.2.8  | Implementation of BP-BPM                                                            | . 145         |

| 6.2.9  | Comments on Different ME Algorithms                                                 | . 146         |

| 6.3 C  | onclusions                                                                          | . 149         |

| CHAI   | PTER 7 C*RAM Implementations of Image and Video Compression Standards               | . 150         |

| 7.1 In | mplementations of the JPEG Image Compression Standard                               | . 151         |

| 7.1.1  | JPEG Baseline Compression                                                           |               |

| 7.1.2  | JPEG Lossless Compression                                                           |               |

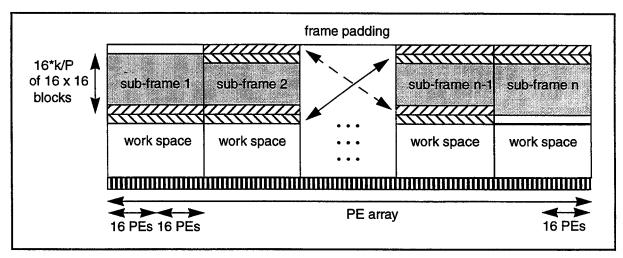

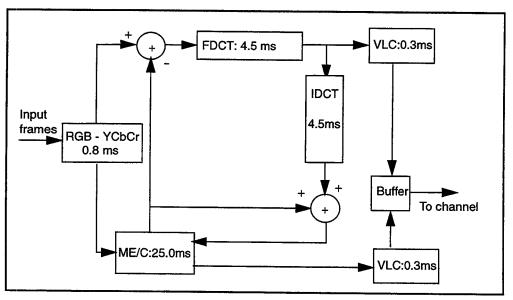

| 72 C   | *RAM Model for Video Compression                                                    | . 15 <i>6</i> |

| 7.2.1 Design Equations                                                 | 157 |

|------------------------------------------------------------------------|-----|

| Memory Requirement and the Number of PEs in a C*RAM                    | 158 |

| Computation of I/O Time                                                |     |

| Computation of Padding Time                                            |     |

| Adjustment to Block DCT Time                                           |     |

| Adjustment to Block VLC Time                                           |     |

| Adjustment to Block ME Time                                            |     |

| 7.2.2 Simulation Results and Performance Analysis                      |     |

| Implementation of H.261                                                |     |

| -                                                                      |     |

| 7.3 Improvements to Existing C*RAM Architecture for Better Performance | 167 |

| 7.4 Conclusions                                                        | 168 |

| CHAPTER 8 Conclusions and Future Work                                  | 170 |

| 8.1 Conclusions                                                        | 171 |

|                                                                        |     |

| 8.2 Future Work                                                        | 1/2 |

| BIBLIOGRAPHY                                                           | 173 |

| APPENDIX A Other Image Compression Issues                              | 184 |

| A.1 Data Compression Techniques                                        | 184 |

| A.1.1 Lossless Compression                                             | 184 |

| A.1.2 Lossy Compression                                                |     |

| A.2 Objective Measures                                                 | 186 |

| A.3 Codebook Generation in Vector Quantization                         |     |

| A.4 Edge Detection/Enhancement Techniques                              | 189 |

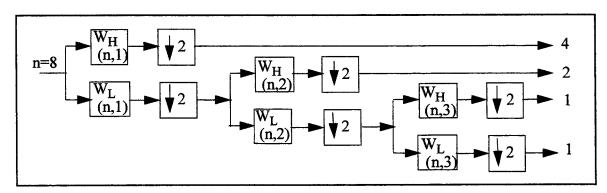

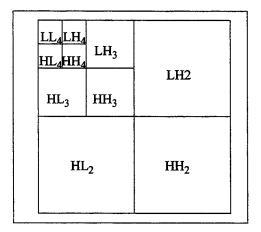

| A.5 Discrete Wavelet Transform (DWT)                                   | 189 |

| APPENDIX B Matrix Multiplication using C*RAM                           | 193 |

| B.1 Image Transformation Implemented on a SIMD architecture            |     |

| APPENDIX C Program Listings                                            | 195 |

| C.1 VHDL Files                                                         |     |

|                                                                        |     |

| C.2 Test Files for VHDL models                                         |     |

# List of Figures

| Figure 1.1  | Some examples of parallel image and video processing                  |

|-------------|-----------------------------------------------------------------------|

| Figure 2.1  | Contrast stretching                                                   |

| Figure 2.2  | Erosions and Dilations with different structuring elements B and D 19 |

| Figure 2.3  | Internal and External Gradients using structure elements B and D 21   |

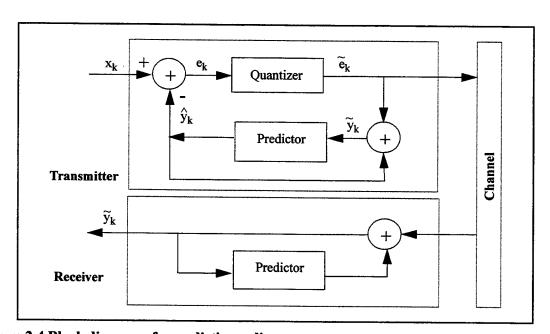

| Figure 2.4  | Block diagram of a predictive coding system                           |

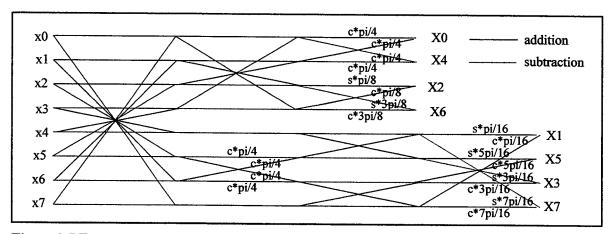

| Figure 2.5  | Forward DCT flow graph for N=8, Ci = cos i, Si = sin i [Chen77]       |

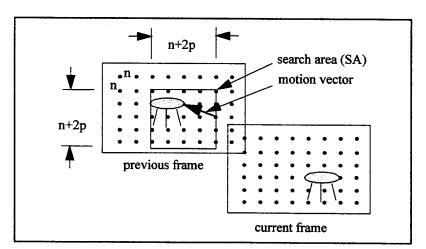

| Figure 2.6  | Block matching process                                                |

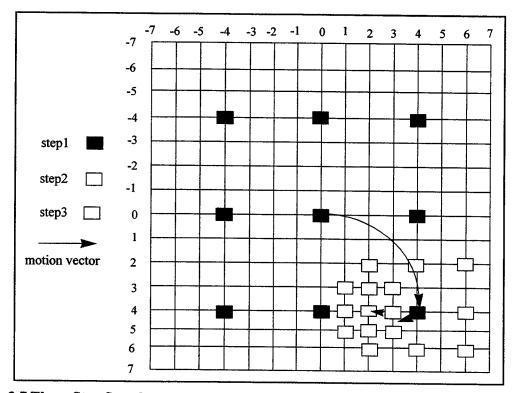

| Figure 2.7  | Three-Step Search                                                     |

| Figure 2.8  | Simple and Efficient Search                                           |

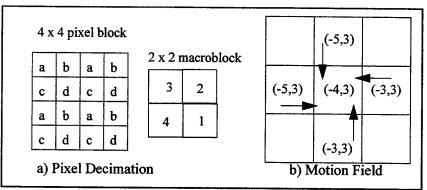

| Figure 2.9  | Pixel Decimation and Motion Field                                     |

| Figure 2.10 | VQ for Image Compression                                              |

| Figure 2.11 | JPEG Baseline Sequential Mode                                         |

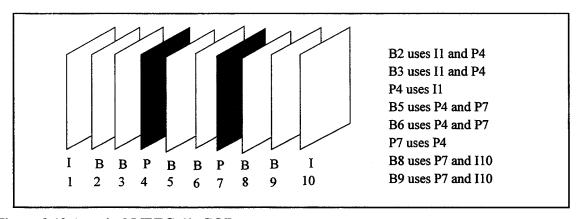

| Figure 2.12 | A typical MPEG-1's GOP                                                |

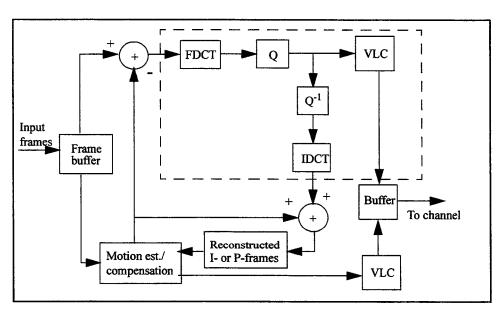

| Figure 2.13 | Block diagram of MPEG-1 encoder                                       |

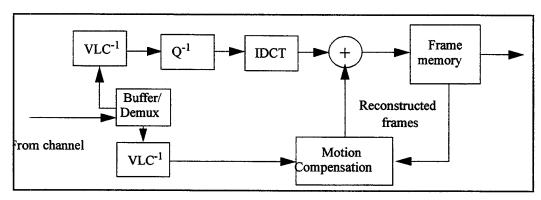

| Figure 2.14 | Block diagram of MPEG-1 decoder                                       |

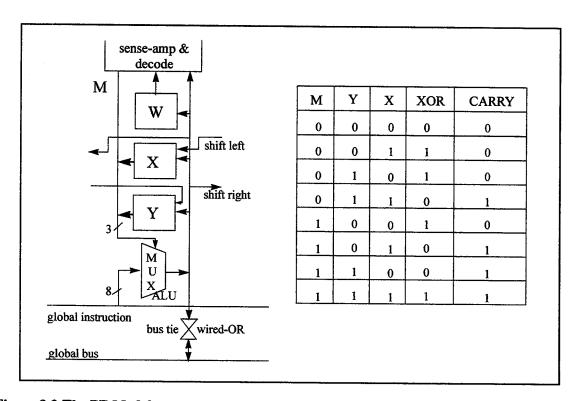

| Figure 3.1  | C*RAM Architecture                                                    |

| Figure 3.2  | The PE Model                                                          |

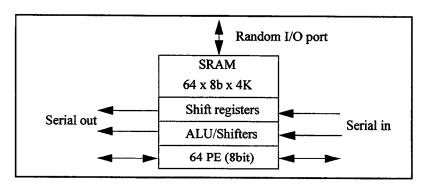

| Figure 3.3  | Integrated Memory Array Processor 57                                  |

| Figure 3.4  | The Extended PE Model                                                 |

| Figure 3.5  | A PIM Processor                                                       |

| Figure 3.6  | CNAPS Architecture                                                    |

| Figure 3.7  | PIP-RAM Architecture                                                  |

| Figure 3.8  | Associative PE of the CAPP65                                          |

| Figure 3.9  | The PE of the HDPP                                                    |

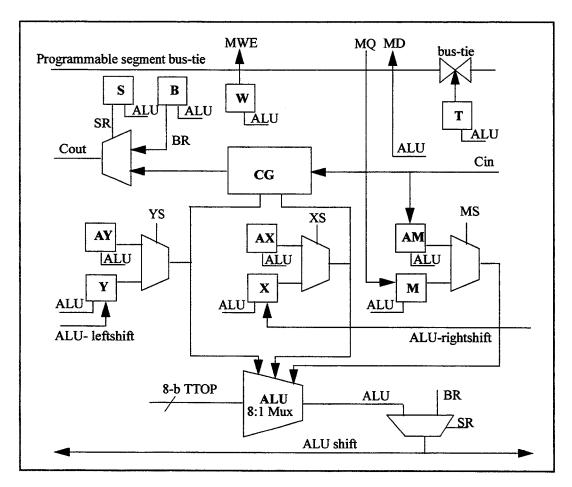

| Figure 4.1  | Enhanced features added to the baseline PE                            |

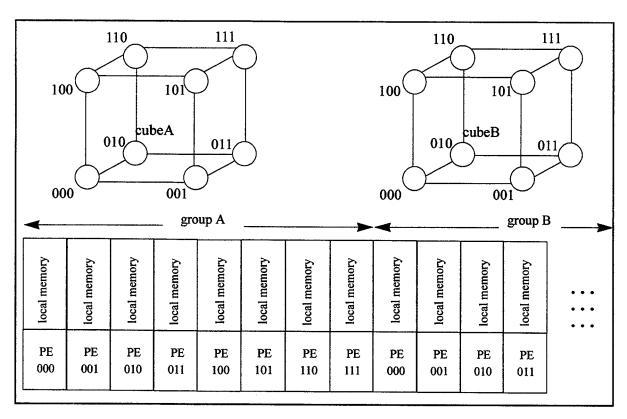

| Figure 4.2  | Multiple Hypercube, realized by enhanced PE with PSB                  |

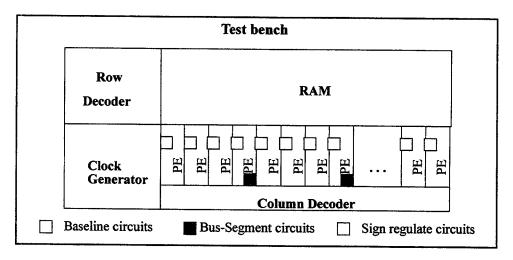

| Figure 4.3  | VHDL model for C*RAM with image/video-enhanced circuits               |

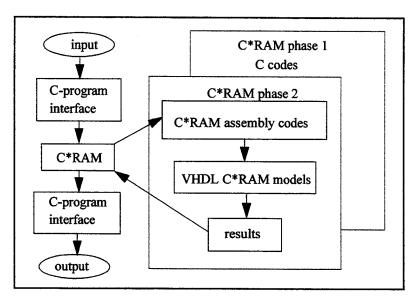

| Figure 4.4  | Phase 1: C-program model; phase 2: C*RAM VHDL model                                 |

|-------------|-------------------------------------------------------------------------------------|

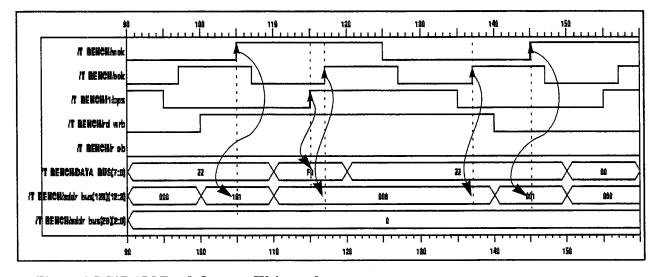

| Figure 4.5  | C*RAM Read-Operate-Write cycle                                                      |

| Figure 4.6  | Derivation of GRE instruction                                                       |

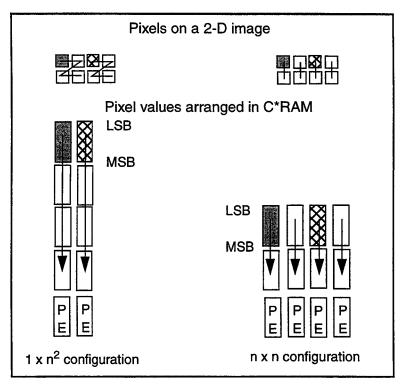

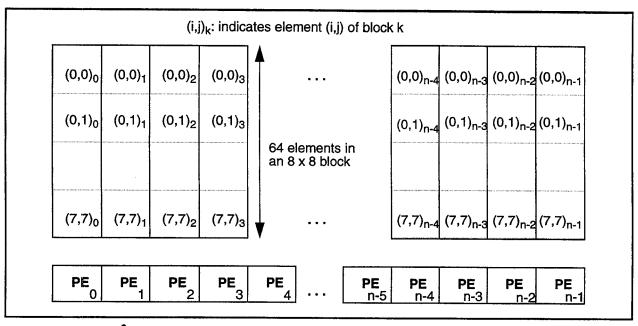

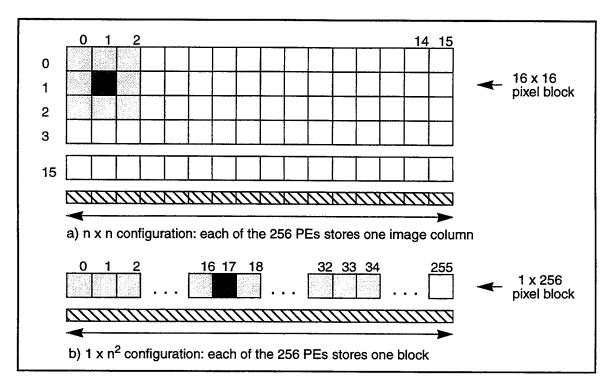

| Figure 5.1  | Two configurations for data arrangement in C*RAM 90                                 |

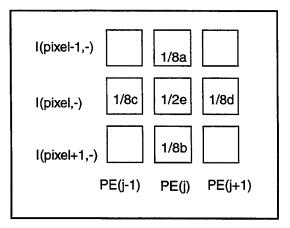

| Figure 5.2  | Spatial Averaging                                                                   |

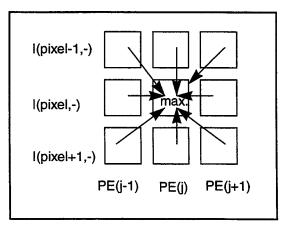

| Figure 5.3  | Morphological dilation                                                              |

| Figure 5.4  | Original 256 x 256 Airplane image                                                   |

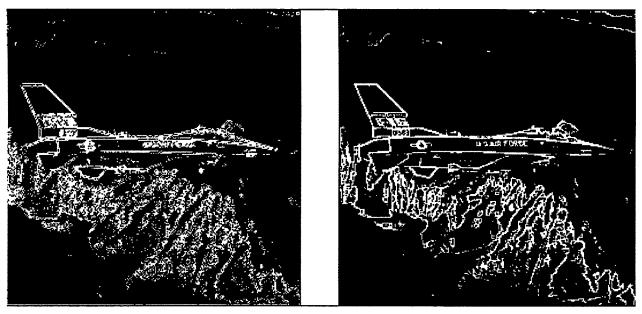

| Figure 5.5  | Edge detection using a) Spatial average filtering, and b) Morph. Ext. Gradient . 97 |

| Figure 5.6  | 1 x n <sup>2</sup> block data arrangement for DCT computation                       |

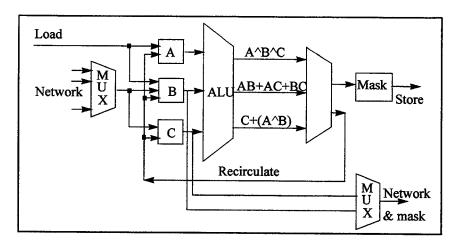

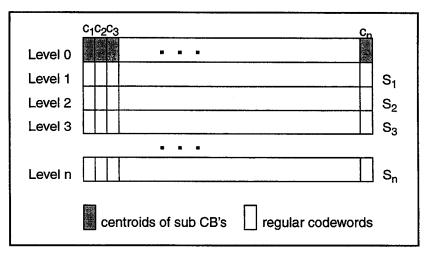

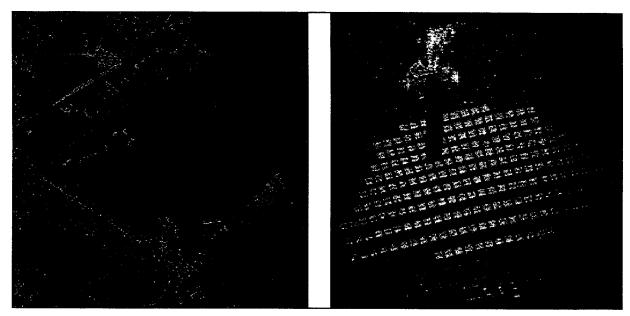

| Figure 5.7  | SCVQ for large codebook allocation                                                  |

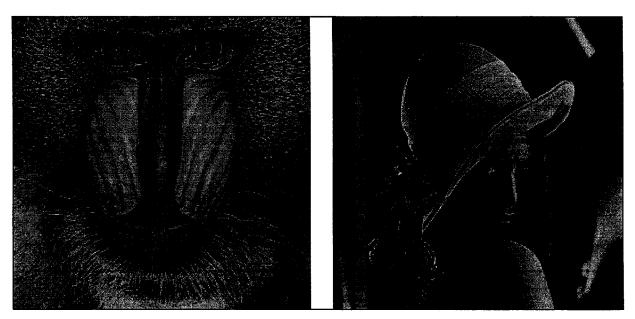

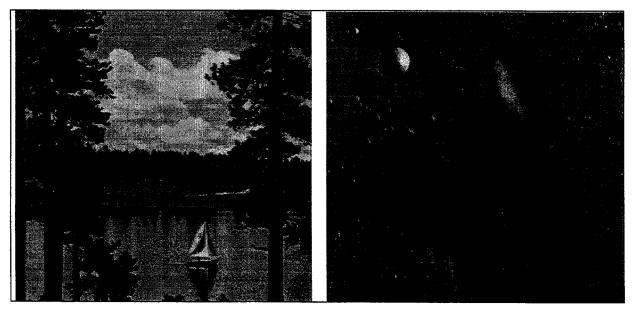

| Figure 5.8  | Original a) Baboon and b) Lena images of size 256 x 256 pixels                      |

| Figure 5.9  | SCVQ with boundary consideration                                                    |

| Figure 5.10 | Original a) Airport and b) Ptower images of size 256 x 256 pixels 117               |

| Figure 5.11 | Original a) Sailboat and b) Moon images of size 256 x 256 pixels 117                |

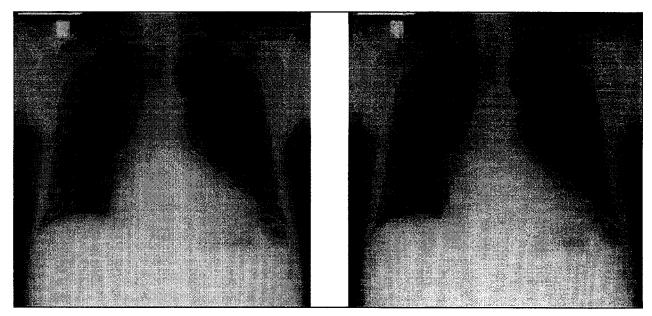

| Figure 5.12 | a) Original 256 x 256 Chest image and b) Its recons. using 512-word FSVQ 118        |

| Figure 5.13 | Reconstructed Chest image using 512-word a) SCVQb and b) TSVQ 118                   |

| Figure 6.1  | Original frame 12 of Pingpong sequence                                              |

| Figure 6.2  | Binary frame 12 generated using BP_BPM                                              |

| Figure 6.3  | Binary frame 12 generated using Lee's filter                                        |

| Figure 6.4  | Binary frame 12 generated using FEXOR                                               |

| Figure 6.5  | Binary frame 12 generated using dynamic thresholding FEXOR                          |

| Figure 6.6  | Image data arrangements                                                             |

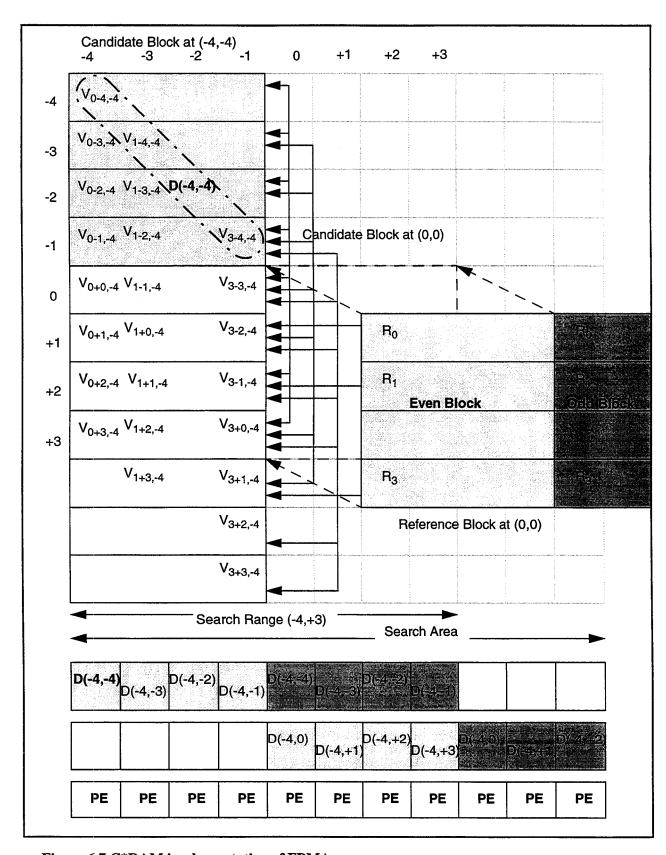

| Figure 6.7  | C*RAM implementation of FBMA                                                        |

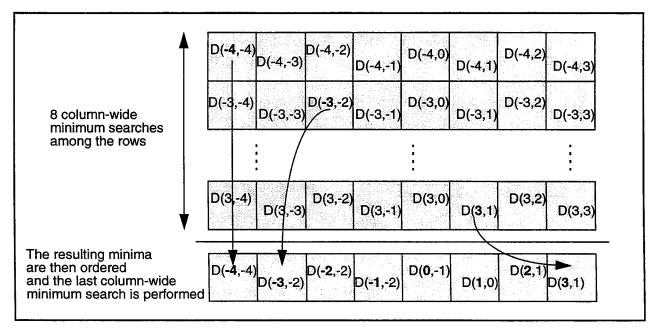

| Figure 6.8  | Column-wide minimum search using PSB                                                |

| Figure 7.1  | Prediction window in lossless mode                                                  |

| Figure 7.2  | Partition of frame data for C*RAM processing                                        |

| Figure 7.3  | Computing load of a C*RAM-based video encoder                                       |

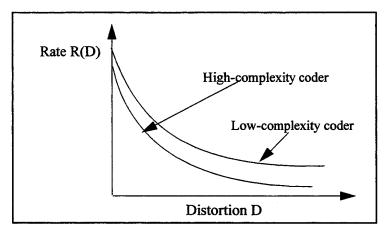

| Figure A.1  | Rate distortion curves and typical encoder performance                              |

| Figure B.1  | Image Transformation implemented on a SIMD architecture 194                         |

# List of Tables

| Table 2.1  | Level-shifting on 8-b pixels                                                                            |  |  |

|------------|---------------------------------------------------------------------------------------------------------|--|--|

| Table 2.2  | CCIR 601 and MPEG frame characteristics                                                                 |  |  |

| Table 3.1  | Feature Summary of logic-in-memory SIMD designs                                                         |  |  |

| Table 4.1  | C*RAM standard and user-defined instructions                                                            |  |  |

| Table 4.2  | C*RAM macros                                                                                            |  |  |

| Table 5.1  | Performance comparison of image processing operations with a RISC (ms) 98                               |  |  |

| Table 5.2  | Comparisons in spatial average filter operation (ms)                                                    |  |  |

| Table 5.3  | Common multiplicative constants in scaled binary representations                                        |  |  |

| Table 5.4  | Block DCT and quantization times using Lee's algorithm                                                  |  |  |

| Table 5.5  | Block DCT and quantization times using Cho's algorithm 107                                              |  |  |

| Table 5.6  | Block DCT and quantization times using n x n configuration                                              |  |  |

| Table 5.7  | Block DCT (ms) using different algorithms on various configurations 108                                 |  |  |

| Table 5.8  | C*RAM speed-ups in block DCT over a RISC processor using different algorithms on various configurations |  |  |

| Table 5.9  | Block execution times (ms) for DC differential and AC run-length codings 110                            |  |  |

| Table 5.10 | Performance of FSVQ vs. SCVQ                                                                            |  |  |

| Table 5.11 | Performance comparison: SCVQ without versus with border consideration 115                               |  |  |

| Table 5.12 | Performance comparison: FSVQ vs. TSVQ vs. SCVQb                                                         |  |  |

| Table 5.13 | Block VQ times and the corresponding speed-ups                                                          |  |  |

| Table 6.1  | Average NMSE (%) of the tested sequences                                                                |  |  |

| Table 6.2  | Average entropies (bpp) of the error frames                                                             |  |  |

| Table 6.3  | Average NMSE (%) over 30 frames using dynamic FEXOR                                                     |  |  |

| Table 6.4  | Block MAE time per 256-D vector                                                                         |  |  |

| Table 6.5  | Minimum search times (ns)                                                                       |  |  |

|------------|-------------------------------------------------------------------------------------------------|--|--|

| Table 6.6  | Motion vector map: an example                                                                   |  |  |

| Table 6.7  | Block ME times using FBMA (ms)                                                                  |  |  |

| Table 6.8  | Block ME times using PD (ms)                                                                    |  |  |

| Table 6.9  | Block ME times using FEXOR (ms)                                                                 |  |  |

| Table 6.10 | Block ME time using BP_BPM (ms)146                                                              |  |  |

| Table 6.11 | Block ME times on the baseline C*RAM (ms)                                                       |  |  |

| Table 6.12 | Block ME times among C*RAM designs and data configurations 147                                  |  |  |

| Table 6.13 | C*RAM speed-ups in block ME times over a RISC processor using FBMA on both C*RAM versions       |  |  |

| Table 7.1  | C*RAM intraframe execution time for grayscale frames (ms)                                       |  |  |

| Table 7.2  | Grayscale baseline JPEG: C*RAM speed-ups over RISC                                              |  |  |

| Table 7.3  | JPEG intraframe execution times for color frames (ms)                                           |  |  |

| Table 7.4  | Color baseline JPEG: C*RAM speed-ups over RISC using 154                                        |  |  |

| Table 7.5  | JPEG lossless execution times (ms)                                                              |  |  |

| Table 7.6  | Lossless JPEG: C*RAM speed-ups over RISC                                                        |  |  |

| Table 7.7  | Optimal no. of PEs and the sizes of their local memories for various video compression profiles |  |  |

| Table 7.8  | H.261 frame processing time (ms)                                                                |  |  |

| Table 7.9  | H.261 simulations: C*RAM speed-ups over RISC                                                    |  |  |

| Table 7.10 | MPEG-2 MP@ML frame processing times                                                             |  |  |

| Table 7.11 | 28-frame timing window using C*RAM (ms)                                                         |  |  |

| Table 7.12 | MPEG-2 MP@MP simulations: C*RAM speed-ups over RISC 166                                         |  |  |

### List of Abbreviations

ALU: Arithmetic Logic Unit

AIS: Applied Intelligent System

ASCII: American National Standard Code for Information Exchange

ASIC: Application Specific Integrated Circuit

AVO: Audio-Video Object

BiCMOS: Bipolar Complementary Metal-Oxide Semiconductor

BMA: Block Matching Algorithm

BPM: Bit Plane Matching

BP-BPM: Band-Pass Bit Plane Matching

bpp: bit per pixel

BSP: Burroughs Scientific Processor

CAM: Content-Addressable Memory

CAPP: Content Addressable Parallel Processors

**CBR:** Constant Bit Rate

CCIR: The International Radio Consultative Committee of the International Telecommunications Union (now ITU-R)

CCITT: Consultative Committee on International Telephony and Telegraphy

CG: Carry Generator

CIF: Common Intermediate Format

CIS: Canadian Ice Services

**CRT**: Cathode Ray Tube

CM: Connection Machine

CMOS: Complementary Metal-Oxide Semiconductor

COP: Control Op-code

CPU: Central Processing Unit

CR: Codebook Replenishment

C\*RAM: Computational Random Access Memory

CU: Computing Unit, sometimes refers to a PE in the 1 x n<sup>2</sup> configuration, and a group of 8 PEs

in the n x n configuration

CW: Codeword

DAP: Distributed-memory Array Processor

DCT: Discrete Cosine Transform

DFP: Differential Frame Prediction

**DMA: Direct Memory Access**

DPCM: Differential Pulse Code Modulation

DRAM: Dynamic Random Access Memory

DSP: Digital Signal Processing / Digital Signal Processor

FCC: Federal Committee on Communications

FEXOR: Feature Extraction and eXclusive OR.

FFT: Fast Fourier Transform

FIR: Finite Impulse Response

FPGA: Field Programmable Gate Array

fps: frame per second

FSVQ: Full-search VQ

GIPS: Giga Instructions per Second

GOP: Group Of Pictures

HDPP: High Density Parallel Processors

HDTV-GA: High Definition TeleVision - Grand Alliance

HVS: Human Visual System

HW: hardware

IBM: International Business Machine Corp.

**IDCT: Inverse Discrete Cosine Transform**

IEC: International Electrotechnical Commission

**IMAP: Integrated Memory Array Processor**

I/O: Input - Output

IRAM: Intelligent RAM

ISDN: Integrated Services Digital Network

ISO: International Standards Organization

ITS: Ice Tracking System

ITU-T: International Telecommunications Union - Telecommunication Standards Sector

JEDEC: Joint Electron Devices Engineering Council

JPEG: Joint Photographic Experts Group

KBps: Kilo Bytes per second

Kbps: Kilo bits per second

LBG (algorithm): Y. Linde, A. Buzo, and R. M. Gray's algorithm

LR: Label Replenishment

LSB: Least Significant Bit

MAE: Mean Absolute Error

Mb: Mega-bits

MB: Mega-bytes

Mbps: Mega-bits per second

MCVQ: Multiple Codebook Vector Quantization

MD: Maximum Descent

ME/C: Motion Estimation/ Compensation

MEG: Morphological External Gradient

MIG: Morphological Internal Gradient

MIP: Morphological Image Processing

MIMD: Multiple-Instruction stream, Multiple-Data stream

MISD: Multiple-Instruction stream, Single-Data stream

MOS: Mean Opinion Score, also Metal-Oxide Semiconductor

MOPS: Million Operations per second

MPEG: Moving Picture Experts Group

MPP: Massively Parallel Processor

MSB: Most Significant Bit

MSE: Mean Square Error

MU: Memory Unit

NMSE: Normalized Mean Square Error

NTSC: National Television System Committee

PC: IBM-compatible Personal Computer

PCB: Printed-Circuit Board

PD: Pixel Decimation, also Pixel Distortion

PDC: Pixel Difference Classification

PE: Processing Element

PIP-RAM: Parallel Image Processing Random Access Memory

PIT: Progressive Image Transmission

PNN: Pairwise Nearest Neighbor

PPM: Portable Pixel Map

PSNR: Peak Signal-to-Noise Ratio

PSB: Programmable Segment Bus-Tie

PWB: Programmable Word Boundary

QCIF: Quarter CIF

**RAM: Random Access Memory**

**RISC: Reduced Instruction-Set Computer**

RLC: Run-Length Coding

**ROM: Read-only Memory**

SA: Search Area

SCVQ: Sub-Codebook Vector Quantization

SIF: Source Input Format

SIMD: Single-Instruction stream, Multiple-Data stream

SIMM: Single Inline Memory Module

SISD: Single-Instruction stream, Single-Data stream

SNR: Signal-to-Noise Ratio

SRAM: Static RAM

SRC-PIM: Supercomputing Research Center Processor-in-Memory

SW: software

TSVQ: Tree Search VQ

TTOP: Truth Table Op-code

VBR: Variable Bit Rate

VHDL: VHSIC Hardware Description Language

VHSIC: Very High Speed Integrated Circuit

VLC: Variable Length Code

VLSI: Very Large Scale Integrated Circuit

VRAM: Video RAM

**VQ: Vector Quantization**

# CHAPTER 1 Introduction

For more than a decade, visual communications has been an important area of research. Digital services such as: tele-conferencing, tele-medicine, digital library, distant education, and video-on-demand, etc., to name a few, are being made possible with continuing developments in the area of visual computing and communications.

During the last Mars exploration, 3-D images taken by the Sojourner Rover have once again excited the scientific community and general public. The visual information was processed and losslessly compressed before being sent back to Earth, which was, at the time, 310 million miles away from Mars. Recently, with the advances in tele-medicine, more than 100,000 X-ray images of injured soldiers and civilians have been sent from Bosnia, where Serbian Croatian conflict occurs, to radiologists in Germany for diagnosis and suggestions for treatments [Hardin99]. Another example of useful image and video processing is the Ice Tracking System (ITS) used at Canadian Ice Services (CIS), Environmental Canada [Lee97]. This system is to generate sea-ice

kinematic information over navigable Canadian waterways. ITS must efficiently extract the ice motion between sequential satellite images with minimum errors, and operate in different ice regions without human intervention.

In order to provide reliable visual services, vast quantity of visual data must be processed and compressed in a very short period of time, while maintaining an acceptable fidelity. The raw data stream entails a significantly large bit rate, for example, an uncompressed color video sequence sampled at a frame rate of 30 frames per second (fps), where each frame is typically of size 720 x 576 pixels, requires the transmission of nearly 300 Mbits per second (Mbps). For terrestrial broadcast in North America, the emerging High Definition Television - Grand Alliance (HDTV-GA) has adopted a 6MHz broadcasting channel [Petajan95]. With the presence of significant noise levels and National Television System Committee - TV (NTSC) interference, the Federal Committee on Communications (FCC) service requirements limit the bit rate to about 20 Mbps. Hence, a compression ratio of 15:1 is required, not including error detection/correction and signalling/controlling bit streams. These processing and compression requirements pose a difficult problem to both algorithm developers and computer architects.

During the last few years, the international standardization committees have been developing many visual compression standards. The Joint Photographic Experts Group (JPEG) of the International Standards Organization (ISO) has specified a compression algorithm for still photographic images [ISO/IEC 10918-1]. The International Telegraph and Telephone Consultative Committee (CCITT) has proposed the H.261, and subsequently, the low bit-rate H.263 standards for video telephony and teleconferencing [ITU-T Rec. H.261 & H.263]. The Moving Picture Experts Group (MPEG) of ISO has also proposed the MPEG-1 and MPEG-2 standards for storage and transmission of video sequences [ISO/IEC 11171 & 13818-2]. A new

standard for content based manipulation and coding of video, MPEG-4, has been scheduled to be finalized in early 2000 [Haskell98, Koenen99].

Visual communications involve acquisition, storage, understanding, processing, transmission, and representation of image and video information. Image and video processing, a part of visual communications, involves: representation and modeling, enhancement, restoration, analysis, reconstruction, and compression. Without loss of generality, in many existing techniques, visual data processing algorithms and compression standards possess a high degree of parallelism.

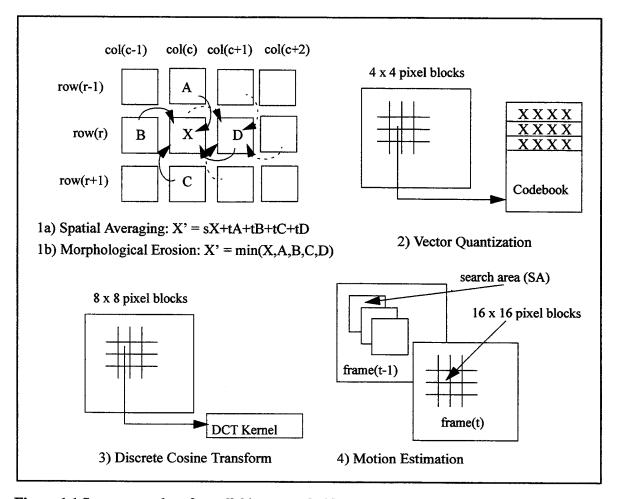

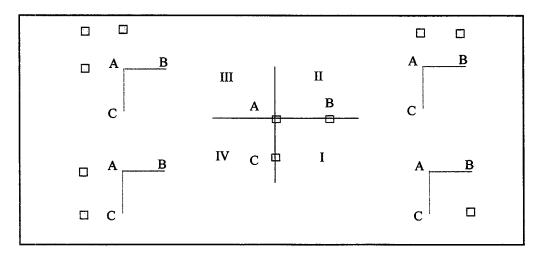

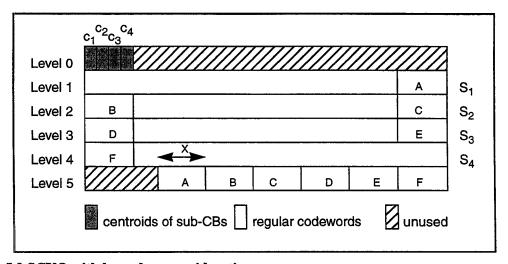

Figure 1.1 Some examples of parallel image and video processing

In particular, the processing of a certain pixel/block of data does not generally require data from distant pixels/blocks, and most of the instructions for processing these pixels/blocks are identical.

Examples of parallel image and video processing operations, such as pixel-based and block-based operations, are shown in Fig. 1.1.

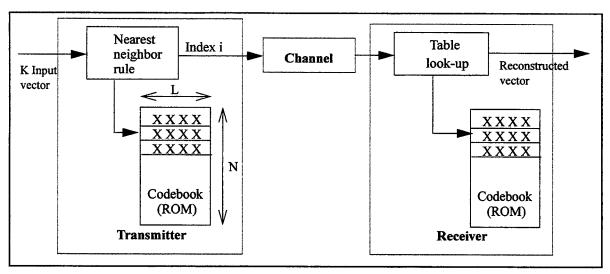

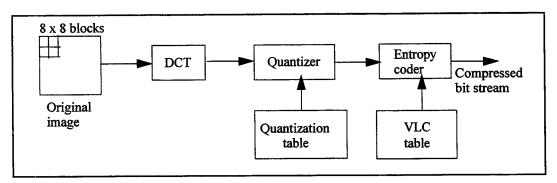

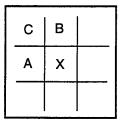

The first example involves image filterings using a linear filter (1a), and a non-linear filter (1b). An image can be low-pass filtered by spatial averaging. The final result is the blurring effect on the original image. In spatial averaging, the new value X' at X is a linear combination of X and the surrounding 4-connected 1 neighbours A, B, C, and D. It is noted that D' can also be computed using the same set of instructions. The same image can also be operated upon by a non-linear filter, a major branch of which is Morphological Image Processing. In the morphological erosion example, X' is, by definition, the minimum of (X, A, B, C, and D) depending on the window defined. Similarly, D' can be similarly derived using the same relationship. Vector Quantization (VQ), in example 2, is generally referred to as the process of representing k-dimensional vectors by their indices in a pre-generated codebook (or a set of representative vectors). In VQ, each image is partitioned into non-overlapping 4 x 4 pixel blocks. Each block, called an input vector, is compared against a set of codevectors in the codebook, and the index of the best match codevector will be used as the address to a lookup-table for reconstruction. In example 3, the Discrete Cosine Transform (DCT), commonly used in spatial image compression, is performed by applying the same set of instructions to every 8 x 8 pixel block of an image. Finally, in Motion Estimation (ME), shown by example 4, the same search procedure is applied to each of the nonoverlapping 16 x 16 pixel macro-blocks. Therefore, parallelism can also be applied at the macroblock level. Details of the image and video processing algorithms will be presented in Chapter 2. In light of the above examples, one can conclude that the image and video processing algorithms map naturally onto Single-Instruction stream, Multiple-Data stream (SIMD) architecture [Flynn72].

<sup>1.</sup> The 8-connected neighbours include the 4-connected neighbours: A, B, C, and D, and the 4 diagonally adjacent neighbours.

The mapping of image and video processing algorithms onto a parallel architecture requires a thorough understanding of the underlying hardware. It has been reported that every year the processor speed of a computer system increases 60% and the memory speed increases by a modest 7% [Patterson96], while the memory capacity is quadrupled every three years [Hennessy94]. The growing processor-memory bandwidth gap cannot be ignored as it results in a loss of performance due to long wait-state and inefficient task scheduling. While the increase in memory capacity enables the designers to place more memory cells on a single chip, it does not bridge the aforementioned bandwidth gap or allow efficient utilization of the increasing speed of the processor. On the other hand, interleaved/pipelined memory modules and hierarchical memories [Patterson98], such as multi-level caches, can enhance the processor-memory interface. For instance, the Rambus architecture [Farmwald92], which supports multiple very high-speed ports, can be used to increase the processor's efficiency. However, these correction measures do not fully take advantage of the parallelism in the visual data processing algorithms. Another important consideration is that the word lengths needed for image and video processing are 8, 16, or 24 bit long, which are much shorter than the common 32- and 64-bit words of today's microprocessor<sup>1</sup>.

Recently, several Intelligent Random Access Memory's (IRAM) have appeared in the literature [Patterson96]. One of the IRAM's, namely the Computational\*RAM (C\*RAM) [Elliott92, Cojocaru93, Cojocaru94, Foss96, McKenzie97, and Torrance98], is a special memory where modular logic circuits are tightly coupled to the compact memory arrays at the sense-amplifiers of the existing RAM. The C\*RAM's concept enables the large *on-chip* memory bandwidth to be fully utilized, while emulating array processors for massively parallel operations. On-chip computing will, in theory, result in either a lower operating power, or a higher operating frequency. This is because the total capacitance at the I/O pads and bus are reduced. Let us take a 1. As an example, a Matlab constant requires 8 bytes of storage.

look at the following expression for the dominant dynamic power dissipation P<sub>D</sub> of Very Large Scaled Integrated (VLSI) Complementary Metal-Oxide Semiconductor (CMOS) circuit:

$$P_D = C_L V_{DD}^2 f_p (1.1)$$

Eq. 1.1 indicates that, for a given voltage  $V_{DD}$  and an operating frequency  $f_p$ , the lower the load capacitance  $C_L$ , the lower the power dissipated  $P_D$ . Also, by rearranging this equation, given a voltage and a power level, it can be seen that the lower the load capacitance, the higher the potential operating frequency.

For instance, if switching energy is  $3\mu$  W/MHz for a 0.3pF bitline at  $V_{DD}$ =3.3 V and  $300\mu$  W/MHz for a 30pF bus, a typical 16Mb DRAM with 4K bitlines cycling at 20MHz requires 240mW, while its 16 buses running at 100MHz takes 480mW [Elliott97]. This analysis will not be further discussed since they are best claimed by the circuit designers. The C\*RAM's concept addresses the above-mentioned image and video processing problems in that:

- Memory bandwidth is fully utilized which is beneficial to memory-bound operations such as motion estimation;

- The emulation of arrays of SIMD processors allows natural mappings of image and video processing/compression algorithms onto the C\*RAM;

- Variable word lengths are readily achievable through bit-serial operations. Furthermore,

arithmetic and logic operations can be optimized at the bit level;

- Applications can be programmed at the controller level which alleviates the needs for specialized hardware;

With parallel image and video processing algorithms and the SIMD-based on-chip array processors in mind, it is apparent that the effective mappings of such algorithms onto the SIMD-based C\*RAM's parallel architecture is an important task.

### 1.1 Thesis outline

According to [Patterson98], given an instruction set, the CPU performance can be increased by the following three factors:

- Increase in clock speed;

- · Improvement of processor organization; and

- Enhancement of its compiler.

The clock speed is technology dependent and, therefore, is dealt with by the device physicists and silicon engineers. The processor, in this case, the C\*RAM, is designed and fabricated by the C\*RAM design team. Issues such as operating power, operating frequency, and data bandwidth have been extensively discussed [Elliott92, Cojocaru93, Cojocaru94, Foss96, McKenzie97, and Torrance98]. The compiler enhancement issue should be most comprehended by application engineers and best addressed by software engineers. The processor performance can only be optimized when there are strong interactions between software developers and hardware designers. Therefore, there is a need for understanding the underlying architecture and the intended applications. Having mentioned the difficult issues in image and video processing such as intense computation and high data bandwidth, a solution to the given challenging problems will be addressed in this thesis entitled Visual Communications on a Memory-Embedded Array Processor: The Computational\*RAM.

In the following chapters, reviews on image and video processing algorithms and C\*RAM-related SIMD designs are provided along with the simulation results to prove that such mappings are, indeed, efficient, economical and yet practical. In Chapter 2, visual data (image and video) processing algorithms and compression standards are reviewed. In Chapter 3, the SIMD-based logic-in-memory designs are examined. Chapter 4 provides the proposed architecture improvements to the existing C\*RAM's along with the underlying C\*RAM assembler, necessary

for C\*RAM implementations and performance analysis. In Chapter 5, implementations of image processing algorithms will be presented. Such implementations include general and morphological image processing algorithms, DCT and RLC, and Sub-Codebook VQ for compressing image using large codebook. Chapter 6 presents a newly proposed low complexity ME algorithm for video compression and its C\*RAM implementation. Finally, Chapter 7 provides the overall implementations of image and video compression standards, followed by the conclusions and future work in Chapter 8.

Appendix A provides other image compression issues which are referred, but not directly related to the thesis contents. Appendix B provides an example of matrix multiplications using C\*RAM. Finally in Appendix C, typical program listings for VHDL-based<sup>1</sup> C\*RAM models, and test files which are used to generate stimuli for performance comparisons in different processing and compression algorithms are presented.

At the end of this thesis, references to the compression standards are listed first followed by references to websites, for example, WSh263. References to other publications are subsequently listed in alphabetical order of principal authors' surnames followed by the publication years.

### 1.2 Thesis contributions

Two VHDL models, a baseline C\*RAM and an enhanced C\*RAM, have been built. Based on the resulting circuit characteristics, software simulations of C\*RAM functionalities have been performed. Macros for image and video processing have been written as well as suggestions for improvements. Contributions to this thesis include:

• Development of an instruction set for C\*RAM operations (Sections 4.4 and 4.5). The assembly codes enable better memory and register allocations at the bit level, and variable

1. Very-high-speed-integrated-circuits Hardware Description Language.

- word-length signed and unsigned arithmetic operations<sup>1</sup>. Variable word-length results in a speed-up of 48% in distortion and filtering computations (Section 6.2.3);

- Enhancements to C\*RAM designs for improving performances of image and video processing algorithms. Such enhancements are the parallel addition/subtraction features (Section 4.1.1) which are used to generate the sum of absolute differences<sup>2</sup> for VQ and ME. This enhancement results in a speed-up of 116% in mean absolute error (MAE) calculations (Section 6.2.3). In addition, the implementation of the one-to-many communication network (Section 4.1.2) enables emulations of Hypercubes, Illiac mesh, and Barrel shifter; and hence, enlarges the range of applications for C\*RAM;

- Proposed Sub-codebook VQ (SCVQ) implementation for fast and efficient VQ search (Section 5.5). SCVQ is proved to result in a speed-up of 400% or higher on any 1-D SIMD array processor; and

- Proposed algorithm for fast motion estimation by extracting the frame features and XORing the binary feature maps for motion vectors (FEXOR) (Section 6.1). Motion estimation using FEXOR generally results in a speed-up of 500% compared to full-search block matching algorithm (FBMA) implemented using the same C\*RAM configuration, and as high as 5,000% over the FBMA on a RISC (Section 6.2.9).

In addition to the proposed algorithms and architectural enhancements, the existing image and video processing algorithms and compression standards have been mapped onto the C\*RAM which are listed below:

- General and morphological image processing techniques (Section 5.2);

- 1. The sum of two 8-b operands is a 9-b intermediate result, and the sum of two 9-b intermediate results is a 10-b final result. Hence, there is no need for a fixed 10-b addition on the 8-b pixels.

- 2. Conventional MAE distortion operation requires 3 steps: subtraction, absolute operations, and addition to the partial sum. The new PE computes the same distortion operation in 2 steps: subtraction, and parallel addition to or subtraction from the partial sum.

- 2-D DCT (Section 5.3) and Run-length coding (Section 5.5.2);

- ME algorithms: Full-search Block Matching Algorithm (FBMA), Pixel Decimation (PD), and Band Pass Bit Plane Matching (BP-BPM) (Section 6.2); and the

- JPEG (Section 7.1), and H.26x and MPEG's compression standards (Section 7.2).

# Overview of Image and Video Processing Algorithms and Compression Standards

In this chapter, parallel image and video processing algorithms are reviewed, followed by summaries of the compression standards. In order to facilitate understanding of visual information of images, color components are first discussed in Section 2.1. In Section 2.2, general image processing techniques are presented. These techniques are listed from sub-pixel operations, pixel operations, to local operations. Mathematical morphology, a major branch of non-linear image processing, is presented in Section 2.3. Data compression techniques, both lossless and lossy, are discussed in Section 2.4 along with the subjective and objective evaluation methods. In Section 2.5, the spatial-domain compression techniques are presented, emphasizing the standardized compression techniques such as DCT. In Section 2.6, temporal-domain compression techniques are reviewed, and a study of fast Motion Estimation techniques is provided. In Section 2.7, a low bit-rate compression technique for table look-up applications, namely, Vector Quantization, is

reviewed. Finally, in Section 2.8, a review of the JPEG image compression standard, H.261 & H. 263, and MPEG-1, -2, and -4 video compression standards is presented.

## 2.1 Image Color Components

When an image is processed, unless otherwise stated, its *luminance* component, commonly known as the grayscale, is implied. The luminance of an image is computed using the following expression:

$$Y = 0.299R' + 0.587G' + 0.114B'$$

(2.1)

where R', G', and B' are the gamma-corrected values<sup>1</sup> of the red, green, and blue components, respectively, obtained by an image sensing device [Netravali89]. The magnitudes of the three multiplicative factors correspond to the responsiveness to red, green, and blue of the cones in the *human visual system* (HVS). For color image processing, other color-difference components, *chrominance*, are used. The derivation of chrominance components will be discussed in detail in Section 2.8 when image and video compression standards are reviewed.

# 2.2 General Image Processing Techniques

In this section, sub-pixel operations are first presented followed by the pixel operations (or point operations). Sub-pixel operations such as bit extraction, level-shifting, and re-quantizing bit-depth to lower resolutions<sup>2</sup> involve the manipulations on the bits representing the pixel. In pixel operations, where no memory is required, a given grayscale level  $u \in [0, L]$  is mapped onto another level  $v \in [0, L]$  according to some transformation v = f(u). The local operations

- 1. Color components appear as voltage waveforms whose instantaneous values are directly proportional to the illumination falling on the corresponding spots of a camera tube target. Such a video signal is not directly suitable for the CRT display because of its non-linearity. Therefore, the received voltage values are compensated using the expression  $I_{display} \propto V^{7}_{received}$  where I is the light intensity, V is the signal voltage, and  $\gamma$  is some power from 2.0 to 3.0.

- 2. The 12-b medical images can be displayed at 8-b or 4-b without the need for the pixel co-processor.

where a processed pixel is determined by a window of its neighboring pixels are presented. Global operations which involve the pixels of the entire image are not vectorizable in the SIMD context, and therefore, not discussed.

Unless otherwise stated, the origin of the coordinates is considered the upper-left corner of an image; and u(m,n) and v(m,n) are the pixels at row m, column n of the input and output images, respectively.

### 2.2.1 Bit Extraction

Progressive image transmission requires the display of images in various qualities from coarse to fine. In general, the image pixel is uniformly quantized to b bits, and some of the bit planes are more visually significant than others. Let the image pixel be represented by:

$$u = k_1 2^{b-1} + k_2 2^{b-2} + \dots + k_{b-1} 2 + k_b$$

(2.2)

If the n<sup>th</sup> most-significant bit (MSB) is extracted for display, the output is formed by setting:

$$v = \begin{cases} L & k_n = 1 \\ 0 & otherwise \end{cases}$$

(2.3)

On most of the 8-b monochrome images, it is noticed that only the first 6 MSB's are visually significant [Jain89]. In applications where image quality is not important such as image browsing, only the more visually significant bits are stored or transmitted, and hence, compression can be achieved.

Sometimes the pixel values are required to be level-shifted from (0, 255) to (-128, 127) with zero being the center. Sub-pixel operations are applied by flipping the MSB of the raw pixel<sup>1</sup>. Typical mappings are shown in Table 2.1:

1. in unsigned representation.

Table 2.1 Level-shifting on 8-b pixels.

| Decimal | Binary    | Decimal | Level-shifted Binary |

|---------|-----------|---------|----------------------|

| 0       | 0000 0000 | -128    | 1000 0000            |

| 1       | 0000 0001 | -127    | 1000 0001            |

| •••     | •••       | •••     | •••                  |

| 127     | 01111111  | -1      | 11111111             |

| 128     | 10000000  | 0       | 00000000             |

| 129     | 10000001  | 1       | 0000001              |

| •••     | •••       | •••     | •••                  |

| 254     | 1111 1110 | +126    | 0111 1110            |

| 255     | 1111 1111 | +127    | 0111 1111            |

# 2.2.2 Contrast Stretching, Clipping, and Thresholding

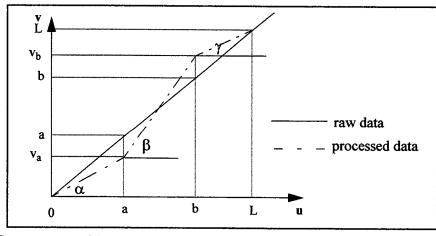

Due to poor / non-uniform lighting conditions, or due to non-linearity / small dynamic range of the imaging sensor, image contrast may be too low for viewing. To stretch the image contrast to a visible level, transformations can be performed on the image (Fig. 2.1) as defined below:

$$v = \alpha u \qquad 0 \le u \le a \tag{2.4}$$

$$v = \beta(u-a) + v_a \qquad a < u \le b$$

(2.5)

$$v = \gamma(u - b) + v_b \qquad b < u \le L \tag{2.6}$$

Figure 2.1 Contrast stretching

where the slope  $\beta$  is chosen to be greater than unity in the region of stretch [a,b].

When the input image is known to be in the range [a,b], clipping can be performed by setting  $\alpha = \gamma = 0$  and  $\beta = \frac{L}{b-a}$ . Therefore:

$$v = 0 \qquad 0 \le u \le a \tag{2.7}$$

$$v = \beta(u-a) \qquad a < u \le b \tag{2.8}$$

$$v = L \qquad b < u \le L \tag{2.9}$$

A special case of clipping is thresholding, where a = b = t, the output hence becomes a binary image.

Intensity Level Slicing: Images from weather maps often contain regions of different interests such as clouds, precipitations, cold/warm fronts, hurricane, etc. Intensity level slicing is transformation which allows segmentation of certain grayscale regions from the rest of the image. In cases where background is of concern, regions of interest are set to white, while the rest of the image (background) remains unchanged:

$$v = \begin{cases} L & a < u \le b \\ u & otherwise \end{cases}$$

(2.10)

#### 2.2.3 Image Subtraction

In pattern analysis, it is desirable to compare two images to identify, for example, the missing components on a printed circuit board (PCB) on an assembly line, or the blood-flow in radiology. The two images are aligned, and then subtracted. Let  $u_1(m,n)$  and  $u_2(m,n)$  be the pixels at row m, column n of two input images 1 and 2, respectively. The output image is defined as:

$$v(m,n) = |u_1(m,n) - u_2(m,n)| \tag{2.11}$$

v(m,n) is later enhanced by thresholding.

A special case of image subtraction is *grayscale reversal*. A negative image can be obtained by reversing the grayscale defined by the following transformation:

$$v = L - u \tag{2.12}$$

This method is of particular interest in machine vision since the dissimilar object, resulting from subtracting the image of a standard object from the image of the object in study, can be detected.

In the following section, pixel operations are performed on the neighboring pixels. The output image is obtained by convolving the input image with a *finite impulse response* (FIR) filter called a *spatial mask*.

#### 2.2.4 Convolution

If W is a chosen window, and a(k,l)'s are the filter weights, the output pixel is obtained by replacing the corresponding input pixel with a weighted sum of the pixels in window W.

$$v(m,n) = \sum_{k} \sum_{l} a(k,l) u(m-k,n-l) \qquad k,l \in W$$

(2.13)

A typical filter, the *Spatial Averaging* filter, often used for noise smoothing, or low-pass filtering. is given by:

$$v(m,n) = \frac{1}{2}u(m,n) + \frac{1}{8}u(m-1,n) + \frac{1}{8}u(m+1,n) + \frac{1}{8}u(m,n-1) + \frac{1}{8}u(m,n+1)$$

(2.14)

Similarly, the unsharp masking filter, commonly used for edge enhancement, is expressed by:

$$v(m,n) = u(m,n) + \lambda g(m,n)$$

(2.15)

where  $\lambda > 0$  and g(m,n) is a suitably defined gradient at location (m,n). A commonly used gradient function is the discrete Laplacian:

$$v(m,n) = u(m-1,n) + u(m+1,n) + u(m,n-1) + u(m,n+1) - 4u(m,n)$$

(2.16)

It has been mentioned earlier that spatial *low-pass filter* can be obtained by spatial averaging. If  $h_{LP}(m,n)$  denotes a FIR low-pass filter, then the FIR *high-pass filter*  $h_{HP}(m,n)$  can be obtained by:

$$h_{HP}(m,n) = \delta(m,n) - h_{LP}(m,n)$$

(2.17)

A spatial band-pass filter  $h_{BP}(m,n)$  can be obtained by:

$$h_{BP}(m,n) = h_{L1}(m,n) - h_{L2}(m,n)$$

(2.18)

where  $h_{L1}(m,n)$  and  $h_{L2}(m,n)$  denote the short-term and long-term averaging low-pass filters, respectively.

While low-pass filters are useful for noise smoothing and interpolation, high-pass filters are useful in edge extraction and image sharpening. Band-pass filters are useful in edge enhancement and emphasis of other high-pass image characteristics in the presence of noise.

While general image processing requires arithmetic operations such as: addition, subtraction, and multiplication, the fundamental operations of morphological image processing involve comparisons and maximum/minimum searches. In the following section, morphological image processing will be presented.

## 2.3 Image Processing using Mathematical Morphology

Mathematical morphology refers to a branch of non-linear image processing and analysis that concentrates on the geometric structures in an image [Doughety92]. Morphological image processing includes enhancement, segmentation, restoration, edge detection, texture analysis, particle analysis, curve filling, and general thinning. These methods have been successfully applied to robot vision, material sciences, industrial inspection, medical imaging, remote sensing, and automatic character recognition.

Mathematical morphology considers images as algebraic sets. Consider the two images, sets A and B. The basic set operators on A and B are the union  $A \cup B$  and the intersection  $A \cap B$ . These operators are applied directly to binary images. For a grayscale digital image, the corresponding operators are the supremum  $A \vee B$  (maximum) and the infimum  $A \wedge B$  (minimum) operators, respectively. Another basic set operator is the complement. The complement of an image f, denoted  $f_c$ , is defined as:

$$f_c(x) = L - f(x) \tag{2.19}$$

where L is 1 for binary images, and 255 for 8-b monochrome images.

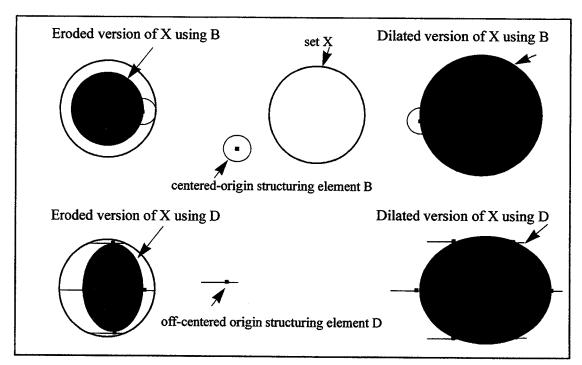

The basic idea of all morphological operators is to consider the image as a set. The image is then touched with a set of known shapes called *structuring elements*<sup>1</sup> (SE). SE's can be a small disk, a horizontal bar or a vertical bar, to name a few. A SE B can be represented by a matrix, and B<sup>T</sup> is the transpose of B. An origin must be specified for each SE. Fig. 2.2 shows some applications where a centered-origin disk SE and a off-centered-origin horizontal bar SE are used.

#### 2.3.1 Erosion and Dilation

Erosion and dilation are the basis of all morphological operations. The *erosion* of a set X by a SE(B), denoted  $\varepsilon_B(X)$ , is defined as the locus of points x such that B is included in X when its origin is placed at x:

$$\varepsilon_R(X) = \{x | B_x \subset X\} \tag{2.20}$$

1. A structuring element can also be considered as a convolution kernel.

Figure 2.2 Erosions and Dilations with different structuring elements B and D

Dilation is the dual operator of erosion. The *dilation* of a set X by a SE(B), denoted  $\delta_B(X)$ , is defined as the locus of points x such that B hits X when its origin coincides with x:

$$\delta_B(X) = \{x | B_x \cap X \neq \emptyset\} \tag{2.21}$$

Dilation of a previously eroded set does not allow, in general, the recovery of the initial set. In fact, there exists no inverse transformations for erosion and dilation.

## 2.3.2 Opening and Closing

The *opening* of an image X by a SE(B), denoted  $\gamma_B(X)$ , is defined as the erosion of X by B followed by the dilation by  $B^T$  (the transpose of B).

$$\gamma_B(X) = \delta_{B^T}[\varepsilon_B(f)] \tag{2.22}$$

The erosion by SE(B) primarily removes objects (or noise) of sizes equal to or less than B. Subsequent dilation restores the shape of the remaining objects to some extent. Sometimes, the remaining objects become larger than their originals.

It is sometimes desirable to preserve the shapes of the remaining objects. Therefore, *opening-by-reconstruction* operation is required and is defined as the erosion of a set using SE(B) followed by a dilation using SE(B<sup>T</sup>) with a condition. This condition ensures that the sizes of the remaining objects do not get larger after undergoing dilation. Therefore, if an object is not eliminated, its size and shape are preserved.

The dual operation of opening is closing. The *closing* of an image X by a SE(B), denoted  $\phi_B(X)$ , is defined as the dilation of X by SE(B) followed by the erosion by SE(B<sup>T</sup>). *Closing-by-reconstruction* is similarly defined.

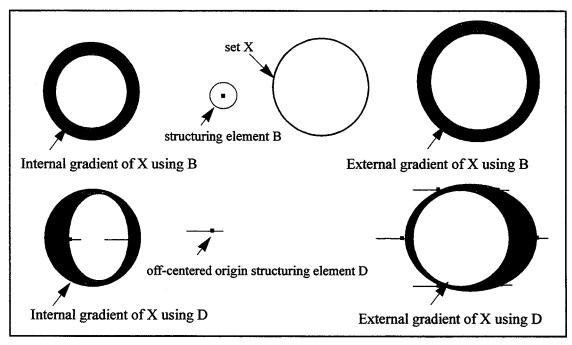

## 2.3.3 Morphological Gradients

The basic morphological gradient is the gradient of Beucher g. It is defined as the arithmetic difference between the dilated and the eroded versions of the original image X with SE(B).

$$g(X) = \delta_B(X) - \varepsilon_B(X) \tag{2.23}$$

g(X) represents the maximum variation of the grayscale intensities within a neighborhood rather than a local slope.

It is crucial to distinguish between the internal and external boundaries of a region. Morphological internal gradient (MIG) of an image is the arithmetic difference between the original image X and its eroded image  $\varepsilon_B(X)$ , while morphological external gradient (MEG) of an image is the arithmetic difference between the dilated  $\delta_B(X)$  and its original image X.

MIG and MEG operations are shown in Fig. 2.3. Morphological gradient operations remove noise and pixel variations within a solid region while preserving sharp edges. Therefore, morphological smoothing is generally preferred over linear blurring for edge detection [Serra82].

Figure 2.3 Internal and External Gradients using structure elements B and D

## 2.3.4 Edge Detection

Having introduced various linear and non-linear filters, it is now appropriate to present a few edge detection techniques. Edge detection has been employed for enhancing the features of objects in an image to a machine detectable or humanly visible level where they can be used to make further decisions. In machine vision, edge information can be used to separate nuts and bolts in an assembly line, and to identify whether a product is defective based on its size and shape. As will be introduced in Section 6.1, edge detection techniques are also applied to transform an b-bit image to a 1-bit image for low-complexity motion estimation. There are mainly 3 types of edges: step (as in step function), ramp, and texture edges. Step and texture edges can be detected using first-order filters, while ramp edges can only be effectively detected using multi-scale morphological gradient [Wang96], or second-order filters.

To detect edges, there are four steps: pre-processing, slope approximation, thresholding, and post-processing. Pre-processing involves noise removal and blurring. Slope approximation is to find

gradients in different directions at each pixel. Thresholding is to select the highest gradient at a certain direction of each pixel, and post-processing involves noise removal (if any) and edge connection or merging. Simple edge detection techniques only require steps 1 and 3. A difference image obtained by subtracting the blurred version from its original image is an example. The morphological counterparts are MEG and MIG. More elaborate edge detection techniques require all four steps. First-order techniques are Prewitt, Sobel, Laplacian, and the one proposed by [Canny86] using linear filters, and those proposed by [Lee87, Verbeek88, Hertz92] use non-linear operations. Second-order techniques include [Johnson90], and Laplacian of Gaussian.

For low-complexity motion estimation, the candidate edge detection techniques should be simple and efficient<sup>1</sup>, in which all 3 types of edges should ideally be recognized. The connectivity of edges are not critical since unconnected edges are common to both current and reference frames.

In subsequent sections, image and video compression techniques and standards are reviewed. In order to better understand techniques, some data compression concepts and evaluation methods are introduced next.

## 2.4 Data Compression Techniques

The large memory capacity and high channel bandwidth requirements for storage and transmission of visual data necessitates the use of efficient image and video compression techniques while acceptable fidelity is maintained. Image and video compression, whose goal is to minimize the number of bits required to represent an image and video signal, is essentially a reduction process [Jain81a] in which spatial, temporal, structure, and psycho-visual redundancies are exploited.

1. The low-complexity motion estimation algorithms only remain attractive if their computation requirement is kept low compared to the compute intensive of the full-search block matching algorithm.

In an image and video frame, the pixels in close vincinity are usually highly correlated. For example, pixel values in a local region do not change significantly from one location to the next; and hence, a pixel value can be approximately inferred from the neighboring pixel values. This correlation, called the *spatial redundancy*, can be easily observed and is removed by employing *intraframe* coding techniques such as, predictive coding, vector quantization, transform coding, entropy coding, and their hybrids.

Temporal redundancy, refers to the correlation between the successive frames in a video sequence. The differences between successive frames are due to object motions and/or camera operations<sup>1</sup>. Temporal redundancy is usually detected and removed by applying *interframe* coding techniques such as, predictive coding, adaptive vector quantization, conditional frame replenishment, motion estimation and compensation, and predictive coding with motion estimation.

Structure redundancy results from the fact that an image is the projection of 3-D objects onto a 2-D plane [Aizawa87]. Structure redundancy also refers to the representation of objects based on their basic forms and movements. For instance, human facial expression - including forehead, eye-browns, eyes, cheek, nose, mouth, and chin - can be categorized into many classes depending on the individual mood at a particular time. Each expression can be characterized by a set of controllable parameters which is much less than the amount of image data themselves, therefore, high compression can be achieved.

The seven basic camera operations include: fixed (no motion involved), zooming (camera's lens forward and backward while the whole mechanism is fixed on its stand), panning (camera head's movement to the left and to the right), tilting (camera head's movement up and down), booming (camera movement in the horizontal direction), tracking (camera movement in the forward and backward direction), and dollying (camera movement in the vertical direction). Finally, *psycho-visual redundancy* refers to information which may be removed without sacrificing the subjective image quality due to the properties of the HVS [Chen90, Xie91]. For example, human eyes are more sensitive to small signal changes in dark areas. Other properties include: more sensitivity to noise with patterns compared to random noise<sup>1</sup>, less sensitivity to faster moving objects, and less sensitivity to distortion at higher spatial frequencies.

Image and video compression techniques can be generally classified into: "distortionless" or lossless and "minimum distortion" or lossy schemes. Lossless compression minimizes the average number of bits per pixel (bpp) without any loss in objective image quality, while lossy compression is to minimize the bit rate R(D) for a given average distortion D or equivalently, to minimize the average distortion for a given bit rate. More detailed descriptions of lossless and lossy compression schemes are discussed in Section A.1.

In studying the performance of image compression schemes, image quality can be evaluated using subjective and objective measures. Subjective measures refer to the judgement of a human viewer using quality rating scales such as: excellent, good, fair, poor, and bad; or impairment rating scales such as imperceptible, perceptible but not annoying, slightly annoying, annoying, and very annoying. The average of the ratings for a given image is called the mean opinion score (MOS) and used as a measure of the quality of the reconstructed image. Objective measures are sometimes referred to as distortion measures. The most commonly used distortion measures are the Mean Square Error (MSE), Normalized MSE (NMSE), Mean Absolute Error (MAE), Signal-to-Noise ratio (SNR), and Peak Signal-to-Noise ratio (PSNR). NMSE generally provides a more precise judgement to a particular coding algorithm. On the other hand, many use PSNR as the performance indicator. PSNR is, however, very image dependent. Images with little details tend to

1. Evenly scattered small spots on the windshield can be tolerated compared to the streaks made by the wipers.

have higher PSNR's, compared to those with many details, assuming the same coder is applied. The definitions of the objective measures are reviewed in Section A.2.

# 2.5 Spatial-Domain Compression Techniques

## 2.5.1 Predictive Coding