# Mixed Analog-Digital Design Considerations in Deep Submicron CMOS Technologies

By

## Seyfi Bazarjani

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Ottawa-Carleton Institute for Electrical Engineering

Department of Electronics

Faculty of Engineering

Carleton University

Ottawa, Canada

24 July 1996

© Seyfi S. Bazarjani 1996

The undersigned recommend to the Faculty of Graduate Studies and Research the acceptance of the thesis

"Mixed Analog-Digital Design Considerations in Deep Submicron CMOS Technologies" submitted by Seyfollah S. Bazarjani in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Prof. Martin Snelgrove

Thesis Supervisor

Prof. J.S. Wight

Chairman,

Department of Electronics

Prof. Gabor Temes

**External Examiner**

Ottawa-Carleton Institute for Electrical Engineering

Department of Electronics

Faculty of Engineering

Carleton University

24 July 1996

## **Abstract**

Higher speed and higher density are the main thrusts of CMOS technology and are achieved by device miniaturization. In deep submicron geometries, the supply voltage is scaled down to prevent reliability hazards such as oxide breakdown and hot carrier effects and also to reduce energy per operation of digital circuits. Lowering the supply voltage directly reduces the signal swing, which in turn makes the design of high-speed wide dynamic range mixed-signal SC circuits a challenge. It is also desirable to implement SC circuits in a standard digital CMOS process, where double-poly capacitors are not available, because the driving forces behind the CMOS technologies are DRAMs and microprocessors which do not require linear capacitors.

This thesis demonstrates that analog circuit design can track projected digital technology until at least the year 2010. It addresses the design of low-voltage and high-speed SC circuits and also explores the feasibility of using MOSFET capacitors in a linear SC circuit. The thesis describes an experimental 1 V CMOS process implemented as a subset of a 0.5  $\mu$ m dual n<sup>+</sup>/p<sup>+</sup> poly gate process using natural MOSFETs. A 1 V experimental SC sigma-delta modulator is presented—the lowest supply voltage reported so far for SC  $\Sigma\Delta$  modulators. Also described is a high-speed fourth-order SC bandpass  $\Sigma\Delta$  modulator and a novel fourth-order double-sampled SC bandpass  $\Sigma\Delta$  modulator together with their experimental results. Finally, a fourth-order bandpass SC  $\Sigma\Delta$  modulator designed in a digital CMOS process using pMOSFET capacitors is described.

## Acknowledgments

I wish to express my gratitude to my advisor Professor Martin Snelgrove for his support and guidance during the course of my Ph.D. studies at Carleton University. I would also like to thank the members of my doctoral committee, Professors Miles Copeland, Tad Kwasniewski, Calvin Plett, and Garry Tarr for their advice.

It was a great pleasure to interact with members of my research group at Carleton University. Special thanks are due to Omid Shoaei, for sharing his knowledge on sigmadelta modulators through many technical discussions; Theo Varelas, for assisting me with chip layout and testing; Luc Lussier and Philip Lauzon for laying out test boards; and Alana Wirta, for helping me with administrative matters.

Most of all, I would like to thank my wife Jaleh for her love and companionship, my daughter Anahid for her cheerfulness which is a source of inspiration for me, and my mother for her endless support.

The financial and technical support of Nortel is gratefully acknowledged. I owe thanks to my past and present management at Nortel for instituting a research agreement for me. In particular, I am grateful to, Michael Krause, David Simmons, Kathy Howlett, Leonard McCready, Don Treen, David Agnew, David Lynch, and Jack Dyment. Thanks also to Robin Collins, microsurgeon at Nortel, for chip microsurgery and microphotographs.

## **Table of Contents**

| Abstract                                                                      |     |

|-------------------------------------------------------------------------------|-----|

| Acknowledgments                                                               |     |

| Table of Contents                                                             | i   |

| List of Figures                                                               | iv  |

| List of Tables                                                                | ix  |

| List of Abbreviations                                                         | X   |

| List of Symbols                                                               | xii |

| 1 Chapter 1 Introduction                                                      | 1   |

| 1.1 Motivation                                                                | 1   |

| 1.2 Thesis Objectives                                                         | 2   |

| 1.3 Contributions                                                             | 3   |

| 1.4 Thesis Outline                                                            | 4   |

| Circuits  2.1 Introduction                                                    | 6   |

| 2.1 Introduction                                                              |     |

| 2.2.1 CMOS Scaling in the Next Decade                                         |     |

| 2.2.2 Vt Scaling Issues                                                       |     |

| 2.3 Low-Voltage Mixed-Signal Design                                           |     |

| 2.3.1 Limits on Digital CMOS Supply Voltage Scaling                           |     |

| 2.3.2 Limits on Analog CMOS Supply Voltage Scaling                            |     |

| 2.3.3 Previous Work on Low-Voltage Digital Circuits                           |     |

| 2.3.4 Previous Work on Low-Voltage Analog Circuits                            | 20  |

| 2.3.4.1 Low-Voltage Active-RC Circuits                                        | 20  |

| 2.3.4.2 Low-Voltage Switched-Current Circuits                                 | 21  |

| 2.3.4.3 Low-Voltage Switched-Capacitor Circuits                               | 22  |

| 2.3.5 Impact of Voltage Scaling on Power Dissipation of Mixed-Signal Circuits | 24  |

| 2.4 Oversampled Sigma-Delta Modulator Overview                                | 28  |

| 2.4.1 Lowpass Sigma-Delta Modulators                                          | 30  |

| 2.4.2 Randness Sigma Dalta Modulators                                         | 31  |

| 2.4.3 High-Speed SC Bandpass Sigma-Delta Modulator                | 32            |

|-------------------------------------------------------------------|---------------|

| 2.5 Analog Circuit Design in a Standard Digital CMOS Process      | 34            |

| 2.5.1 SI Circuit Technique                                        | 35            |

| 2.5.2 High Performance Memory Cells                               | 39            |

| 2.5.3 Linear SC Circuit Techniques in a Digital CMOS Process      | 41            |

| 2.6 A Comparative Study of SC and SI for Low-Voltage Applications | 46            |

| 2.7 Summary                                                       | 48            |

| 3 Chapter 3 Low-Voltage SC Design with Low-Vt MOSFETs             | 50            |

| 3.1 A Low-Vt Process                                              | 51            |

| 3.2 Circuit Technique for Vt Reduction                            | 54            |

| 3.3 Low-Vt Transmission Gate Design for SC Circuits               | 57            |

| 3.4 Series Transmission Gate and Composite Switch                 | 63            |

| 3.4.1 Series Transmission Gate Switch                             | 65            |

| 3.4.2 Composite Switch                                            | 67            |

| 3.5 A 2.25 V Second-Order Sigma-Delta Modulator                   | 70            |

| 3.5.1 Short-Channel MOSFETs                                       | 70            |

| 3.5.2 Short-Channel MOSFETs Layout Issues                         | 72            |

| 3.5.3 Measured SNDR                                               | 72            |

| 3.6 A 1 V First-Order Sigma-Delta Modulator                       | 73            |

| 3.6.1 1 V opamp                                                   | 74            |

| 3.6.2 Comparator                                                  | 75            |

| 3.6.3 Switches                                                    | 76            |

| 3.6.4 Measured Results for the 1 V Sigma-Delta Modulator          | 77            |

| 3.7 Summary                                                       | 78            |

| 4 Chapter 4 High-Speed SC Fourth-Order Bandpass Sigma-Del<br>80   | ta Modulators |

| 4.1 Modulator Architecture                                        | 80            |

| 4.2 Half Delay SC Circuits                                        | 83            |

| 4.3 Full Delay SC Circuits                                        | 93            |

| 4.4 A SC Bandpass Sigma-Delta Modulator                           |               |

| 4.4.1 Sources of Error                                            | 106           |

| 4.5 A Double-Sampled SC Bandpass Sigma-Delta Modulator            | 111           |

| 4.5.1 Sources of Error                                            | 113           |

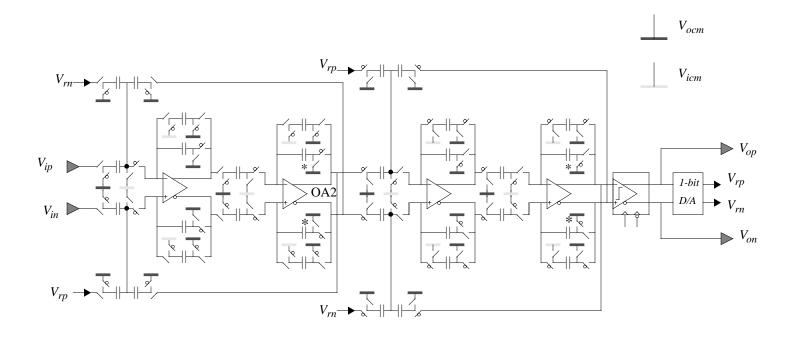

| 4.6 Implementation                                                            | 117 |

|-------------------------------------------------------------------------------|-----|

| 4.7 Measurement Results                                                       | 125 |

| 4.7.1 Fourth-Order Bandpass Sigma-Delta Modulator                             | 125 |

| 4.7.2 Double-Sampled Fourth-Order SC Bandpass Sigma-Delta Modulator           | 127 |

| 4.8 Summary                                                                   | 129 |

| 5 Chapter 5 SC Bandpass Sigma-Delta Modulator Design In a Digital CM          | IOS |

| Process                                                                       | 130 |

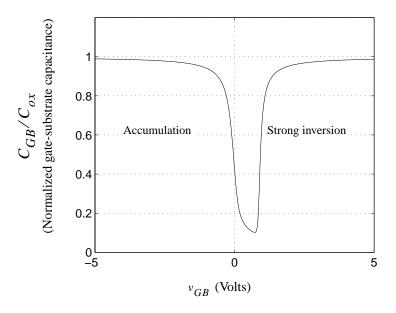

| 5.1 MOS Capacitor                                                             | 130 |

| 5.2 Distortion in SC Amplifier Caused by Non-linear Capacitors                | 136 |

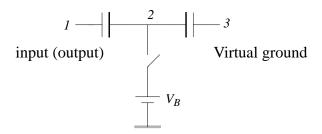

| 5.3 A SC Delay Circuit Using pMOSFET Capacitors                               | 139 |

| 5.4 A Fourth-Order SC Bandpass Sigma-Delta Modulator Using pMOSFET Capacitors | 141 |

| 5.4.1 Linear Charge Processor Viewpoint                                       | 145 |

| 5.5 Summary                                                                   | 146 |

| 6 Chapter 6 Conclusions and Future Work                                       | 147 |

| 6.1 Summary                                                                   | 147 |

| 6.2 Conclusions                                                               | 149 |

| 6.3 Future Work                                                               | 149 |

| Appendix A: Appendix A MOSFET Equations                                       | 151 |

| Appendix B: Appendix B Natural MOSFET Characteristics                         | 153 |

| References                                                                    | 156 |

# **List of Figures**

| Figure 2.1: A negative feedback Vt adjust circuit                                                   | 12        |

|-----------------------------------------------------------------------------------------------------|-----------|

| Figure 2.2: A basic CML inverter-buffer gate                                                        | 14        |

| Figure 2.3: A fully differential CMOS Opamp                                                         | 15        |

| Figure 2.4: Complementary transmission gate switch on-conductance for (a) VDD<2Vt, (b) VDD          | =2Vt, and |

| (c) VDD>2Vt                                                                                         | 17        |

| Figure 2.5: A simple current mirror cell                                                            | 18        |

| Figure 2.6: An active-RC integrator                                                                 | 21        |

| Figure 2.7: A non-inverting SC integrator and its associated 2-phase non-overlapping clock          | 22        |

| Figure 2.8: A switched-opamp SC integrator                                                          | 24        |

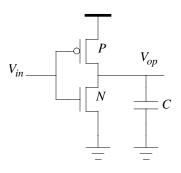

| Figure 2.9: CMOS inverter                                                                           | 25        |

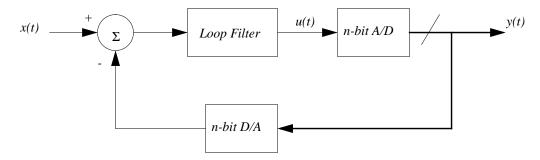

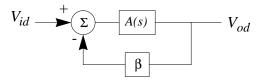

| Figure 2.10: A block diagram of a SD modulator                                                      | 28        |

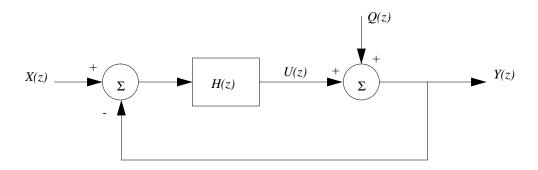

| Figure 2.11: Equivalent linear system of Figure 2.10                                                | 29        |

| Figure 2.12: Pole/zero placement of (a) a first-order lowpass SD and (b) a second- order bandpass S | D derived |

| by transformation                                                                                   | 32        |

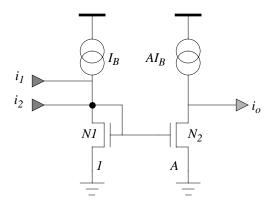

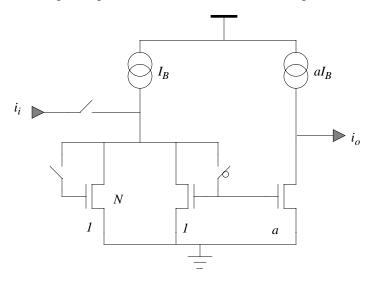

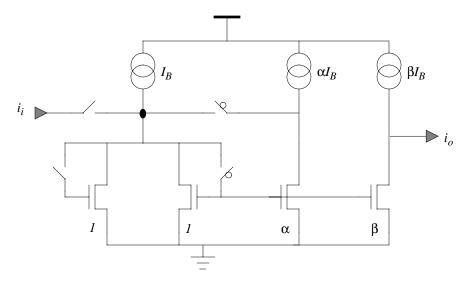

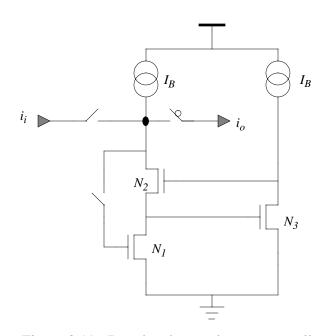

| Figure 2.13: A weighted current mirror                                                              | 36        |

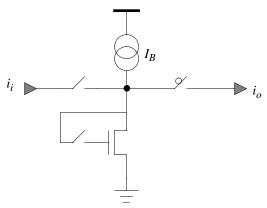

| Figure 2.14: A first generation memory cell                                                         | 36        |

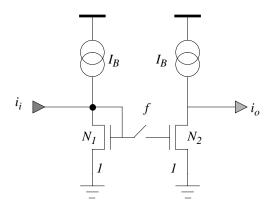

| Figure 2.15: First generation SI integrator                                                         | 37        |

| Figure 2.16: Second generation SI memory cell                                                       | 38        |

| Figure 2.17: A second generation non-inverting lossless integrator                                  | 38        |

| Figure 2.18: Second generation damped integrator                                                    | 39        |

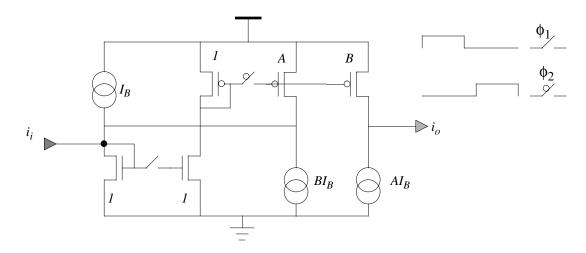

| Figure 2.19: Regulated cascode memory cell                                                          | 40        |

| Figure 2.20: S2I memory cell                                                                        | 41        |

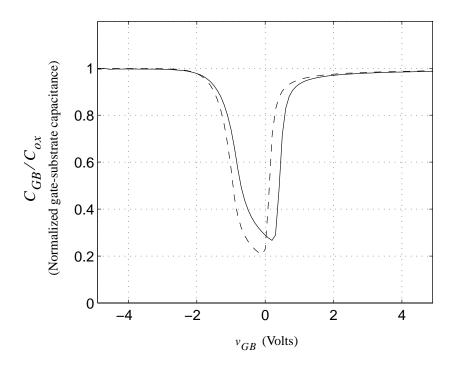

| Figure 2.21: nMOSFET CV plot                                                                        | 42        |

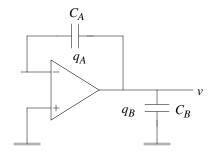

| Figure 2.22: A charge mirror cell                                                                   | 44        |

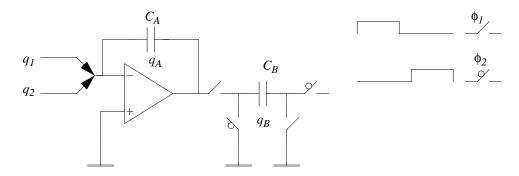

| Figure 2.23: A SC building block                                                                    | 45        |

| Figure 2.24: The MOSFET SC branch                                                                   | 45        |

| Figure 2.25: A SC circuit using the MOSFET SC branch                                                | 46        |

| Figure 2.26: A two-stage pole-splitting opamp                                                       | 48        |

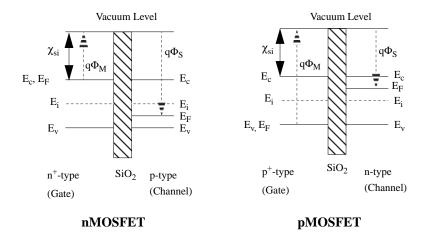

| Figure 3.1: Gate-substrate workfunction of nMOSFET and pMOSFET in an n+/p+ dual poly gate           | CMOS      |

| process                                                                                             | 52        |

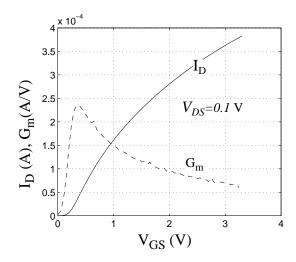

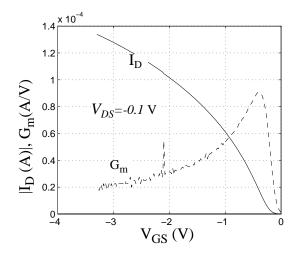

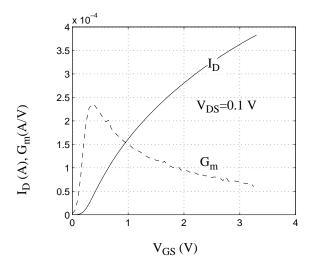

| Figure 3.2: Measured ID (A) and Gm (A/V) versus VGS (V) for "natural" nMOSFET                       | 53        |

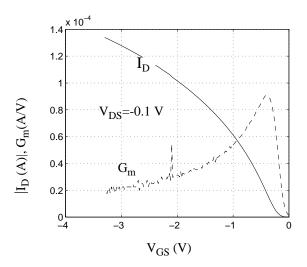

| Figure 3.3: Measured  ID (A)  and Gm (A/V) versus VGS (V) for "natural" pMOSFET                     | 53        |

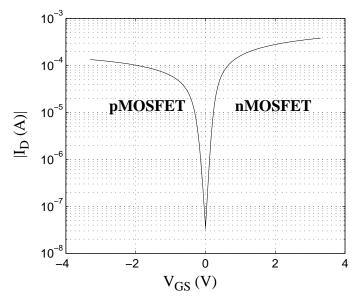

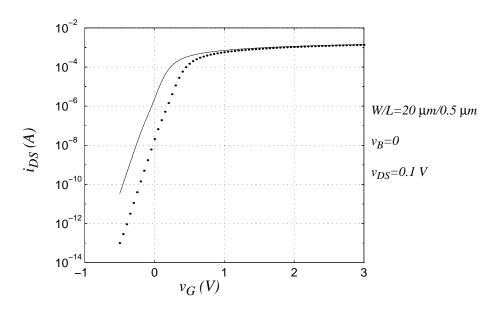

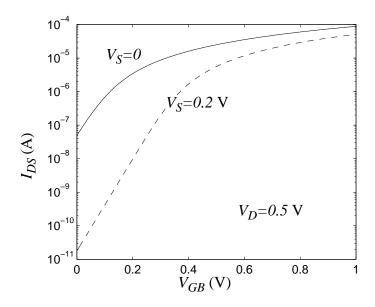

| Figure 3.4: Measured subthreshold characteristics of natural nMOSFET and nMOSFET                    | 54        |

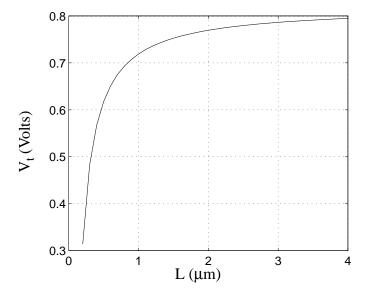

| Figure 3.5: Threshold voltage as a function of channel length                                           | 55   |

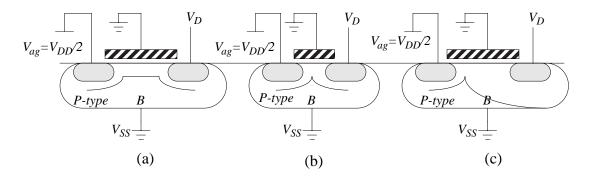

|---------------------------------------------------------------------------------------------------------|------|

| Figure 3.6: Turned-off nMOSFET switch exhibiting (a) no punchthrough, (b) punchthrough due to short     | Į.   |

| channel length, and (c) punchthrough due to large drain to source potential                             | 56   |

| Figure 3.7: A non-inverting SC integrator                                                               | 58   |

| Figure 3.8: Equivalent circuit of Figure 3.7 during                                                     | 60   |

| Figure 3.9: Equivalent circuit of Figure 3.7 during non-overlapping period                              | 62   |

| Figure 3.10: Equivalent circuit of Figure 3.7 during                                                    | 63   |

| Figure 3.11: Measured iDS vs. vG for an nMOSFET with Vt=130 mV and vS=0 (solid line) and vS=0.2         | V    |

| (dotted line)                                                                                           | 64   |

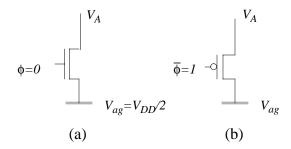

| Figure 3.12: Turned-off (a) nMOSFET and (b) pMOSFET switches                                            | 65   |

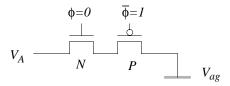

| Figure 3.13: A series transmission gate switch                                                          | 66   |

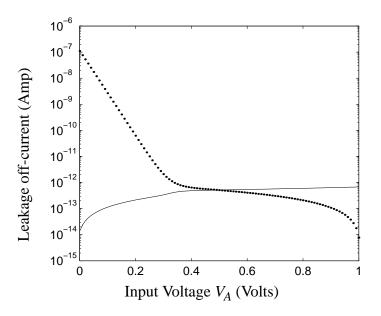

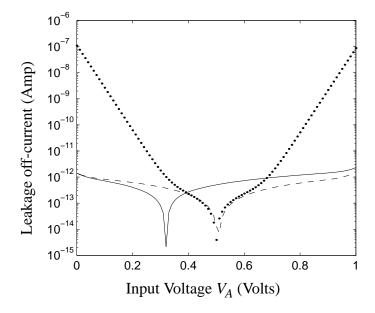

| Figure 3.14: Leakage off-current through an nMOSFET switch (dotted line) and a STG switch (solid line   | e)   |

| versus input voltage                                                                                    | 66   |

| Figure 3.15: On-conductance of the nMOSFET (dotted-line) and STG switch (solid-line) versus input       |      |

| signal                                                                                                  | 67   |

| Figure 3.16: A composite switch                                                                         | 68   |

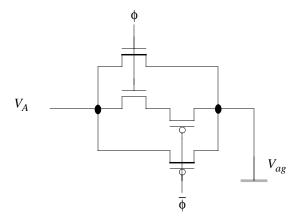

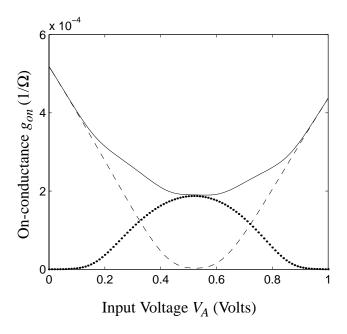

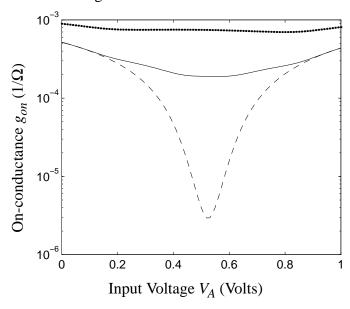

| Figure 3.17: Simulated on-conductance for high-Vt TG switch (dashed-line), low-Vt series transmission g | gate |

| switch (dotted-line), and the composite switch (solid-line) versus input signal                         | 68   |

| Figure 3.18: On-conductance for high-Vt TG switch (dashed-line), low-Vt TG switch (dotted-line), and    | the  |

| composite switch (solid-line) versus input signal                                                       | 69   |

| Figure 3.19: Leakage current for high-Vt TG switch (dashed-line), low-Vt TG switch (dotted-line), and   | the  |

| composite switch (solid-line) versus input signal                                                       | 69   |

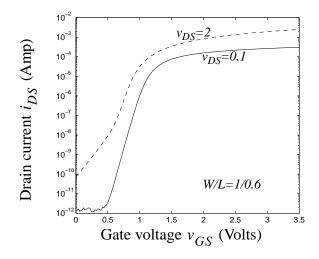

| Figure 3.20: Drain current versus gate voltage for a 0.6 mm nMOSFET with vDS=0.1 V (solid line) and     |      |

| vDS=2 V (dashed line)                                                                                   | 71   |

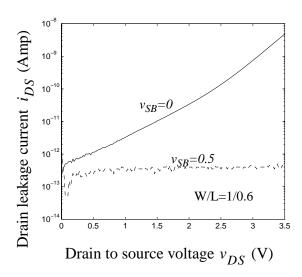

| Figure 3.21: Drain off-current (vG=0) versus drain to source voltage for a 0.6 mm nMOSFET with vSB=     | =0   |

| (solid line) and vSB=0.5 V (dashed line)                                                                | 72   |

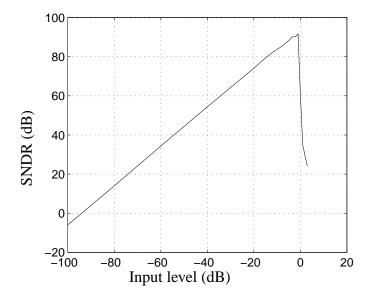

| Figure 3.22: Measured SD modulator performance                                                          | 73   |

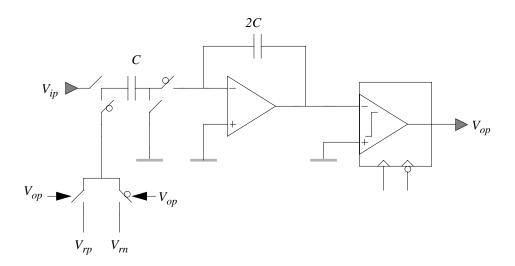

| Figure 3.23: A first-order SC SD modulator                                                              | 74   |

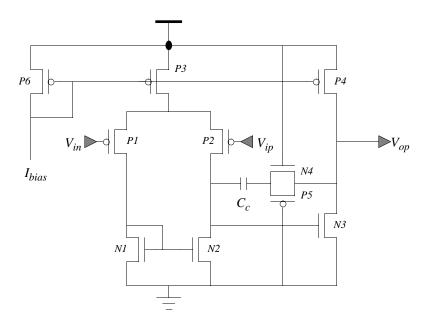

| Figure 3.24: A two-stage pole-splitting opamp                                                           | 75   |

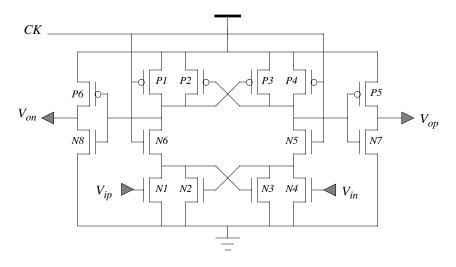

| Figure 3.25: Schematic of the comparator                                                                | 76   |

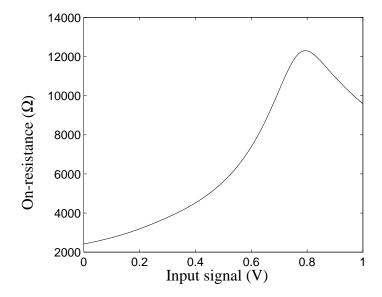

| Figure 3.26: Simulated transmission gate switch resistance as a function of input signal                | 77   |

| Figure 3.27: Simulated off-current for the nMOSFET switch                                               | 78   |

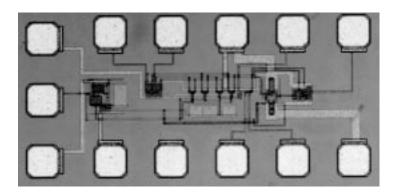

| Figure 3.28: Chip die microphotograph                                                                   | 78   |

| Figure 3.29: Measured spectrum (Vip = 420 mVpp)                                                         | 79   |

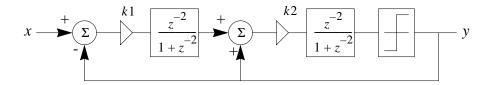

| Figure 4.1: A fourth-order double resonator bandpass SD modulator                                       | 81   |

|                                                                                                         |      |

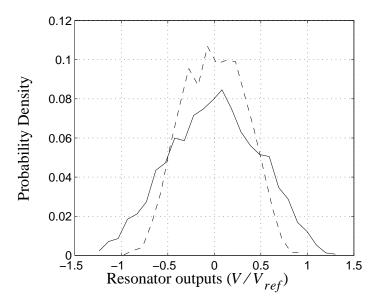

| Figure 4.2: Histograms of output levels for the first (solid line) and the second (dash | hed line) resonator for a - |

|-----------------------------------------------------------------------------------------|-----------------------------|

| 6 dB tone input                                                                         | 82                          |

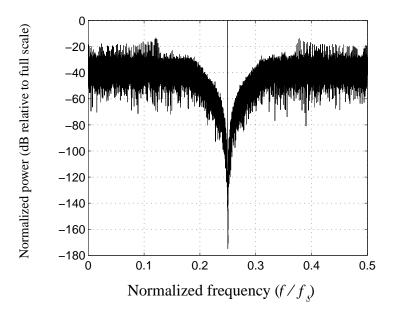

| Figure 4.3: Simulated output spectrum of the fourth-order bandpass SD modulator         | in Figure 4.1 for a         |

| sinusoidal input.                                                                       | 82                          |

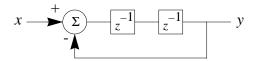

| Figure 4.4: Resonator using delay cells                                                 | 83                          |

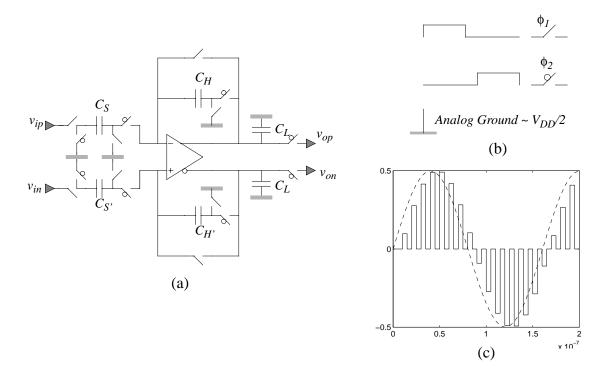

| Figure 4.5: (a) A SC half delay gain stage, (b) 2-phase non-overlapping clock, (c) i    | nput (dashed line) and      |

| output (solid line) waveforms                                                           | 84                          |

| Figure 4.6: A single-ended equivalent circuit of Figure 4.5a during (a) and (b) pha     | ıses85                      |

| Figure 4.7: Opamp in the closed-loop configuration during                               | 86                          |

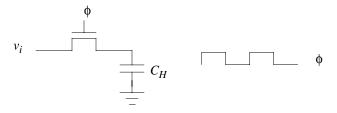

| Figure 4.8: A simple SC sample-and-hold circuit                                         | 87                          |

| Figure 4.9: Bottom-plate sampling technique to eliminate signal dependent charge        | injection88                 |

| Figure 4.10: Fully differential bottom-plate sampling to cancel fixed charge injection  | on and clock                |

| feedthrough                                                                             | 89                          |

| Figure 4.11: Single-ended equivalent circuits of Figure 4.5a during (a) sampling ph     | ase, and (b) holding        |

| phase                                                                                   | 89                          |

| Figure 4.12: One capacitor sample-and-hold circuit                                      | 91                          |

| Figure 4.13: A simple cascade SC delay circuit                                          | 93                          |

| Figure 4.14: A SC delay gain stage                                                      | 94                          |

| Figure 4.15: A single-ended equivalent circuit of Figure 4.14 during (a) and (b) pl     | nases94                     |

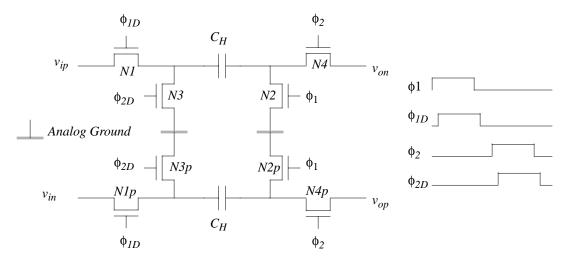

| Figure 4.16: A double-sampled SC delay circuit                                          | 97                          |

| Figure 4.17: A single-ended equivalent circuit of Figure 4.16 during (a) and (b) pl     | nases98                     |

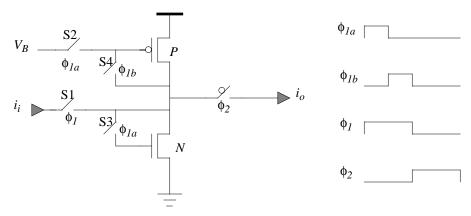

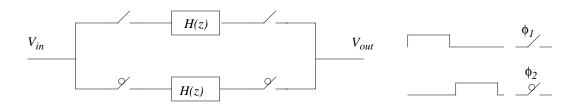

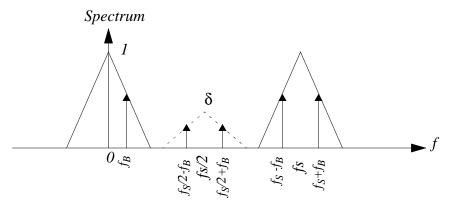

| Figure 4.18: Two-path SC circuit and clock phases                                       | 100                         |

| Figure 4.19: Spectrum of the input signal (solid line) and the attenuated odd sample    | es of the input signal      |

| (dotted line)                                                                           | 101                         |

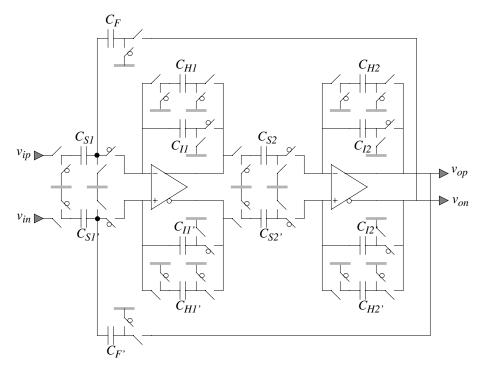

| Figure 4.20: A SC resonator using two delay cells                                       | 102                         |

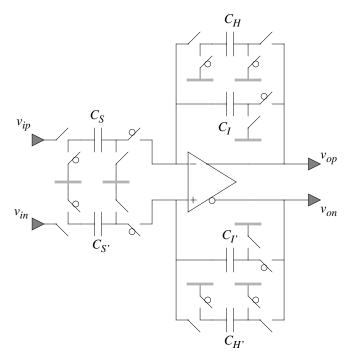

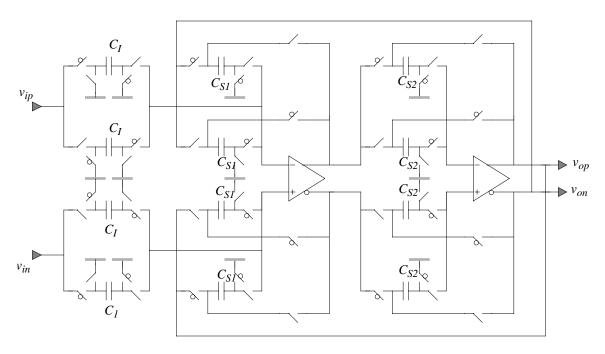

| Figure 4.21: A fourth-order SC bandpass sigma-delta modulator                           | 104                         |

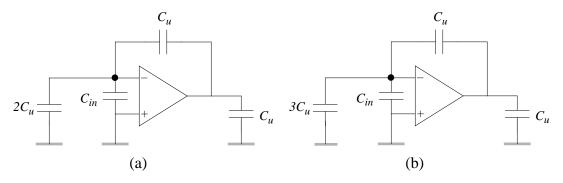

| Figure 4.22: Worst case opamp loading for (a) bandpass SD of Figure 4.21 (b) band       | dpass SD modulator in       |

| [Longo93]                                                                               | 105                         |

| Figure 4.23: Output spectrum from Eldo simulation                                       | 105                         |

| Figure 4.24: Output spectrum of the fourth-order bandpass SD modulator with an o        | pamp gain of 40 dB and      |

| opamp input capacitance of Cin =2Cu                                                     | 109                         |

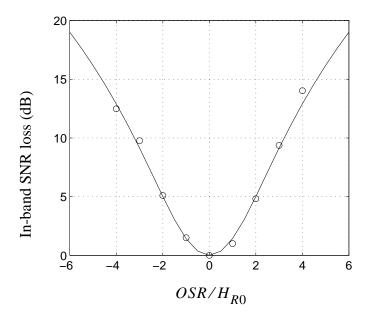

| Figure 4.25: SNR loss versus OSR / HR0 from analytical result (solid line) and from     | m simulation results (o     |

| points).                                                                                | 110                         |

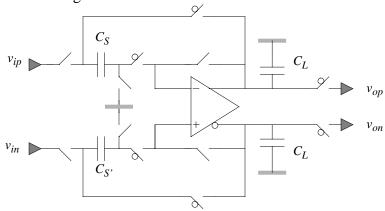

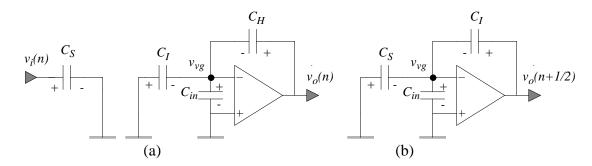

| Figure 4.26: A double-sampled SC resonator                                              | 112                         |

| Figure 4.28: Output spectrum from Eldo simulation                                       | 113                         |

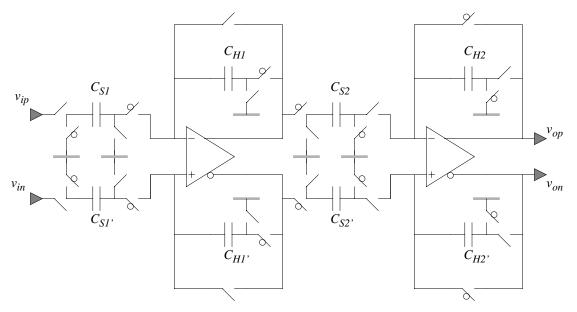

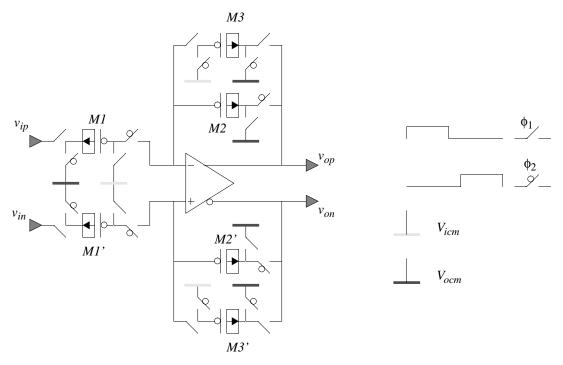

| Figure 4.27: A double-sampled SC fourth-order bandpass sigma-delta modulator                                                                                                  | 114     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

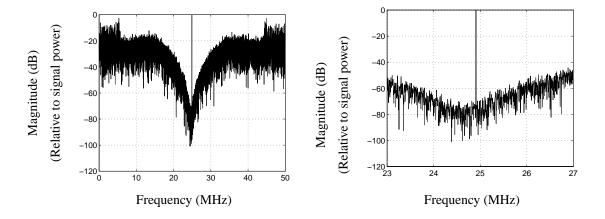

| Figure 4.29: Output spectrum of the double-sampled bandpass sigma-delta modulator with 1% capacitations and the sampled bandpass sigma-delta modulator with 1% capacitations. | itor    |

| mismatch between the two paths. Note that the image power is 40 dB below the signal p                                                                                         | ower    |

| 115                                                                                                                                                                           |         |

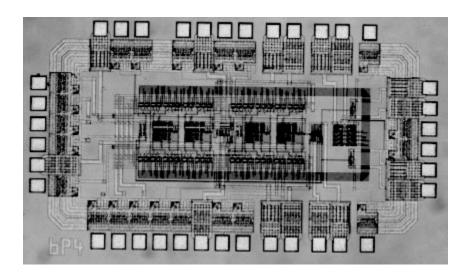

| Figure 4.30: Chip microphotograph of the fourth-order SC bandpass sigma-delta modulator                                                                                       | 117     |

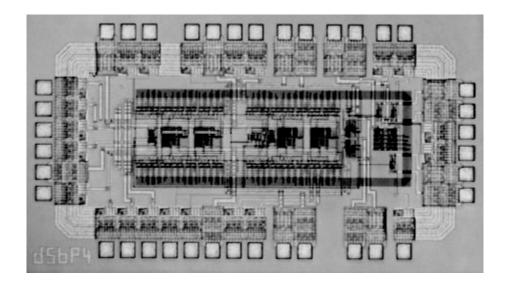

| Figure 4.31: Chip microphotograph of the fourth-order double-sampled SC bandpass sigma-delta                                                                                  |         |

| modulator                                                                                                                                                                     | 118     |

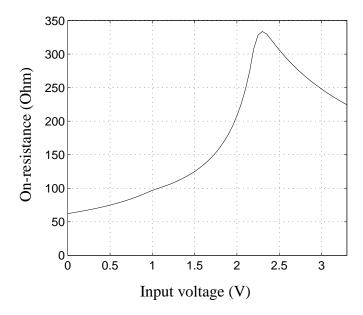

| Figure 4.32: Transmission gate switch on-resistance vs. signal level                                                                                                          | 120     |

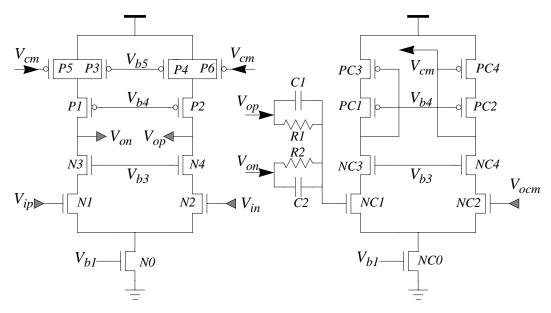

| Figure 4.33: Fully differential cascode opamp                                                                                                                                 | 121     |

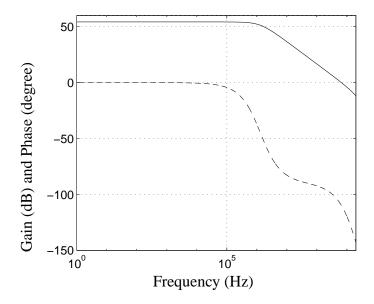

| Figure 4.34: Simulated open loop gain (solid line) and phase (dotted line) of the cascode opamp for 1 p                                                                       | F load  |

| capacitance                                                                                                                                                                   | 122     |

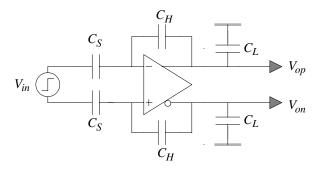

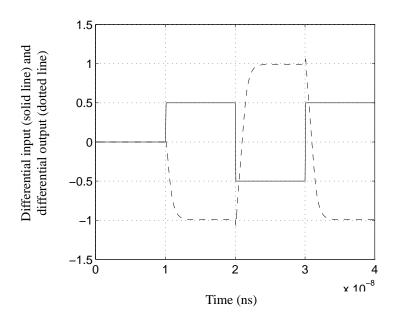

| Figure 4.35: Test structure for settling time simulation                                                                                                                      | 123     |

| Figure 4.36: Worst case settling time simulation in Eldo.                                                                                                                     | 123     |

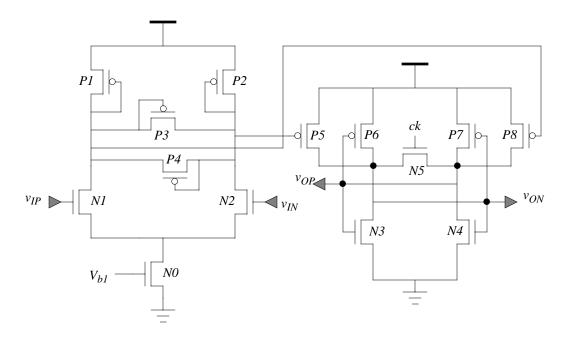

| Figure 4.37: Fully differential comparator                                                                                                                                    | 124     |

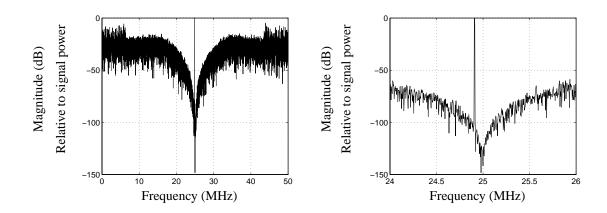

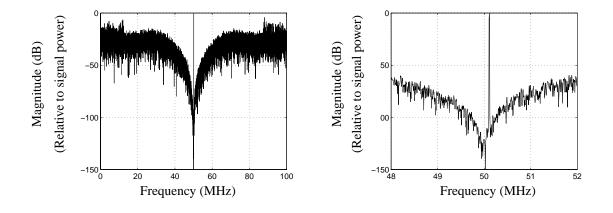

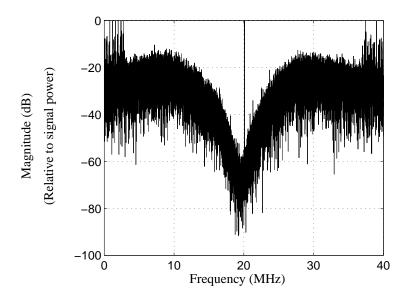

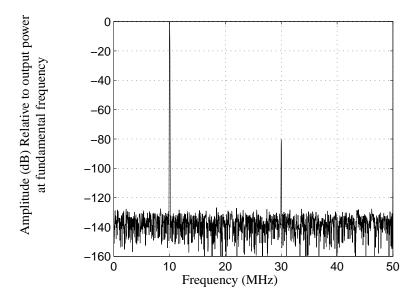

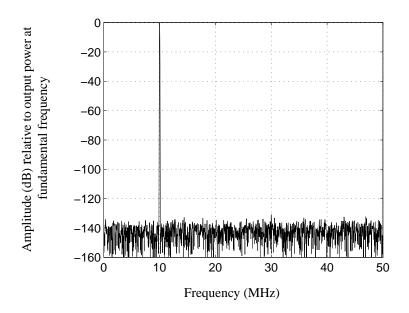

| Figure 4.38: Measured output spectrum of the fourth-order bandpass sigma-delta modulator for an in                                                                            | put     |

| signal of 10 dB below full scale                                                                                                                                              | 126     |

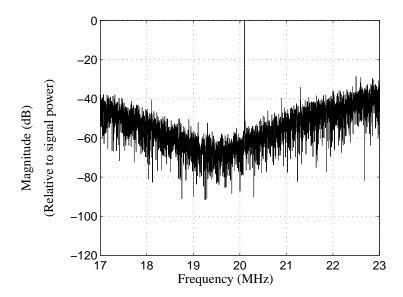

| Figure 4.39: Expanded view of the output spectrum around the notch. Note that the notch frequency is                                                                          | shifted |

| by about 500 kHz to the left (lower frequency)                                                                                                                                | 127     |

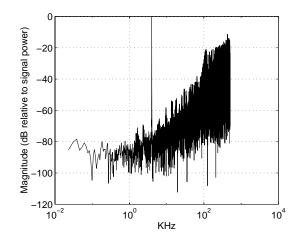

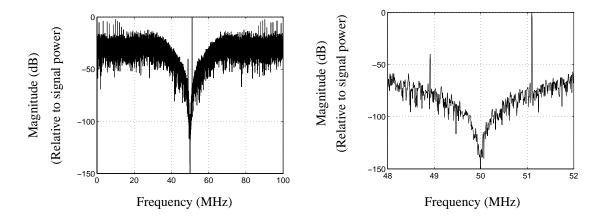

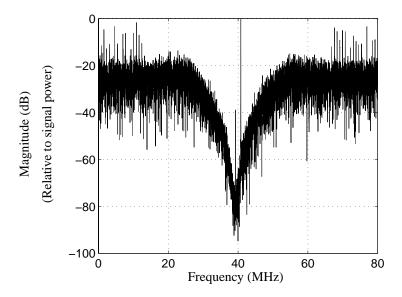

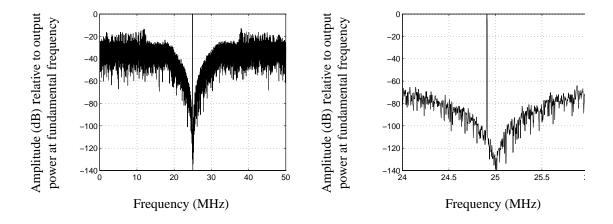

| Figure 4.40: Measured output spectrum of the double-sampled fourth-order SC bandpass sigma-delta                                                                              | ı       |

| modulator for an input signal of 10 dB below full scale. Note that image signal is about                                                                                      | 39 dB   |

| below the fundamental signal.                                                                                                                                                 | 128     |

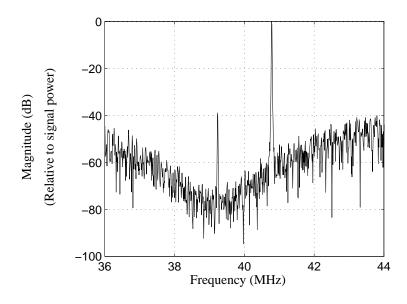

| Figure 4.41: Expanded view of the output spectrum around the notch. Note that the notch frequency is                                                                          | shifted |

| by about 1 MHz.                                                                                                                                                               | 128     |

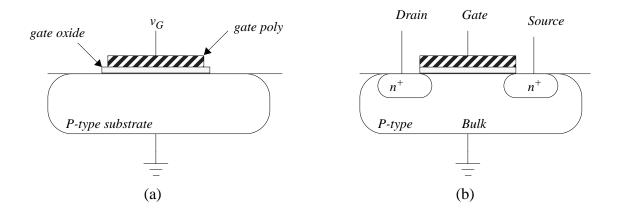

| Figure 5.1: Structure of (a) a MOS capacitor and (b) an nMOSFET transistor                                                                                                    | 131     |

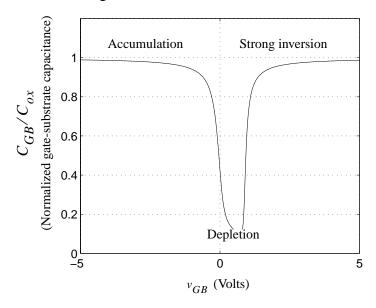

| Figure 5.2: Analytical C-V characteristics of an nMOSFET transistor                                                                                                           | 132     |

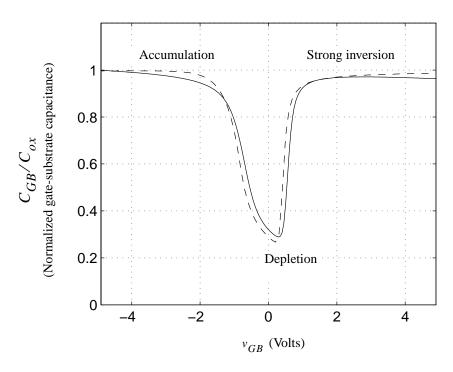

| Figure 5.3: Measured (solid line) and simulated (dashed line) C-V plot of an nMOSFET                                                                                          | 134     |

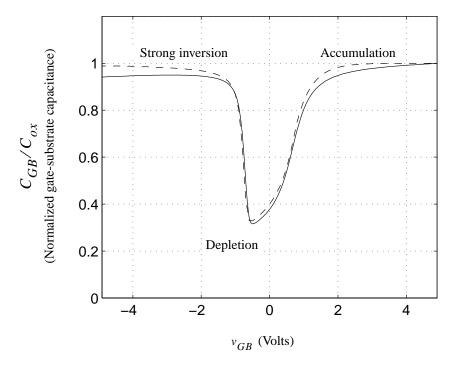

| Figure 5.4: Measured (solid line) and simulated (dashed line) C-V plot of a pMOSFET                                                                                           | 134     |

| Figure 5.5: Simulated C-V characteristics of a low-Vt natural nMOSFET (dashed line) and a threshold                                                                           | old     |

| adjusted nMOSFET (solid line)                                                                                                                                                 | 136     |

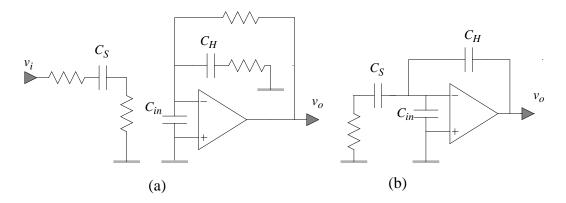

| Figure 5.6: A single-ended SC amplifier                                                                                                                                       | 137     |

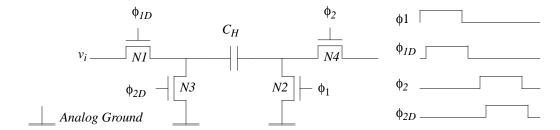

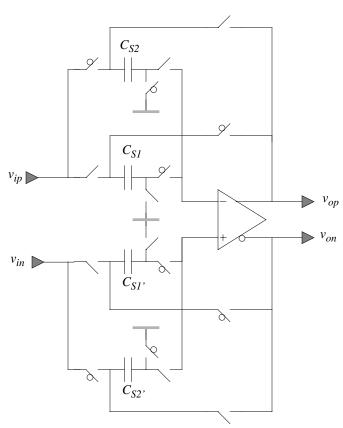

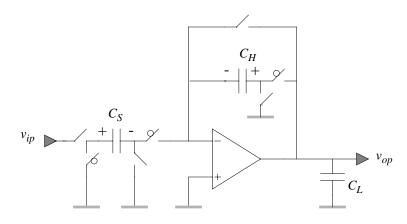

| Figure 5.7: SC delay cell using pMOSFET capacitors                                                                                                                            | 140     |

| Figure 5.8: Output spectrum of the fully differential SC gain stage, Figure 5.7, during                                                                                       | 141     |

| Figure 5.9: Output spectrum of the fully differential SC unity gain stage, Figure 5.7, during f1                                                                              | 142     |

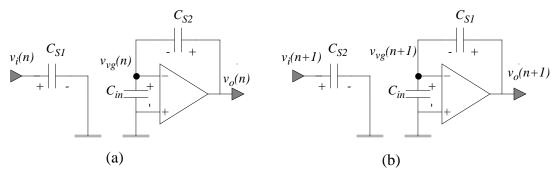

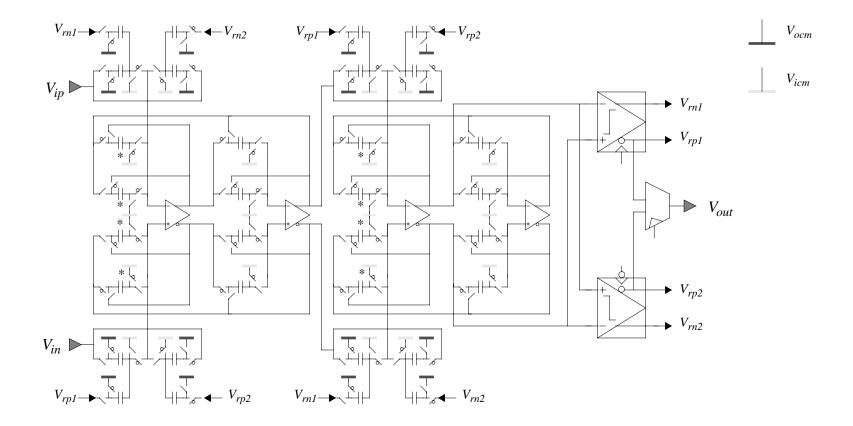

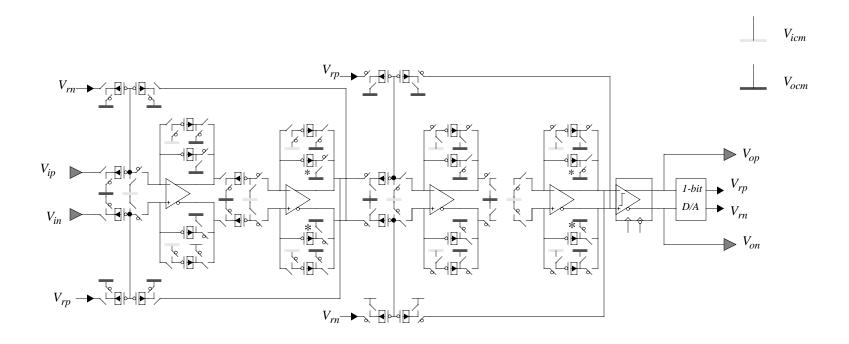

| Figure 5.10: A fourth-order bandpass sigma-delta modulator using pMOSFET capacitors                                                                                           | 143     |

| Figure 5.11: Output spectrum of the fourth order SC handness sigma delta modulator of Figure 5.10                                                                             | for an  |

|              | input signal of 6dB below full scale                                | 144 |

|--------------|---------------------------------------------------------------------|-----|

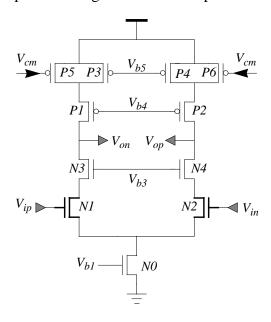

| Figure 5.12: | : A fully differential cascode opamp                                | 144 |

| Figure B.1:  | Measured ID (A) and Gm (A/V) versus VGS (V) for "natural" nMOSFET   | 154 |

| Figure B.2:  | Measured  ID (A)  and Gm (A/V) versus VGS (V) for "natural" pMOSFET | 154 |

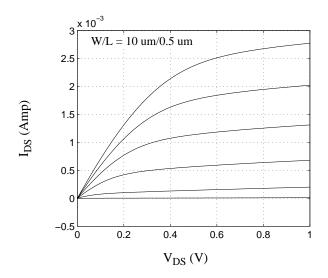

| Figure B.3:  | Measured nMOSFET IDS-VDS characteristics. IDS ~ (VGS-Vt)1.27        | 155 |

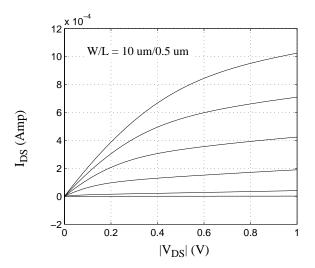

| Figure B.4:  | Measured pMOSFET IDS-VDS characteristics. IDS ~ (VGS-Vt)1.32        | 155 |

## **List of Tables**

| Table 1.1: SIA semiconductor technology roadmap                         | 1   |

|-------------------------------------------------------------------------|-----|

| Table 2.1: CMOS scaling schemes                                         | 8   |

| Table 2.2: A guideline for CMOS scaling                                 | 8   |

| Table 3.1: On-resistance of switches with W=10mm                        | 71  |

| Table 3.2: Dimension of MOSFETs used in the opamp of Figure 3.24        | 74  |

| Table 3.3: Simulated opamp performance for a 1 pF load capacitance      | 75  |

| Table 3.4: Transistor sizes for the comparator                          | 76  |

| Table 4.1: Some MOSFET parameters in HCMOS5a process                    | 118 |

| Table 4.2: Target specification for the bandpass SD modulator           | 119 |

| Table 4.3: Transistors sizes used in the opamp                          | 121 |

| Table 4.4: Transistor sizes used in the CMFB circuit                    | 121 |

| Table 4.5: Simulated characteristics of opamp for 1 pF load capacitance | 124 |

| Table 4.6: Comparator transistor sizes                                  | 125 |

| Table 5.1: nMOSFET capacitance voltage coefficients                     | 135 |

| Table 5.2: pMOSFET capacitance voltage coefficients                     | 135 |

| Table 5.3: Simulated characteristics of opamp for 1pF load capacitance  | 145 |

## **List of Abbreviations**

A/D Analog-to-Digital

ASIC Application Specific Integrated Circuit

BiCMOS Bipolar and Complementary Metal Oxide Semiconductor

CE Constant Electric Field

CML Current Mode Logic

CMOS Complementary Metal Oxide Semiconductor

CV Constant Voltage

DC Direct Current

DR Dynamic Range

DRAM Dynamic Random Access Memory

FE Forward Euler

$HD_k$   $k^{th}$  harmonic distortion

IF Intermediate Frequency

LDI Lossless Discrete Integrator

LDD Lightly Doped Drain

LT Low Temperature

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NTF Noise Transfer Function

nMOSFET n-channel Metal Oxide Semiconductor Field Effect Transistor

opamp operational amplifier

OSR Oversampling Ratio

OTA Operational Transconductance Amplifier

pMOSFET p-channel Metal Oxide Semiconductor Field Effect Transistor

QCV Quasi-Constant Voltage

SC Switched-Capacitor

SCE Short-Channel Effect

SI Switched-Current

SNR Signal to Noise Ratio

SNDR Signal to Noise+Distortion Ratio

STF Signal Transfer Function

STG Series Transmission Gate

TG Transmission Gate

TTL Transistor-Transistor Logic

UGBW Unity-gain Bandwidth

VLSI Very Large Scale Integration

$\Sigma\Delta$  Sigma-Delta

# **List of Symbols**

| Absolute value                      |

|-------------------------------------|

| opamp DC gain                       |

| Gate-bulk capacitance of MOSFET     |

| Gate-source capacitance of MOSFET   |

| Specific gate capacitance of MOSFET |

| Conduction band edge                |

| Silicon bandgap energy              |

| Valence band edge                   |

| Quantization noise                  |

| Frequency in Hz                     |

| Center frequency                    |

| Sampling frequency                  |

| Drain-source conductance            |

| MOSFET transconductance             |

| s-domain transfer function          |

| z-domain transfer function          |

| Drain current                       |

| Input current                       |

| Output current                      |

| MOSFET subthreshold off-current     |

| CMOS technology scaling factor      |

| Boltzman's constant                 |

|                                     |

L MOSFET channel length

$m(\omega)$  Magnitude error frequency response

N<sub>A</sub> Acceptor impurity density

*n* Subthreshold slope factor

$n_0$  Quantization noise in signal band

$\hat{Q}$  Fixed charge density

$R_{on}$  MOSFET drain-source on-resistance

$r_j$  MOSFET junction depth

S Subthreshold swing factor

$S \Big|_{y}^{x}$  Sensitivity of x to variation in y

T Clock period

*T* Temperature

$t_D$  Delay time

$t_{ox}$  Gate oxide thickness

$V_{BE}$  Base-Emitter voltage

$V_{DD}$  Power supply voltage

*V<sub>FB</sub>* Flat-band voltage

$V_{\it icm}$  Input common-mode voltage

$V_{\it ocm}$  Output common-mode voltage

$V_{on}$  MOSFET gate over-drive voltage (on-voltage)

$V_t$  MOSFET threshold voltage

$V_{\it tn}$  nMOSFET threshold voltage

$V_{tp}$  pMOSFET threshold voltage

$\overline{v_n}$  RMS noise voltage

$v_D$  Drain voltage

v<sub>id</sub> Differential input voltage

*v<sub>in</sub>* Negative input voltage

*v*<sub>ip</sub> Positive input voltage

$v_{od}$  Differential output voltage

*v*<sub>on</sub> Negative output voltage

*v<sub>op</sub>* Positive output voltage

$v_S$  Source voltage

W MOSFET channel width

z<sup>-1</sup> Sampled-data representation of delay  $(z^{-1} = e^{-j\omega T})$

α Velocity saturation index

$\alpha_1$  First-order voltage coefficient of capacitance

$\alpha_2$  Second-order voltage coefficient of capacitance

$\beta$  MOSFET transconductance parameter ( $\beta = \mu C_{ox}W/2L$ )

β Feedback factor

$\varepsilon_{ox}$  Oxide dielectric constant

$\varepsilon_{si}$  Silicon dielectric constant

$\phi_B$  Bulk potential

$\phi_F$  Fermi potential

$\phi_{ms}$  Metal-silicon work function difference

$\phi_n$  Clock phase n

$\phi_t$  Thermal voltage

γ Body effect coefficient

μ Mobility

$\mu_n$  Electron mobility

$\mu_p$  Hole mobility

$\theta(\omega)$  Phase error frequency response

$\omega_u$  Unity-gain bandwidth

$\omega_0$  Cut-off frequency (-3dB)

# Chapter 1

## Introduction

#### 1.1 Motivation

Higher speed and higher density are the main benefits of CMOS VLSI technology and are achieved by shrinking the feature size of the MOSFET devices. In the past, Constant Voltage (CV) scaling has been used for CMOS (down to 0.5 μm) to achieve higher performance and to maintain supply voltage compatibility. However, as MOSFET miniaturization reaches to deep submicron sizes (0.5 μm and below), supply voltage scaling based on Quasi-Constant Voltage (QCV) scaling must be adopted to assure reliability [Kakumu90]. Hot carrier effects and gate oxide breakdown are the two important reliability factors determining how high power supply voltage can be. The Semiconductor Industry Association (SIA) roadmap (Table 1.1) predicts a supply voltage of 0.9 V for semiconductors by the year 2010 [SIA94].

| Year                     | 1995 | 1998 | 2001 | 2004 | 2007 | 2010 |

|--------------------------|------|------|------|------|------|------|

| Feature size (µm)        | 0.35 | 0.25 | 0.18 | 0.13 | 0.1  | 0.07 |

| Power supply voltage (V) | 3.3  | 2.5  | 1.8  | 1.5  | 1.2  | 0.9  |

Table 1.1: SIA semiconductor technology roadmap

The move toward lower supply voltages is also fueled by low-power battery powered portable devices [Thomas93]. An ideal power supply for a battery powered system is a single-cell (1.2 V - 0.9 V) off-the-shelf battery.

Integrated circuits are moving increasingly into the mixed-signal world where more parts of a system are implemented on a single chip. Performance and density of digital circuits are expected to follow the famous Moore's law—achieving a 2X increase in circuit density and a slower rate of (1.4-1.2)X increase in circuit speed every three years. Energy per operation in digital circuits ( $E \sim CV^2$ ) is also reduced due to supply voltage scaling in deep submicron CMOS. However, lowering the supply voltage directly reduces the signal swing in analog circuits, which in turn makes the design of wide dynamic range mixed-signal circuits a challenge. This raises the following question:

#### • Will mixed-signal supply voltage follow the digital supply voltage down to 1 V?

In deep submicron CMOS ( $L < 0.5~\mu m$ ), the charge carriers' velocity will be saturated at the pinch-off point in the channel and as a result the classical quadratic saturation current becomes  $I_{dsat} \sim \left(v_{GS} - V_t\right)^{\alpha}$ , where  $\alpha = 1.3$  to 1.4 instead of 2 [Hu94]. Therefore, 1.4X circuit speed improvement every generation will slow down to about 1.2X, leading to another question:

#### • What are the circuit techniques to maintain a high dynamic range at high speed?

Analog circuits are usually implemented using Switched-Capacitor (SC) techniques because of their high circuit accuracy. Traditionally, SC circuits are implemented in analog CMOS processes where linear double poly capacitors are available. However, the driving forces behind the CMOS technologies are DRAMs and microprocessors which do not require a double-poly process. The next question is:

#### • Can linear SC circuits be implemented in a standard digital CMOS process?

These questions form the core of the research conducted in this thesis.

#### 1.2 Thesis Objectives

This thesis is concerned with the three key issues mentioned above, namely: low voltage, high speed, and the implementation of linear SC circuits in a digital CMOS process. Through analysis and some preliminary experimental circuits it will be shown that SC mixed-signal circuits will scale down to 1 V.

Low voltage: To demonstrate the feasibility of 1 V mixed-signal circuits, low-threshold

MOSFET transistors are required. A 1 V CMOS process technology is developed as a subset of a 0.5  $\mu$ m n<sup>+</sup>/p<sup>+</sup> dual poly gate CMOS process. In this process, natural threshold voltage MOSFETs are optimized to have a  $V_t$  of about 200 mV . A first-order voice-band SC  $\Sigma\Delta$  modulator is implemented in this process and operates at 1 V power supply.

**High speed**: Low-voltage operation is known to compromise speed unless the technology shrink is in proper relation to the supply voltage. Two new high-speed bandpass  $\Sigma\Delta$  modulators are implemented in a 3 V 0.5 μm CMOS process to verify their performance and functionality.

Linear SC design in a digital CMOS process: MOSFET capacitors biased in strong inversion or accumulation regimes can be used to replace linear capacitors. A telescopic opamp with different input and output common mode voltages is shown to be suitable for this purpose. Also described is the design of a fourth-order SC bandpass  $\Sigma\Delta$  modulator using pMOSFET transistors, biased in strong inversion, as linear capacitors.

The benchmark circuits are chosen to be  $\Sigma\Delta$  modulators for the following two reasons. First, a  $\Sigma\Delta$  modulator is a typical mixed-signal circuit with enough complexity to test the technology and to demonstrate the achievable performances. It contains important analog cells such as opamps, comparators and switches as well as some digital gates including inverters, NORs, and a D-type flip-flop. Second,  $\Sigma\Delta$  modulators are widely used as precision Analog-to-Digital (A/D) converters and are becoming popular in A/D conversion of narrow-band signals at Intermediate Frequencies (IF) in radio receiver circuitry.

#### 1.3 Contributions

Contributions of this work include:

- Proposed and verified suitability of low- $V_t$  natural MOSFETs for 1 V mixed analog/digital applications.

- Compared Switched Capacitor (SC) and Switched Current (SI) analog techniques for low-voltage applications.

- Analyzed low-voltage SC circuits using low-V<sub>t</sub> MOSFETs.

- Proposed low-leakage series transmission gate and composite switches.

- Demonstrated a technique for exploiting the short-channel effects to obtain low-voltage switches.

- Implemented a high-speed architecture for bandpass  $\Sigma\Delta$  modulator.

- Developed a novel double-sampled bandpass  $\Sigma\Delta$  modulator.

- Designed a fourth-order SC bandpass ΣΔ modulator in a standard digital CMOS process.

#### 1.4 Thesis Outline

**Chapter 1** provides an introduction.

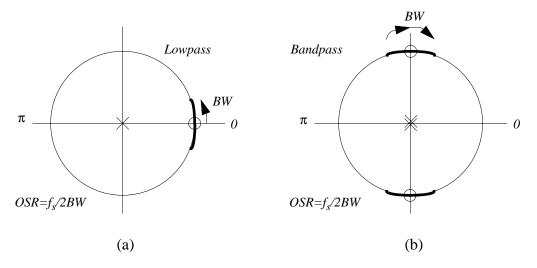

Chapter 2 starts with an examination of CMOS scaling in deep submicron geometries which require supply voltage scaling down to 1 V. Theoretical limits on low-voltage digital and analog CMOS due to circuit topology are discussed and some recent work in this area is reviewed. Oversampling and noise-shaping are then briefly overviewed and a simple mapping of lowpass  $\Sigma\Delta$  to bandpass  $\Sigma\Delta$  [Jantzi] is described. High-speed SC bandpass  $\Sigma\Delta$  modulator techniques are also presented. Next, the Switched-Current (SI) analog circuit technique [Hughes89] is introduced and methods of implementing SC circuits in a digital CMOS process are discussed. Finally, a comparative study of SC and SI for low-voltage applications is presented. It is concluded that the SC technique is preferred in low-voltage circuits from a dynamic range point of view.

In Chapter 3, low-voltage SC circuit design using low- $V_t$  MOSFETs is considered. First, two methods of achieving low- $V_t$  MOSFETs in current CMOS processes are proposed. The impact of subthreshold leakage current on the accuracy of the SC circuit is then analyzed. Methods of reducing the subthreshold leakage through analog switches are discussed next and two new switch topologies (series transmission gate and composite switch) addressing this problem are presented. Finally, two experimental circuits, a 2.25 V  $\Sigma\Delta$  modulator using short-channel MOSFETs and a 1 V  $\Sigma\Delta$  modulator using low- $V_t$  natural MOSFET are discussed.

**Chapter 4** begins by examining motivations for a high-speed bandpass  $\Sigma\Delta$  modulator. A

high-speed fourth-order SC bandpass  $\Sigma\Delta$  modulator is discussed, followed by presentation of a double-sampled SC bandpass  $\Sigma\Delta$  modulator. Fully differential circuit implementations of both modulators in a 3 V 0.5  $\mu$ m analog CMOS process are described and measured results are presented.

Chapter 5 describes a SC circuit technique employing MOSFET capacitors biased in strong inversion as linear capacitors. Distortion caused by capacitor non-linearity in a SC amplifier is analyzed. Then, the design of a fourth-order bandpass  $\Sigma\Delta$  modulator using a pMOSFET transistor as a linear capacitor is described.

**Chapter 6** draws the thesis conclusions and proposes future work.

Appendices which provide some additional information on MOSFET equations used in this thesis and measured characteristics of natural MOSFETs are also included.

# Chapter 2

# **Impacts of CMOS Scaling on Performance of Mixed-Signal Circuits**

#### 2.1 Introduction

The scaling of CMOS technology in the deep submicron regime is expected to continue providing faster and denser devices. In section 2.2, CMOS scaling is reviewed along with the fact that, for device reliability, the supply voltage is being scaled down in deep submicron technologies. The power supply voltage of 0.1 µm CMOS technology is expected to be about 1 V [Davari95]. Along with the power supply, the threshold voltage of MOSFETs must be scaled down to achieve high-speed circuits. Limits on supply voltage scaling for mixed-signal circuits are considered in section 2.3; some current research in the area of low-voltage digital and analog circuits is also presented. The impact of reducing the supply voltage on power dissipation of digital and analog circuits is discussed next. In section 2.4,  $\Sigma\Delta$  modulators, which are the benchmark circuits in this thesis, are introduced and high-speed bandpass SC  $\Sigma\Delta$  modulators reported in the literature are discussed. Most advanced CMOS processes are developed to support memory and digital circuits. Thus, mixed-signal circuits that are realizable in a standard digital CMOS process are desired. Analog SI and SC circuit techniques that allow mixedsignal circuits to be implemented in a digital CMOS process are discussed in section 2.5. Finally, a comparative study of SC and SI sampled-data analog circuit techniques is presented in section 2.6. It will be seen that SC has advantages over SI for low-voltage design.

#### 2.2 CMOS Scaling

The scaling of CMOS technology is achieved by reducing the dimensions of MOSFET transistors by a factor of k (k > 1). The original Constant Electric-field (CE) scaling law proposed by Dennard [Dennard74] involved supply voltage scaling as well as scaling all the device dimensions to preserve the same electric-field in the scaled-down device. A constant electric-field in the substrate is obtained by increasing device-well doping concentrations in the smaller devices. The CE scaling scheme improves the device density by  $k^2$ , reduces the gate delay by k, and lowers power dissipation by  $k^2$  thus maintaining a constant power density.

Drawbacks of CE scaling are the departure from standard power supply voltage, problems with MOSFET threshold voltage scaling, and degradation in analog signal swing. Therefore, in the past (down to  $0.5~\mu m$  technology) a Constant Voltage (CV) scaling rule has been used for CMOS to maintain a supply voltage of 5 V and to achieve higher circuit performance; gate delay is reduced by  $k^2$  in a CV scaling. However, in CV scaling the higher electric field causes a reliability hazard due to hot carriers and gate oxide breakdown. A higher electric field in deep submicron devices also brings about carrier velocity saturation, which causes speed improvement to become linearly proportional to k (similar to CE scaling). Another drawback of CV scaling is an increase in power dissipation density which is proportional to  $k^3$ .

A compromise between CV and CE scaling schemes is a general scaling theory called Quasi-Constant Voltage (QCV) scaling. In a QCV scaling, power supply voltage is reduced at a slower rate of approximately  $\sqrt{k}$ . In Table 2.1, various scaling schemes and their effects on MOSFET device characteristics are summarized.

Studies of CE, CV, and QCV scaling for mixed-signal circuits in high-micron [Wong83] and submicron [Sano88] CMOS technologies have shown that QCV scaling is close to an optimum scaling scheme.

#### 2.2.1 CMOS Scaling in the Next Decade

Recently, Davari published a guideline for CMOS scaling in the next decade for digital circuits [Davari95]. A summary of this guideline is produced in Table 2.2. Two different

| Parameters                              | CE               | CV               | QCV                |

|-----------------------------------------|------------------|------------------|--------------------|

| Lateral dimensions (L)                  | 1/k              | 1/k              | 1/k                |

| Gate oxide thickness (t <sub>ox</sub> ) | 1/k              | 1/k              | $1/\sqrt{k}$       |

| Doping concentration                    | k                | $k^2$            | k <sup>1.5</sup>   |

| Supply voltage (V)                      | 1/k              | 1                | $1/(\sqrt{k})$     |

| Electric field                          | 1                | k                | 1                  |

| Current (I)                             | 1/k              | k                | 1/k                |

| Area (A)                                | 1/k <sup>2</sup> | 1/k²             | $1/k^2$            |

| Capacitance (C=Aɛ/t <sub>ox</sub> )     | 1/k              | 1/k              | 1/k <sup>1.5</sup> |

| Gate delay (VC/I)                       | 1/k              | 1/k <sup>2</sup> | 1/k                |

| Power dissipation (VI)                  | 1/k <sup>2</sup> | k                | $1/k^{1.5}$        |

| Power density (VI/A)                    | 1                | $k^3$            | $\sqrt{k}$         |

| Energy dissipation (CV <sup>2</sup> )   | $1/k^3$          | 1/k              | k <sup>2.5</sup>   |

Table 2.1: CMOS scaling schemes

power supply voltages are recommended for each generation of deep submicron technology: one for high-performance (HP) circuits and another one for low-power (LP) circuits.

| Year                     | 1995    | 1998    | 2001    | 2004    |

|--------------------------|---------|---------|---------|---------|

| Supply voltage (HP/LP) V | 3.3/2.5 | 2.5/1.5 | 1.5/1.0 | 1.2/1.0 |

| Channel length (µm)      | 0.35    | 0.25    | 0.18    | 0.13    |

| Oxide thickness (nm)     | 9       | 6       | 3.5     | 2.5     |

Table 2.2: A guideline for CMOS scaling

This guideline is in agreement with the SIA technology roadmap for semiconductors presented in Chapter 1. By the year 2004, the power supply voltage is predicted to be scaled down to 1.2 V for high-performance circuits and 1 V for low power applications.

Supply voltage scaling in CMOS, undertaken to maintain reliability, causes severe speed performance degradation unless the MOSFET threshold voltage  $(V_t)$  is scaled down.

Circuit speed suffers because it is proportional to transconductance  $(g_m)$  and for a fully turned- on MOSFET (i.e.,  $v_{GS} = V_{DD}$ ) the transconductance is  $g_m \sim V_{DD} - V_t$ .

#### 2.2.2 V<sub>t</sub> Scaling Issues

A MOSFET transistor biased below threshold voltage  $(v_{GS} \le V_t)$  operates in the weak inversion mode where drain current is exponentially dependent on the value of  $v_{GS} - V_t$  (Appendix A). The subthreshold off-current (for  $v_{GS} = 0$ ) is given by the following simplified equation:

$$i_{off} = I_{D0} \frac{W}{L} 10^{-V_t/S}, (2-1)$$

where S is the subthreshold swing and is given by

$$S = n \frac{kT}{q} ln(10) \tag{2-2}$$

and typically  $n \approx 1.4$ .

#### Non-Scalability of Subthreshold Swing

As can be seen from (2-2), subthreshold swing does not scale with technology scaling. Therefore, the main limitation of  $V_t$  scaling is due to the non-scalability of S.

At room temperature, S has a typical value of 80 mV/decade for bulk CMOS, and increases to about 100 mV/decade at  $85^{\circ}C$ . Reducing the threshold voltage of MOSFETs by 100 mV increases the subthreshold off-current by an order of magnitude. Higher off-current increases the standby power dissipation in digital circuits and limits the accuracy of the analog SC circuits.

**Digital circuits:** In digital CMOS circuits the total power consumption expression is

$$P = p_{0 \to 1} f C_L V_{DD}^2 + i_{off} V_{DD} + i_{sc} V_{DD}$$

(2-3)

where  $p_{0 \to 1}$  is the activity factor, f is the clock frequency,  $C_L$  is the load capacitance,  $V_{DD}$  is the supply voltage, and  $i_{sc}$  is the short circuit current during each input transition when both nMOSFET and pMOSFET are temporarily on.

Lowering the  $V_t$  increases the off-current and the second term in the above equation will

rise. However, low- $V_t$  MOSFETs allow operation at a lower  $V_{DD}$  without sacrificing speed performance. A reduced  $V_{DD}$  decreases the dynamic power consumption, the first term in (2-3).

Several studies [Liu93] [Burr91] have shown that a significant power saving is achieved by operating at very low supply voltages (as low as 200 mV) using low- $V_t$  MOSFETs, while preserving circuit speed.

Analog circuits: Analog switches in SC and SI circuits must exhibit a low on-resistance when closed and very low leakage current when opened. At a low supply voltage, low- $V_t$  MOSFET are suitable as switches due to their low on-resistance. However, low- $V_t$  switches are leaky and limit the precision of the analog circuits. In Chapter 3, the impact of leakage through analog switches is analyzed and some solutions are proposed.

A sharper subthreshold slope (i.e., a lower value of S) is obtained by reducing n, or T, or both in (2-2). The lowest possible value for n is achieved in a CMOS on Silicon-on-Insulator (SOI) process where n=1. The corresponding value of S is 57.5 mV/decade at room temperature. Low-Temperature (LT) CMOS is another method of scaling the subthreshold swing. Operation at liquid nitrogen temperature (77 K) reduces S by a factor of four to about 14.5 mV/decade.

Both SOI and LT-CMOS furnish a better  $V_t$  scaling and are promising technologies for very low-voltage deep sub-0.1  $\mu$ m CMOS processes.

#### Threshold Voltage Fluctuation

Another limitation of  $V_t$  scaling is based on the fundamental variability of the threshold voltage due to process variations. Fluctuation in  $V_t$  is mainly due to random dopant and channel length variations. For a normally distributed threshold voltage, the standard deviation due to random dopant concentration variation is

$$\delta V_t = \frac{q}{2C_{ox}} \sqrt{\frac{\pi N_A}{2}} (WL)^{-3/8} (X_D)^{1/4} , \qquad (2-4)$$

where  $N_A$  is the doping density, L and W are the channel length and width of the transistor, and  $X_D$  is the depletion width [Keyes75].

Recent studies based on measurements [Mizuno93] and simulations [Nishinohra92] [Wong93] show that  $V_t$  variation due to dopant fluctuation is proportional to  $1/\sqrt{L}$ , in agreement with (2-4), and increases as channel length is reduced. In [Nishinohra92], 2-D and 3-D simulations indicate that  $\delta(\Delta V_t)$  is expected to increase from 10 mV, for 1  $\mu$ m technology, to about 30 mV for a 0.1  $\mu$ m technology.

Temperature variation also changes the  $V_t$  by approximately 1.25 mV/°C [Chen90]. For an industrial temperature range of -50°C to 85°C, the total threshold shift due to temperature alone is about 170 mV.

In low- $V_t$  processes, threshold voltage changes due to process variations and temperature have a big impact on speed and standby power dissipation. For instance speed performance variation (based on quadratic equation formulae given in Appendix A) due to a  $\pm 100$  mV change in  $V_t$  is about  $\pm 2.5$ % in a 5 V process with  $V_t = 0.8$  V, and rises to  $\pm 12$ % in a 1 V process with  $V_t = 0.2$  V. Assuming  $i_{DS} = 1$   $\mu$ A at  $v_{GS} = V_t$  and S = 100 mV/decade, the highest off-current in the above example would be 100 fA for the 5 V high- $V_t$  and 10 nA for the 1 V low- $V_t$  processes, respectively. Such a large impact on speed and standby power dissipation due to threshold variation in a low- $V_t$  scenario is intolerable and circuit techniques to address this problem are discussed briefly here.

**Multi-threshold voltage:** A process with multiple threshold voltage transistors offers circuit design flexibility at the cost of additional threshold adjust masks and an implants. Low- $V_t$  transistors can be used for circuit speed and high- $V_t$  transistors can be used to reduce the leakage current [Shinichiro93].

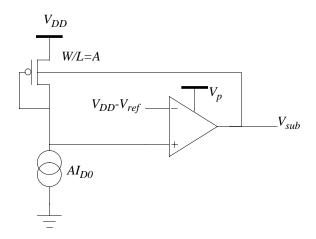

**Back-bias**  $V_t$  **adjusting:** Threshold voltage can be held constant by adjusting the substrate voltage. Figure 2.1 shows negative feedback circuitry which generates a substrate voltage to keep  $V_{tp}$  equal to a constant  $V_{ref}$  [Shoji92] [Bazarjani95d]. The amplifier in this circuit operates with supply voltages of  $V_P$  and  $V_{DD}$  where  $V_P > V_{DD}$  is the positive supply (generated by a charge-pumped circuit) to keep source/drain and bulk junctions reverse biased at all times.

A self-substrate-biasing circuit technique is also reported in [Kobayashi94] to reduce the

Figure 2.1: A negative feedback  $V_t$  adjust circuit

$V_t$  fluctuation. In [Kuroda96], a back-bias feedback circuit that adjusts  $V_t$  to 0.1 V in active mode and 0.5 V in the standby mode is discussed. A complete study of  $V_t$  adjusting circuits in SOI through back-bias along with the charge pump circuitry is under investigation [Soreefan96].

#### **Summary**

Supply and threshold voltages of future deep submicron CMOS technologies are being scaled down. Reducing the threshold voltage increases the off-current due to non-scalability of subthreshold swing, S, limiting the minimum  $V_t$ .

## 2.3 Low-Voltage Mixed-Signal Design

Low-voltage micropower circuit techniques were developed in the late 1960s and early 1970s for electronic wristwatches. These circuits had to operate from a single cell 1.35 V mercury or 1.5 V silver oxide battery. The operating frequencies of these circuits were typically a few kHz and their total power consumption was below 1  $\mu$ W. Other low-power applications include calculators, hearing aid devices, and pacemakers. In all these systems, the required speed performance of the circuit is low, typically less than 1 MHz.

The technology of choice for low-power applications has been CMOS due to its very low static power dissipation. Techniques to build low threshold voltage MOSFETs with  $V_t \sim 0.5-0.8 \text{ V}$  were developed in the late 1960s [Nagane69][Leuenberger69] and

methods of adjusting the threshold voltage by doping implants were successfully demonstrated by Swanson [Swanson72].

In this section, limitations to low-voltage digital and analog designs due to circuit topology are discussed and some recent research in the area of low-voltage digital and analog circuits is presented. Finally, the impact of supply voltage scaling on power consumption of digital and analog circuits is considered.

#### 2.3.1 Limits on Digital CMOS Supply Voltage Scaling

A lower limit on the supply voltage of digital circuits is set by the requirement that the voltage gain of a logic gate must be greater than unity. This condition is necessary to obtain regeneration of logic levels at the output of each gate.

In [Swanson72], MOSFET equations in weak inversion are derived and low-voltage operation of a CMOS inverter circuit is analyzed. Voltage gain of the CMOS inverter at mid-rail is found to be:  $(V_{DD}/2)(q/(nkT))$ . Thus, the minimum required supply voltage for digital CMOS is

$$V_{DD}\big|_{min} > \frac{2nkT}{q}. \tag{2-5}$$

This is the theoretical lower bound for the supply voltage of a static CMOS inverter circuit, about 50-70 mV at room temperature. Some experimental circuits that have demonstrated the validity of the above limit include: a 100 mV 11-stage ring oscillator [Swanson74], a 7-stage ring oscillator operating at 75 mV at room temperature and 27 mV at 77 °K [Burr95].

The present supply voltage of 3.3 V for CMOS is a factor of 47 larger than the theoretical limit of 70 mV found in (2-5). Therefore, a large margin for supply voltage reduction exists for CMOS.

In CMOS logic, a certain energy  $(CV^2/2)$  is stored on the gate capacitance to represent logic 1. This stored energy must be greater than the thermal noise in that capacitor. The mean thermal noise energy in a capacitor is kT/2 and in [Stein77], it is shown that for an error rate of  $10^{-19}$  the minimum energy required per operation is 165kT. Considering this energy requirement and the minimum supply voltage of (2-5), a logic operation

involves only 118 electrons.

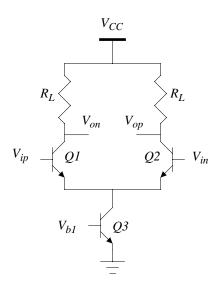

At this point, it would be interesting to see what are the minimum required supply voltage and logic swing for a bipolar circuit. A similar study for a Current Mode Logic (CML) gate, Figure 2.2, shows that exceeding unity gain requires the logic swing to be [Gray93]

$$V_{Swing} > \frac{2kT}{q}.$$

(2-6)

Figure 2.2: A basic CML inverter-buffer gate

At room temperature, the lower bound of logic swing for bipolar circuits is about 50 mV.

The lower limit of the power supply voltage for this CML gate is determined by the voltage required to turn on the input transistors Q1 and Q2 which is

$$V_{CC}\big|_{min} = V_{BE} + V_{Swing} + V_{CE}. \tag{2-7}$$

Assuming a turn-on  $V_{BE}$  of 0.75 V, a 50 mV logic swing, and a minimum  $V_{CE}$  of 0.2 V, the minimum required supply voltage for the CML gate is about 1 V.

Existing 3 V CML gates, with a logic swing of 200 mV, operate close to the limits of 1 V power supply (higher by a factor of 3) and 50 mV logic swing (higher by a factor of 4).

Thus, there is a very narrow margin for supply voltage reduction of bipolar CML gates.

#### 2.3.2 Limits on Analog CMOS Supply Voltage Scaling

This section is an investigation into the lower limit of the supply voltage for an opamp, analog switch, and current mirror—the three basic building blocks commonly used in analog SC and SI circuits.

#### Operational Transconductance Amplifier

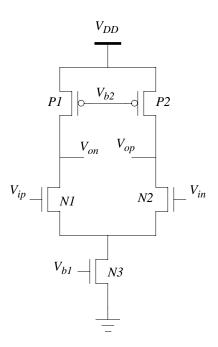

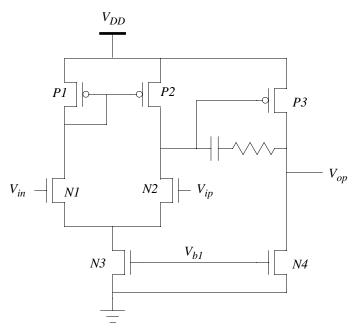

Consider a simple single-stage fully differential opamp circuit, as shown in Figure 2.3. The minimum input common-mode voltage required for the proper operation of this

Figure 2.3: A fully differential CMOS Opamp

amplifier is determined by the voltage needed to turn on the input differential pair MOSFETs, transistors N1 and N2, as given by

$$V_{icm}\Big|_{min} = V_{tn1} + V_{on1} + v_{DS3}.$$

(2-8)

Here,  $V_{icm}$  is the input common-mode voltage,  $V_{tn1}$  is the threshold voltage of the transistor M1,  $v_{DS3}$  is the drain-source voltage of the transistor N3, and  $V_{on1}$  is the gate to source overdrive voltage of the transistor N1 which is defined as

$$V_{on} = v_{GS} - V_t. (2-9)$$

The minimum  $v_{DS3}$  required to keep the transistor M3 in saturation is

$$v_{DS3}\Big|_{min} = V_{on3} = v_{GS3} - V_{t3}.$$

(2-10)

If equal threshold voltage  $V_t$  and overdrive voltage  $V_{on}$  is assumed for all the transistors and also assumed that  $V_{DD} > V_{icm}$  (i.e., charge-pump techniques are not used), from equation (2-8) the lower bound on the supply voltage of the opamp is

$$V_{DD}\Big|_{min} = V_t + 2V_{on}.$$

(2-11)

The minimum required drain-source saturation voltage depends on the MOSFET mode of operation. If the device is in weak inversion, the minimum saturation voltage required is about (4-6)kT/q [Vittoz94], which is 100-150 mV at room temperature. However, the minimum drain-source saturation voltage of MOSFETs operating in strong inversion is about 200 mV.

In a typical 0.5  $\mu$ m CMOS process, with a threshold voltage of 0.6 V, and assuming an overdrive voltage of 0.2 V, the minimum supply voltage of this opamp is 1 V. In this calculation, we ignored  $V_t$  variations due to process fluctuation, temperature changes and back-bias voltage as well as constraints on input and output common-mode levels.

In a low- $V_t$  process, the minimum supply voltage of the opamp (Figure 2.3) may be determined by the drain-source saturation voltage (or  $V_{on}$ ) and the required output voltage swing  $V_{out(swing)}$ . Assuming equal gate to source overdrive voltage for all the transistors, the minimum supply voltage is

$$V_{DD}\Big|_{min} = 3V_{on} + V_{out(swing)}. \tag{2-12}$$

For  $V_{on} = 0.2 \text{ V}$  and an output voltage swing of 0.4 V, the minimum power supply voltage is 1 V.

#### Analog Switch

An analog switch must have a full rail-to-rail signal handling capability with a low onresistance. An nMOSFET transistor used as a switch operates in triode mode with onresistance of approximately

$$R_{on} = \frac{1}{\mu C_{ox} \frac{W}{L} (v_{GS} - V_{tn})}.$$

(2-13)

A parallel nMOSFET and pMOSFET switch (transmission gate) has a rail-to-rail signal swing capability if the supply voltage is

$$V_{DD} = V_{tn,e} + V_{tp,e} + 2V_{on}. (2-14)$$

The effective threshold voltages,  $\boldsymbol{V}_{tn,\,e}$ , and  $\boldsymbol{V}_{tp,\,e}$  are given by

$$V_{te} = V_{t0}(Max) + \Delta V_{t}(T) + \Delta V_{t}(v_{SB}) . \qquad (2-15)$$

$V_t(Max)$  is the  $3\sigma$  upper value of threshold voltage due to process variations,  $\Delta V_t(T)$  and  $\Delta V_t(v_{SB})$  are the threshold voltage changes due to temperature, and the back bias respectively and are given by

$$\Delta V_t(T) = a(25 - T) (2-16)$$

$$\Delta V_t(v_{SB}) = \gamma(\sqrt{2\Phi_B + v_{SB}} - \sqrt{2\Phi_B}) . \tag{2-17}$$

Here, T is temperature in degrees Celsius, and "a" is the slope of threshold voltage as a function of temperature, which is about 1-2 mV/°C. Other parameters are the body effect coefficient  $\gamma \approx 0.5$ , the bulk potential  $\Phi_B$ , and the source to bulk voltage  $v_{SB}$ .

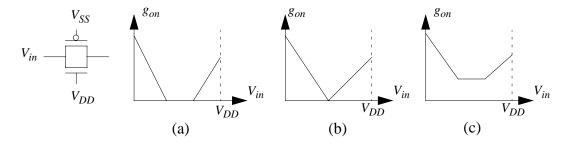

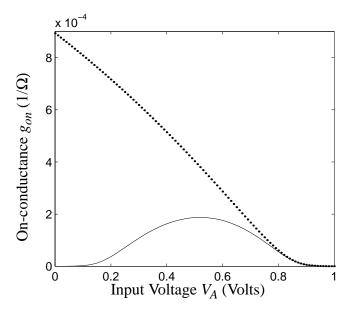

The on-conductance of a transmission gate switch as a function of signal level is shown in Figure 2.4 for three different values of power supply voltages [Vittoz93]. In this figure the

Figure 2.4: Complementary transmission gate switch on-conductance for (a)  $V_{DD} < 2V_t$ , (b)  $V_{DD} = 2V_t$ , and (c)  $V_{DD} > 2V_t$

threshold voltages of nMOSFET and pMOSFET are assumed to be equal to  $\boldsymbol{V}_t.$

In a 0.5 µm process with effective threshold voltages of 0.8 V, a supply voltage of 2 V is required to turn the transmission gate on with a minimum overdrive of 0.2 V at mid-rail.

#### Current mirror

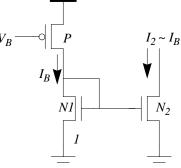

A current mirror circuit is a current gain cell that provides a weighted output copy of an input current. This circuit forms the foundation of SI signal processing and is also widely used to provide bias currents in such blocks as opamps and comparators. A simple current mirror circuit is shown in Figure 2.5. The voltage  $V_B$  generates a current  $I_B$  in the transistor P which is fed to the diode-connected transistor N1. Since transistors N2 and N1 have the same gate and source potential, their drain-source currents are related by

Figure 2.5: A simple current mirror cell

If N1 and N2 are identical transistors,  $I_2$  will mirror  $I_B$ . For accurate operation, all the transistors in the circuit must be in the saturation regime. Transistor N1 is diode connected and when it is turned on it will be in saturation with a gate (or drain) to source voltage of  $V_t + V_{on}$ . Assuming the same overdrive voltage  $(V_{on})$  for all the MOSFETs, transistor P requires a drain to source voltage of at least  $V_{on}$  to be in saturation. Thus, the minimum required supply voltage for proper operation of the simple current mirror is

$$V_{DD} > V_t + 2V_{on},$$

(2-19)

which is identical to the minimum supply voltage expression obtained for a simple opamp (2-11). Comparison of (2-11), (2-19) and (2-14) shows that switches are the bottleneck for low-voltage SC and SI operation.

#### 2.3.3 Previous Work on Low-Voltage Digital Circuits

A low-voltage digital design using standard CMOS technology, by A. Chandrakasan at Berkeley University, is described first. Then, a theoretical analysis by Dake Liu at Linkoping University, showing power savings achieved by supply voltage and threshold voltage down-scaling, is discussed. Finally, an experimental encoder-decoder system operating at 200 mV, by Jim Burr at Stanford University, is presented.

#### **Berkeley**

Power optimization at different levels of technology, circuit style, architecture, and supply voltage scaling is considered in [Chandrakasan92]. The most efficient logic family was found to be CPL (Complementary Pass-transistor Logic) if low threshold nMOSFETs are available. Logic gates must be designed for the lowest acceptable speed to save unnecessary energy loss.

In a 2  $\mu$ m CMOS technology, a power supply of 1.5 V is found to be the optimum for a large variety of cases. At such a low voltage ( $V_{DD}=2V_t$ ), circuit speed may become unacceptably low for some applications. In such cases, techniques such as parallel architecture and pipelining can be used to obtain lower latency and higher throughput rates.

#### Linkoping

An extensive study of the impacts of supply voltage and threshold voltage scaling is reported in [Liu93]. Reducing the supply voltage decreases the power consumption in CMOS logic  $(P \propto fCV^2)$ . However, speed performance  $T \propto (V_{DD})/(V_{DD}-V_t)^2$  is degraded unless the threshold voltage is scaled down.

In a 0.25  $\mu$ m CMOS technology it is shown that a factor of 40 reduction in power dissipation is possible, without any speed loss, by reducing the supply voltage from 3 V to 0.48 V and properly optimizing the MOSFETs threshold voltages from 0.7 V to  $V_{tn}=0.1$  V and  $V_{tp}=-0.01$  V.

### Stanford

Low-power research at Stanford University [Burr91] focuses on the use of near zero threshold voltage ( $\sim 100 \text{ mV}$ ) MOSFETs and selecting a power supply voltage of  $V_{DD} = 3V_t$ . The threshold voltage is fine-tuned by applying a back-bias potential.

Low threshold voltage devices allow reduced power supply voltage, which in turn decreases AC power dissipation quadratically. However, DC power consumption, due to the subthreshold leakage, increases exponentially. The minimum total power dissipation is obtained at a supply voltage where the AC component of the power dissipation and the DC power dissipation are equal. In a 2  $\mu$ m CMOS technology, 200 mV is shown to be the optimum supply voltage for digital circuits with a logic depth of 10 and an activity ratio of 0.1 . An experimental CMOS Encoder/Decoder circuit is demonstrated in [Burr94] to operate at 200 mV supply voltage.

#### 2.3.4 Previous Work on Low-Voltage Analog Circuits

Work on low-voltage analog circuits started in bipolar technology in the 1970s. Some reported 1V circuits in bipolar technology include: a bandgap voltage reference [Vittoz77], operational amplifiers [Widlar78] [Huijsing85], an active lowpass filter [Tanimoto91], and an analog current mode multiplier cell [Chan95].

Low-voltage analog circuits in CMOS (the focus of this work) started in the late 1970s [Vittoz77] and early 1980s [Vittoz80] [Krummen82]. Low-voltage analog circuits are implemented using Switched-Capacitor (SC), active-RC, and Switched-Current (SI) techniques. This section starts by describing a 1 V  $\Sigma\Delta$  A/D converter using an active-RC technique. A 1.2 V  $\Sigma\Delta$  converter implemented with the SI technique is then discussed. Finally, three papers dealing with low-voltage SC filters are presented.

#### 2.3.4.1 Low-Voltage Active-RC Circuits

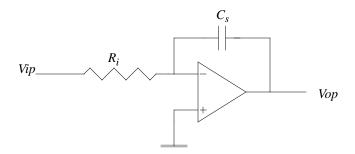

A 1 V second-order  $\Sigma\Delta$  modulator, implemented in a 0.5  $\mu$ m multi-threshold voltage CMOS technology, is reported in [Matsuya94]. Integrators in the  $\Sigma\Delta$  modulator are implemented using an active-RC technique, as shown in Figure 2.6. For an oversampling ratio of 16, this modulator has a SNDR of 51 dB and a dynamic range of 58 dB. The modulator operates at a clock frequency of 6.14 MHz (signal bandwidth of 192 kHz)

and consumes 1.56 mW at a 1 V power supply voltage.

Figure 2.6: An active-RC integrator

Since subthreshold leakage current through low- $V_t$  analog switches was the main source of concern in this design, SC implementation was ruled out. In Chapter 3 of this thesis, the impact of leakage current through analog switches on the accuracy of SC circuits are discussed and methods of reducing the subthreshold leakage are also presented.

A drawback of integrated active-RC circuits is inaccuracy in the RC time constant, because monolithic resistors and capacitors have a tolerance of more than  $\pm 15$ % and do not track each other. For lowpass  $\Sigma\Delta$  modulators, variations in the RC time constant causes a gain variation and is not critical.

#### 2.3.4.2 Low-Voltage Switched-Current Circuits

Recently [Tan95], a low-voltage second-order SI  $\Sigma\Delta$  modulator was reported which operates at 1.2 V. The circuit, however, is not a true 1.2 V part because the switches operate from a higher external supply voltage.

The circuit is implemented in a 0.8 µm digital CMOS process using a fully differential SI memory cell with a common-mode feed forward circuit. This modulator is clocked at 1 MHz and consumes 0.78 mW. The measured SNDR and SNR for an oversampling ratio of 64 are 55 dB and 51 dB respectively. Ideally, this modulator should achieve a SNDR of more than 80 dB. The low performance of this SI circuit is attributed (by the authors of the original paper) to circuit noise generated by the first current copier cell.

A review of SI technique is provided in section 2.5. In section 2.6 it will be shown that SC has some advantages over SI for low-voltage applications.

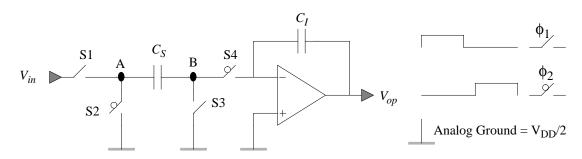

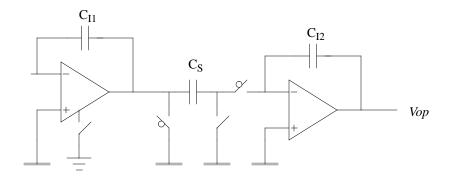

#### 2.3.4.3 Low-Voltage Switched-Capacitor Circuits

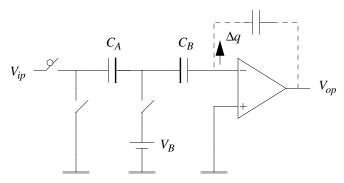

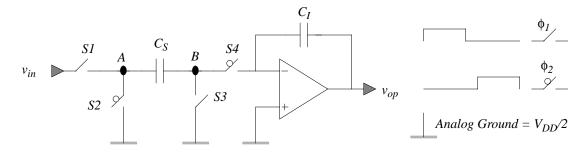

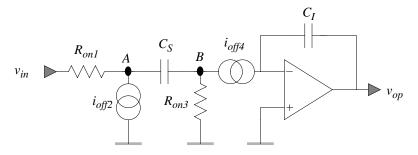

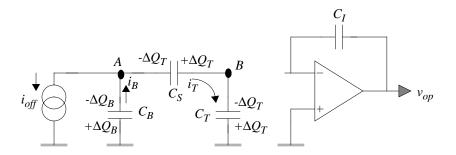

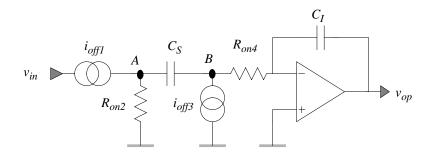

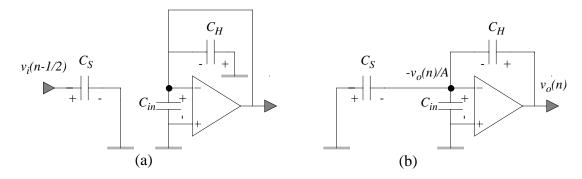

In CMOS, SC is the dominant technique for implementing analog circuits due to its high circuit accuracy and low distortion even at low supply voltages [Castello91]. For low-voltage applications, the most critical component in a SC circuit (and a SI circuit) is the transmission gate switch, which requires a gate voltage of at least  $2V_t$  for proper full swing signal handling. In SC circuits, few switches usually require rail-to-rail signal swing. For instance, in the non-inverting SC integrator of Figure 2.7 only the input switch (S1) needs to be implemented with a transmission gate, an nMOSFET and an pMOSFET in parallel. All the other switches are connected to analog ground  $V_{ag} \approx V_{DD}/2$  and thus can simply be nMOSFET transistors.

Figure 2.7: A non-inverting SC integrator and its associated 2-phase non-overlapping clock

In general, to achieve full signal transmission through a MOSFET switch with acceptable on-resistance, either the gate voltage must be increased (e.g., clock voltage multiplication) or the threshold voltage of MOSFETs must be reduced. A third solution would be to eliminate the need for switch *S*1. In the following section, the above methods of low-voltage SC design are described.

### (I) Clock Voltage Multiplication

If the supply voltage is less than  $2V_t$ , the MOSFET switches will not be able to conduct when biased at the mid-rail. Clock voltage boosting is an effective way of increasing the conductance of the MOSFET switches. This is the most commonly used technique in low-voltage SC circuits [Krummen83] [Callias89] [Castello91] [Wayne92] [Grilo96] [Au96].

A biquadratic SC lowpass filter operating at 1.5 V is reported in [Castello91] for