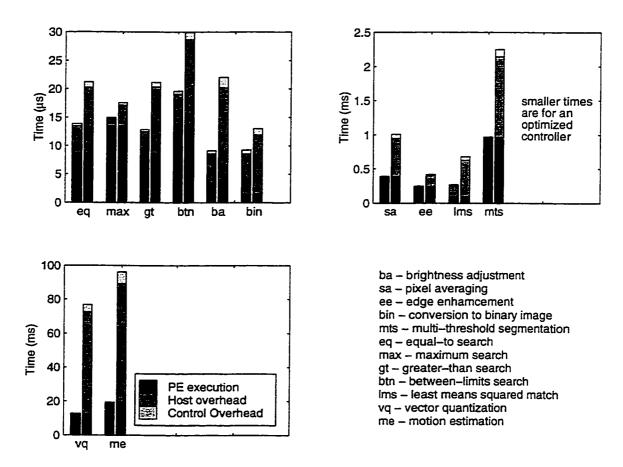

### 5.3 ISA CRAM System Prototype

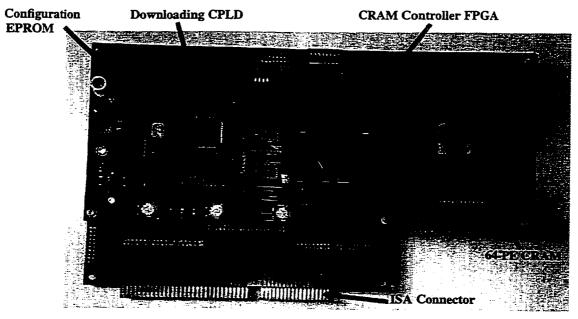

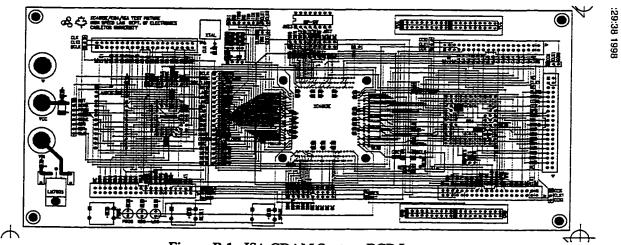

An ISA CRAM system, named CS64p1kISA, has been built. It comprises of one C64p1k CRAM chip, an ISA CRAM Controller FPGA, and the controller downloading CPLD and EPROM. It is made of two PCBs, the CRAM system PCB described in Section 5.2.3 (Appendix B) and a very small PCB that consists of an ISA male connector only. The ISA connector PCB is attached to the main PCB by screws, and its ISA signals are soldered to the main PCB External Bus Header using very thin wires. Figure 5.4 shows a photograph of the CS64p1kISA ISA PC card.

The system has been tested in a PC under both Linux and MSDOS. Because of problems with the software driver for the card, all routines tested on the prototype system were written in machine code (generated automatically using CRAM C++ simulator). Also, because of the small size of memory per PE and the small number of PEs, only small algorithms, especially basic arithmetic operations, were run on the system. The main objective of building the prototype was to demonstrate a working model of the CRAM concept rather than to highlight the performance advantages of CRAM. As mentioned earlier, for many applications, the performance advantage of CRAM becomes evident as the number of PEs increases. Therefore, the performance analysis of Chapter 7 is based on simulations of CRAM systems with a realistically large number of PEs.

Figure 5.4 CRAM System ISA Card

### 5.4 Summary

A VHDL synthesis design flow was used in the design of the CRAM controller in order to reduce design time and provide a generic design that can easily be targeted for implementation in different technologies. A CRAM system VHDL simulation model has been designed to allow the running of actual system assembly or machine code when testing the functionality of the controller and CRAM chips. This reduces the time of generating input test vectors and collecting test output. The simulation model consists of VHDL models of the controller, the CRAM chips, a generic host processor, and host system buses, as well as a couple of C++ tools for processing text-file models of CRAM microinstructions and CRAM/host code.

Two controller prototypes have been implemented in a Xilinx XC4013EPQ240-2 FPGA. The ISA CRAM controller, with a 192-word control store, uses 564 CLBs and runs at 14 MHz. Because of area constraints, the PCI CRAM controller was implemented with a control store of 128 words. It uses all the 576 CLBs, and runs at 10 MHz. In TSMC 0.35 µm CMOS technology, the CRAM controller has an area of just over 12000 gates (2-input NAND gate equivalents) and runs at 90 MHz (limited by the cycle time of SRAM cores). To demonstrate a working model of the whole CRAM concept, a 64-PE ISA CRAM system prototype has been built and tested in a 133 MHz Pentium PC under both Linux and MSDOS.

# Chapter 6

# **CRAM System Software Tools**

This chapter describes the high-level software tools for application programming, software development, and system simulation. Section 6.2 describes the CRAM C++ Compiler, which is a CRAM C++ library that allows the use of the standard C++ language and standard C++ compilers when writing CRAM programs. Section 6.4 describes the CRAM assembly code, and Section 6.5 briefly describes a high-level tool for developing CRAM microcode. The CRAM C++ Simulator, a tool that is used to simulate the behavior of a CRAM system, is described in Section 6.7. This is used to analyze applications, software tools, and CRAM architectural features. Apart from software tools, this chapter also discusses two other software issues: data transposition (Section 6.3) and grouping of microroutines (Section 6.6). Data transposition is used to convert the format of data between the bit-serial CRAM and the bit-parallel host computer. Microroutine grouping is used to reduce the number of microinstructions in the control store so that a smaller microprogram memory can be used.

#### 6.1 Introduction

The lowest level CRAM instructions are the control bits issued to the CRAM chip by the CRAM controller. These include the PE opcodes (COP and TTOP), as well as the control, data and address signals. These are stored as microinstructions in the CRAM controller control store, and are collectively referred to as the CRAM Machine Language.

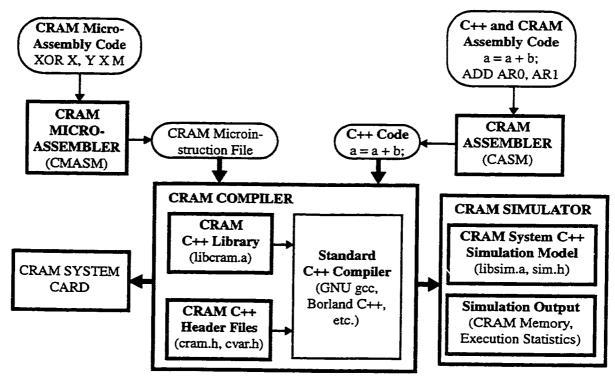

Writing application programs using the CRAM machine code requires detailed knowledge of the architecture of the CRAM chip and the controller. Also, like any other machine code, it is both tedious and slow to program using these instructions. Therefore, high-level software tools have been developed that programmers and designers can use when writing CRAM applications or other software development tools. This also includes a C++ CRAM simulator that can be used by programmers for testing and timing CRAM applications. The simulator is also a vital tool for CRAM hardware and system designers in that it allows different architectural features to be explored before committing to the actual hardware implementation. Figure 6.1 shows the relationship and use of the CRAM software tools.

Figure 6.1 CRAM System Software Tools

CRAM applications can either be written in C++ code and compiled using a standard C++ compiler, or they can use both C++ and CRAM assembly code which is preprocessed through the CRAM Assembler before compilation. The CRAM Microassembler is a high-level tool for generating CRAM microcode. Note that the VHDL simulator described in Section 5.1.6 is used primarily for verification of the behavioral and synthesized VHDL controller design and is therefore not considered as a high-level tool for use by application programmers. It is therefore not included in Figure 6.1.

# 6.2 CRAM Compiler (CRAM C++ Library)

### 6.2.1 Using a C++ Compiler

One of the most negative attributes that SIMD machines are tagged with is that they are difficult to program. Because of this, designers of most well known SIMD machines have gone to great efforts to develop very elaborate software tools for their machines. There are three major approaches that can be followed. The first is to design the programming language for the machine from scratch. An example is the programming language for STARAN [43]. The second approach is to design a dialect of a common standard programming language such as C, Pascal or Fortran. This is a popular approach in most very high performance SIMD machines. Examples of such languages include the MasPar Fortran (MPF) and MasPar C (MPC) [44], the Connection Machine C\*<sup>TM</sup> language [33], and the Terasys PIM data parallel bit C (dbc) [13]. The third approach is to use C++ as the programming language for the SIMD machine, with the addition of specialized libraries [4], [14].

The C++ programming language [45] allows creation of new classes of objects. These are actually new data types. The class constructor allows specialized initialization or operation when an object of a class is created. Such initialization might include allocating memory for the object. The class destructor is invoked when the object goes out of scope and is to be destroyed. This can be used in operations such as memory deallocation. The other important characteristic of C++ is operator overloading, which allows the use of standard C++ operators such as +, -, /, for any C++ class. By using operator overloading,

class objects can be used in expressions in exactly the same way as built-in data types. The third characteristic of C++, called inheritance, allows classes to be built from existing classes, thereby inheriting all the characteristics of the base class.

We have chosen to use C++ as the programming language for CRAM because we don't have to build a compiler, and hence the development cycle is short. It is also easier to upgrade since this only requires the addition of new classes or extension (adding new class functions, members, etc.) of existing classes. More important, C++ is easy to learn and use since many application programmers will already have used it before.

### **6.2.2 CRAM Classes (Data Types)**

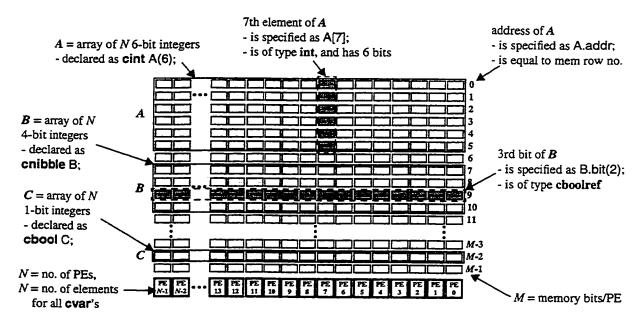

The CRAM C++ library contain classes that represent CRAM parallel integer variables. Because of the complexity of manipulating floating-point numbers in bit-serial format, and the fact that our current prototypes have very small memory per PE to consider using CRAM for floating-point operations, the design of CRAM C++ classes for parallel floating-point variables has been left for future work. Figure 6.2 shows the physical definitions and characteristics of CRAM data types. The following sections describe the CRAM classes.

Figure 6.2 Definitions of CRAM Data Types

- cvar: The basic class from which all CRAM classes are derived is cvar. It represents an array of CRAM parallel integer variables. Its main member variables/functions include:

- bits The number of bits of the variable. This is limited by the size of memory/PE.

- addr The address of the variable in CRAM memory. This is assigned by the cvar() constructor when the variable is being created.

- type signed or unsigned integer.

cvar also contains the functions for all the C++ overloaded operators and functions.

These are described in Section 6.2.4 and Section 6.2.5.

- cint and cuint: These classes are descendants of cvar and represent signed and unsigned CRAM integer variables. cint and cuint only differ by type (cint is CVAR\_SIGNED and cuint is CVAR\_UNSIGNED). The size (bits) of the integer can be any positive number less than PE memory size. However, if bits is not specified, it defaults to sizeof(int) to mimic integer variables on the host computer system. This is usually 32 on most systems. The following shows the declaration syntax for cint and cuint variables.

#### **Declaration Syntax**

```

cint a;  // a is a 2-bit signed CRAM integer

cuint sum1(5);  // 5-bit unsigned

cuint error(INIT_0);  // 32-bit unsigned, initialize all its elements to zero

cint b(8, INIT_1);  // 8-bit signed interger, initialize all bits to 1(0xFF)

```

chool and choolref: cbool is a CRAM data-parallel boolean variable. Unlike on standard computer systems where boolean variables are usually implemented as 8-bit (char) variables, on CRAM, cbool is, as it should be, a 1-bit variable. Like cint and cuint, cbool is a descendant of cvar. It however has extra functions to handle logical operators used to combine relational operators (||, &&, and !). cboolref is a pointer to a bit of a cvar variable. It is not a physical object in CRAM memory, but it contains all the information about the address of a bit of cvar. This is an important class in optimizing operations involving cbool or 1-bit cvar, especially where there is no need to create a cbool variable. Otherwise, cboolref behaves exactly like cbool. The declaration syntax for CRAM boolean variables is shown below.

#### **Declaration Syntax**

```

cbool a; // a is a CRAM boolean variable

cbool a = 0; // initialize a to 0 on declaration

cbool mask1(INIT_1); // CRAM boolean, initialize to 1's

cuint d; // 32-bit CRAM unsigned integer

cboolef c(d.addr); // c points to bit 0 of d

cboolef e = d.bit(3); // e points to bit 3 (4th bit) of d

```

cchar, cshort, clong, cnibble: These are fixed bit-length CRAM integer variables. They are also direct descendants of cvar. Like cint, they all have corresponding unsigned integer classes (cuchar, cushort, culong, and cunibble). The sizes (bits) of these classes are derived from the sizes of their corresponding C++ built-in data types. For example, the size of cchar is calculated from CHAR\_BIT\*sizeof (unsigned char). On most machines, cchar would be 8-bit, cshort 16-bit, cint 32-bit, and clong would also be 32-bit. cnibble is a 4-bit CRAM integer variable. cchar, cshort, clong and cnibble have only one constructor with no parameters. In other words, you can not specify the number of vectors, nor can you initialize them on creation (you can always initialize them after they have been declared, without any increase in execution time). The first reason for having fixed-length classes is to allow programmers to declare variables in exactly the same way as is done for built-in C++ data types (no parameters in the constructor). The second reason, and the more important of the two, is that C++ does not allow declaring arrays if the class declaration (constructor) requires parameters. For example, the declaration cuint a (8) [10] is a syntax error, but cuint a [10] is correct. Therefore, where there is need to declare arrays, the programmer can use data types that do not require parameters. Since these classes cover only bit-lengths of 4, 8, 16, and 32, programmers can create any fixed bit-length CRAM integer class by using the declarations and functions of these classes. Declaration syntax for these variables is shown below:

#### **Declaration Syntax**

```

cchar a; // 8-bit signed cint

cushort diff = 4; // 16-bit cuint, initialize all elements to 4

clong d[10]; // an array of 10 32-bit cint's

cnibble rec[8][12]; // a 2-dimensional array of 96 4-bit cint's

```

### 6.2.3 Memory Allocation

Any call to the cvar constructor invokes a CRAM memory allocation function. Since all classes of CRAM variables are descendants of cvar, the cvar() constructor is always called when objects of such classes are being created. In CRAM, variables are not required to be aligned to any particular address boundaries. There is one exception to this rule. A variable cannot be allocated memory that crosses over the 256n address boundary (n = 1, 2, 3,...). For example, a 6-bit cint variable cannot be allocated CRAM memory at CRAM row 254 because this will require its end address to be 259 (crossing over 256). This is so because the only part of the CRAM address that can be incremented or decremented by the controller to move through the bits of a CRAM variable is 8-bit. This is the part of the address that is stored in the ARO-AR1 registers (AXn registers are fixed).

When a CRAM variable goes out of scope, or when the cvar destructor (~cvar()) is explicitly called, the variable is destroyed and its memory is deallocated. Deallocated memory is returned to the CRAM free memory heap if the variable was at the end of the allocated memory. Otherwise it is returned to the fragmented garbage memory. A new variable is allocated memory in the fragmented garbage memory if it can fit in any memory fragment, else it is allocated in the continuous memory heap. If the memory is badly fragmented, i.e. so many small free unallocatable memory holes, the compiler will defragment the memory automatically. For the compiler to be able to do this, it keeps a list of pointers to all currently allocated CRAM variables. All memory allocation and deallocation issues are handled fully by the compiler.

### **6.2.4 Overloaded Operators**

Most of the standard C++ operators have been overloaded for CRAM classes. These operators can be used with CRAM variables in exactly the same way as for standard C++ data types. Table 6.1 lists all operators that can be used with CRAM variables.

| Operator (@)                           | Description                                                                                                                                                     | Examples (cint a, b; cuint c; cbool h; int i)                       |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| =                                      | Assignment                                                                                                                                                      | a = b;                                                              |

| + - * / % & - ^                        | Addition Subtraction Multiplication Division Modulus Bitwise AND Bitwise OR Bitwise XOR                                                                         | a = a + b;<br>c = c % 6;<br>b = 7 & a;                              |

| +=<br>-=<br>*=<br>/=<br>%=<br>&=<br> - | Add and assign Subtract and assign Multiply and assign Divide and assign Modulus and assign Bitwise AND and assign Bitwise OR and assign Bitwise XOR and assign | a += b;<br>c &= 0xFF;                                               |

| ++<br><br>-<br>-                       | Increment Decrement Negate Complement                                                                                                                           | a ++;<br>b =a;<br>a = -b;<br>c = ~a;                                |

| <<<br>>>                               | Shift left<br>Shift right                                                                                                                                       | c = a << 5;<br>b = a >> i;                                          |

| <<=<br>>>=                             | Shift left and assign<br>Shift right and assign                                                                                                                 | c <<= 5;<br>b >>= 2;                                                |

| < > == != = </p                        | Greater than Less than Equal to Not equal to Less than or equal to Greater than or equal to                                                                     | <pre>cif (a &gt;= 6)    a = b; cend</pre>                           |

| <br>&&<br>!                            | Logical OR<br>Logical AND<br>Logical NOT                                                                                                                        | <pre>cif ((b<c) &&="" (!b))="" a="++b;" cend<="" pre=""></c)></pre> |

| []                                     | Subscripting (ith element of cvar)                                                                                                                              | i = a[24];<br>b[3] = 6;                                             |

**Table 6.1 CRAM C++ Operators**

### **6.2.5** Library Functions

Table 6.2 lists functions provided in the CRAM C++ library for CRAM data types. These include functions for bit-slicing, bit-setting, minimum and maximum searches, and PE shifts. Note that PE shift functions (PE.shiftl()) and PE.shiftr()) are used to shift the elements of a CRAM variable, whereas standard shift operators (<< and >>) operate on CRAM variables in exactly the same way as they do on standard integer variables, i.e. the bits of the elements are shifted left or right (equivalent to multiplying or dividing by  $2^n$ ).

| Function(s)                                      | Description                                                                                                     | Examples (cuchar c; cint a, b; cbool h; int y)                                                                          |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| set(),<br>ones()                                 | Sets all bits of cvar to '1'                                                                                    | c.set();<br>//c[PE] = 0xFF                                                                                              |

| reset(),<br>clear(),<br>zero()                   | Sets all bits of cvar to '0'                                                                                    | c.clear(); //c[PE] = 0x00; equivalent to c = 0                                                                          |

| bit()                                            | Returns ith bit (cbool) of cvar                                                                                 | a.bit(5) = h;  // set bit 5 of a to the value of h                                                                      |

| from()                                           | Returns bit-slice (cvar) of cvar                                                                                | c = a.from(4,11);<br>//c is set to bits 11:4 of a                                                                       |

| search_bitset()                                  | Returns the PE number with bit of cbool set to '1'                                                              | y = search_bitset(h);  // y is set to a value such that h[y] = 'l'                                                      |

| ismax()<br>ismin()                               | PE has max(min)imum element of cvar                                                                             | h = ismax(a);  // h[PE]=1 if a[PE] is the maximum element of a                                                          |

| <pre>max() min()</pre>                           | Returns max(min)imum of two cvar's                                                                              | a = min(a, b);<br>// a[PE] = (a[PE] < b[PE])? a[PE] : b[PE]                                                             |

| <pre>maxindex() minindex()</pre>                 | Returns index of PE with max(min)imum element                                                                   | y = maxindex(a); // yth PE contains maximum element of a                                                                |

| <pre>maxele() minele()</pre>                     | Returns the max(min)imum element of cvar                                                                        | y = minele(a); // does int x=minindex(a), then reads a[x]                                                               |

| abs()                                            | Returns absolute value of cvar                                                                                  | a = abs(a); // a = (a < 0)? -a:a                                                                                        |

| <pre>shiftr() shiftl() rotater() rotatel()</pre> | Shift PE elements left/right (rotatex connects edge PEs (PE <sub>0</sub> and PE <sub>N-1</sub> ] when shifting) | PE.shiftr(a, b, 4, 1);  // a[PE] = b[PE+4], fill edge PEs with 'l'  PE.rotatel(a,b);  // a[PE] = b[PE-1], a[0] = a[N-1] |

**Table 6.2 CRAM Library Functions**

### 6.2.6 Data-Parallel Conditional Statements

• Data-parallel conditional execution if supported by the cif statement proposed by Elliott [4]. This is similar to the ifarray construct used in STARAN [43]. The syntax of the cif statement is shown below:

```

Syntax

cif (cbool expression)

{

ctstatements ...

cfstatements ...

cfstatements ...

}

cend

}

Example

cif (a > b)

c += a;

celse

celse

celse

cend

}

cend

```

cbool expression is any expression that returns a cbool object. The resulting cbool value has a 1 where the PE evaluated the expression to be true, and a 0 where the expression evaluates to false. This cbool value is then written to the PEs write enable (WE) registers to enable or disable the PEs from writing to their own memory. One key difference between cif and the C++ if constructs is that in the cif, all the PEs will execute the statements in both the cif (ctstatements) and celse (cfstatements) branches regardless of whether the cbool expression evaluates to false or true for a particular PE. The conditionality of the cif construct lies in the fact that the PE will only write the results of the executed statements to its memory if the condition evaluated to be true. Therefore, a useful statement inside a cif/celse will be one that assigns its result to a cvar (variable in CRAM memory), otherwise the statement will be executed unconditionally. Also, unlike the C++ if, cif cannot be used for say code execution speedup since all statements inside a cif or celse are always executed.

In order to support nested cif's, a stack of cbool variables is maintained, with the top of the stack containing the current value of the write enable registers. This stack is automatically managed by the constructor and destructor of the write\_en CRAM class. When a cif is executed, the result of the cbool expression is ANDed with the top of the stack (WE values), and the result written back to the WE registers and the top of the stack. The statements inside the cif are then executed. After this, if celse is encountered, and the cbool value next to the top of the stack is true, then the contents of the WE registers

and the top of the stack are inverted. After this, the statements inside the celse are executed. Notice that celse is optional. Every cif, or cif/celse pair, must be terminated with a cend. When cend is executed, the top of the stack is popped out and the write enable registers are restored to their values before the conditional execution.

cif, celse and cend are all defined as preprocessor macros. The curly brackets surrounding the statements inside a cif or celse are optional, but it is advisable to include them if there is more than one statement inside a conditional branch.

### **6.2.7** Operations with Scalar Constants

Operations that have a cvar and an integer value as operands (except << and >>) use the CRAM controller constant broadcast unit (Section 4.5.2). Instead of loading the integer into a temporary cvar in CRAM memory and doing the operation on two cvar variables, the integer is loaded into the controller write buffer and the operate-immediate instruction (such as ADDI, SUBI, etc.) is executed. Thus, the load-constant instruction (LDK), which has 2\*bits microinstructions, is avoided, and no extra CRAM memory is required to store the integer constant. Also, the constants can be pre-loaded into the write buffer and operations performed directly with the constants in the buffer. The advantages of this are outlined in Section 4.5.2.

The CRAM C++ compiler performs some optimizations for operations with certain integer constants. This optimization is done by substituting the operation with an operation which results in fewer microinstructions. Table 6.3 shows all optimized operations. The compiler also optimizes multiplication and division by  $2^n$  (n = 0, 1, 2,...) by replacing them with shift operations (<< and >>, respectively). However, to reduce the overhead of testing against all the possible constants, this optimization is only done for the constants 2, 4, 8, 16, 32 and 64. The programmer can perform the optimizations for the rest of the constants either at compile time (if they are known in advance) or at runtime (by testing against all such constants of interest).

| Intended Operation                                                                                                        | Optimized Operation                                                                                                          | Microinstructions<br>Saved(n=bits)      |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| $a = b + 0 \Rightarrow ADDI a, b, #0$<br>$a = b - 0 \Rightarrow SUBI a, b, #0$                                            | $a = b \Rightarrow MOV a, b$                                                                                                 | 3n+1                                    |

| $a = b \mid 0 \Rightarrow ORI a, b, #0$<br>$a = b ^ 0 \Rightarrow XORI a, b, #0$<br>$a = b & 1 \Rightarrow ANDI a, b, #1$ | a = b ⇒ MOV a, b                                                                                                             | 2n                                      |

| $a = b \& 0 \Rightarrow ANDI a, b, #0$                                                                                    | a = 0 ⇒ CLR a                                                                                                                | 4n-1                                    |

| $a = b \mid -1 \Rightarrow ORI \ a, \ b, \#-1$                                                                            | a = 1 ⇒ SET a                                                                                                                | 4n-1                                    |

| $a = b ^ -1 \Rightarrow XORI a, b, #-1$                                                                                   | $a = \overline{b} \Rightarrow NOT b$                                                                                         | 2n                                      |

| a = b   1 ⇒ ORI a, b, #1                                                                                                  | $a(0) = 1 \Rightarrow SET \ a(0)$<br>$a(n-1:1) = b(n-1:1) \Rightarrow$<br>$MOV \ a(n-1:1), \ b(n-1:1)$                       | 2n+1                                    |

| a = b & 1 ⇒ ANDI a, b, #1                                                                                                 | $a(0) = b(0) \Rightarrow MOV \ a(0), \ b(0)$<br>$a(n-1:1) = 0 \Rightarrow CLR \ a(n-1:1)$                                    | 4n-3                                    |

| a = b ^ 1 ⇒ ORI a, b, #1                                                                                                  | $a(0) = \overline{b(0)} \Rightarrow NOT \ a(0), \ b(0)$<br>$a(n-1:1) = b(n-1:1) \Rightarrow$<br>$MOV \ a(n-1:1), \ b(n-1:1)$ | 2n                                      |

| $a = b + 1 \Rightarrow ADDI a, b, #1$<br>$a = b - (-1) \Rightarrow SUBI a, b, #-1$                                        | $a = b + 1 \Rightarrow INC a, b$                                                                                             | 2n-1                                    |

| $a = b - 1 \Rightarrow SUBI a, b, #1$<br>$a = b + (-1) \Rightarrow ADDI a, b, #-1$                                        | $a = b - 1 \Rightarrow DEC a, b$                                                                                             | 2n-1                                    |

| $a = 0 - b \Rightarrow SUBI a, #0, b$                                                                                     | $a = -b \Rightarrow NEG a, b$                                                                                                | 2n-1                                    |

| $a = -1 - b \Rightarrow SUBI a, \#-1, b$                                                                                  | $a = -1 - b \Rightarrow {}^{\dagger}MINUS a, b$                                                                              | 2n-1                                    |

| a = 0 ⇒ MVI a, #0                                                                                                         | a = 0 ⇒ CLR a                                                                                                                | ÷n-1                                    |

| $a = -1 \Rightarrow MVI a, #-1$                                                                                           | a = -1 ⇒ SET a                                                                                                               | ‡ <b>n-</b> 1                           |

| a = 1 ⇒ MVI a, #1                                                                                                         | $a(0) = 1 \Rightarrow SET \ a(0)$<br>$a(n-1:1) = 0 \Rightarrow CLR \ a(n-1:1)$                                               | ÷n-1                                    |

| $a = b * 0 \Rightarrow MLTI a, b, #0$                                                                                     | $a = 0 \Rightarrow CLR a$                                                                                                    | $^{\ddagger}6n^2+3n-1$                  |

| a = b * 1 ⇒ MLTI a, b, #1                                                                                                 | $a = b \Rightarrow MOV a, b$                                                                                                 | $^{\ddagger}6n^2+n$                     |

| $^{\sharp}a = b * 2^k \Rightarrow MLTI a, b, #2^k$                                                                        | $a = b \ll k \Rightarrow SL a, b, \#k$                                                                                       | <sup>‡</sup> 6 <i>n</i> <sup>2</sup> -1 |

| $a = b / 1 \Rightarrow DIVI a, b, #1$                                                                                     | $a = b \Rightarrow MOV a, b$                                                                                                 | $^{\ddagger}16n^2+36n+2$                |

| $^{\dagger}$ a = b / $2^{k} \Rightarrow DIVI a, b, \#2^{k}$                                                               | $a = >> k \Rightarrow SR a, b, \#k$                                                                                          | $^{\div}16n^2+35n+1$                    |

<sup>&</sup>lt;sup>†</sup>Special type of NEG with Y initially set to 1.

**Table 6.3 Optimizations for Operations with Constants**

Plus the time for loading the constant from the host into the controller write buffer.

<sup>\*</sup>k = 1, 2, 3, 4, 5, 6.

### **6.2.8 Operand Extension**

Operand extension is required if source operands have different number of bits, or if the number of bits of one operand is less than that of the destination operand. In CRAM, rather than physically extending the operands by creating temporary variables, each overloaded C++ operator has a CRAM instruction that is executed if a specific operand extension is required. This increases the speed of execution and also removes the need for using extra CRAM memory. For example, consider the execution sequence of an expression c = a + b, where a is 8-bit, b is 4-bit, and c is 16-bit. Firstly, the ADD instruction is executed for the first 4 bits. Then ADD1 is executed for the next 4 bits to extend b to the size of a, and finally ADD0 is executed to extend a and b to the size of c. In other words, ADD1 only has to ripple carries, and ADD0 is just sign extension. These instructions give a saving of 2n and 4n cycles, respectively, when executed for n bits instead of using the full ADD instruction. CRAM operand extension instructions have very few microinstructions and hence have been implemented for all the main operators.

# **6.2.9** Support Classes

Apart from the CRAM variable classes described in the previous sections, the CRAM C++ library also has classes for objects of the CRAM controller, CRAM PEs, and the host processor. These are briefly described below.

• Controller Objects: The CRAM controller class contains all information about the controller that is necessary to the CRAM C++ compiler. This includes the memory map of the units, the size (in bytes) of the instruction FIFO, the read/write buffers, and the control store, and information about controller registers and other units. This information is provided in form of controller sub-classes and instantiation of their objects in the controller class object. This approach is advantageous because it mimics the hardware architectural composition of the controller. Therefore specific functions can be implemented for the class of an individual controller unit or register, in order to model its behavior and keep track of its status during instruction execution. This makes it easier for the compiler to perform code execution optimization that is dependent on the architecture of the controller. Controller sub-classes include classes for the

instruction FIFO, read/write buffers, control store, command/status registers and their individual bits, and all user-accessible parameter registers. Typically, a class of a controller register includes members to store the register address and value. Member functions include those to implement register assignment (e.g. WLEN = 7), and register increment/decrement (e.g. ARO++). Common member functions for classes of the other units (FIFO, buffers, control store) are functions for reading and writing data. As mentioned earlier, these sub-classes and their functions allow the use of standard C++ constructs when assigning, incrementing, decrementing, reading and writing controller registers and units. Also, by having controller hardware units as objects in the C++ library enables the compiler to have an intelligent and updated information about the status of the relevant units. This is used in code optimization, for example by avoiding unnecessary updating of a register when the register already contains the value that it is supposed to be updated with.

- Processing Element (PE) Objects: The CRAM PE class contains information about, and functions to manipulate PE components. This includes the instantiations of CRAM registers (X, Y, M, W) and their groupings (such as XY, XWY), and functions for register assignment and PE shift operations. Like the controller classes, PE classes simplify the use of PE objects in the compiler or application source code. For example, to set all the PE X registers to zero, instead of issuing a native CRAM instruction, one may code it in normal C++ syntax using PE.X = 0. A number of PE assignment operators have been included to implement common PE register operations such as initialization (PE.W = 1), register-to-register copy (PE.X = PE.Y), and cvar-to-PE-register copy (PE.W = a.bit(8)).

- Host Computer Objects: Host computer classes include the software transposing buffers (Section 6.3) and CRAM instruction types. The instruction types are used for specific instruction characterization during execution. Examples include a one cvar source operand instruction (one\_addr\_instr), two cvar source operands instruction (two\_addr\_instr), and one cvar and one integer constant instruction (addr\_cont\_instr).

### 6.2.10 CRAM System Objects and Their Initialization

When an application compiled with the CRAM C++ library is run, a number of CRAM system objects are created and initialized. The compiler initializes these objects to the initial values of the real hardware units they represent. These objects include:

- **PE** This represents the components of CRAM processing elements described in Section 6.2.9. Therefore, in the application code, all references to CRAM PE registers should be qualified with PE, e.g. PE.X to denote all PE X registers.

- **controller** This object denotes the CRAM controller, and hence must qualify all reference to controller resources, e.g. controller.WLEN.

- host Represents the host processor. The software transposing buffers (Section 6.3) are defined in the host object (host.read\_buffer and host.write\_buffer).

- ALL\_ZEROES\_MASK This is of type cbool and is initialized to a value of all zeroes. It is located at CRAM memory row 0.

- ALL\_ONES\_MASK This is of type cbool and is initialized to a value of all ones.

It is located at CRAM memory row 1.

- MASK\_01 This is of type cbool and is initialized to the value 0x01. It is located at CRAM memory row 2.

# 6.3 Corner-Turning: Host Access of CRAM Variables

Since CRAM operates on data in bit-serial format while the host computer is a bit-parallel system, data must be converted from bit-serial to bit-parallel and vice-versa when it is transferred between the two systems. This is referred to as either corner-turning, data transposing, or format conversion. Typically, data is transposed using multidimensional access memory (MDA) and a flip or shuffle network like the ones used in STARAN [46], [47], or the MIT image processor [14]. These methods require a lot of hardware, especially if the system is general-purpose and its operands are not fixed to a particular size (bits). For example, even for such an application-specific processor as the MIT pixel-parallel image-processing system [14], whose data path is designed for 8-bit gray scale pixels, sixteen 64Kb x 4 SRAMs, plus shuffler, address and other glue logic, are used to transpose the data between the host and the PE array [41]

Because of the high hardware cost and complexity of hardware corner-turning, data on a CRAM system is transposed in software. Traditionally, software data transposition is done on the host computer. This is slower than a hardware transposer, and may severely degrade performance especially if the number of elements to be transposed in a parallel variable is large. But with current increasing processor speeds, host-based data transposition offers a good alternative for low-cost system implementation. An example of a logic-in-memory system that uses software data transposing is the Terasys PIM workstation, which transposes data using its Sparc-2 host processor [13].

To reduce the overhead of transposing a large number of elements of a CRAM variable, a parallel array-based corner-turning approach that exploits the large degree of parallelism of the PE array and the 1-D inter-PE communication network has been developed. A 6-bit Buffer Address Increment register has been included in the CRAM controller to allow faster corner-turning of multi-byte data. The following sections describe these two corner-turning approaches.

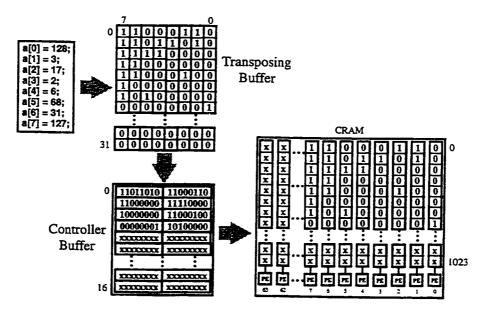

### 6.3.1 Host-Based Data Transposition

Host-based data transposition is used if the number of elements to be accessed by the host is small. This is supported in the CRAM C++ library through the subscripting operator ([]). This operator has been overloaded for cvar in order to support constructs similar to those used by C++ in accessing elements of arrays for built-in data types. Any element of cvar can be addressed using the [] operator. For example, to initialize the 5th element of a cint variable x with an integer value of 6, the expression x[5] = 6 is used. Similarly, the ith element of x can be assigned to an integer variable y using the expression y = x[i]. Figure 6.3 shows how integer values are written to cvar elements using this method. The data is first corner-turned through the host software write buffer (using shifting and masking), then written to the CRAM controller write buffer, and finally transferred to the CRAM memory using a WRITE instruction. If CRAM is a bytewide memory, for the values to be transferred using the WRITE instruction, eight consecutive cvar elements must be loaded at the same time. If cvar elements are assigned in a non-consecutive manner (e.g. the expression a[0] = 2 is followed by a[3] = 7), or if fewer than eight consecutive elements are assigned to, or if neither the first nor the last of the eight elements is on the  $8n^{th}$  PE (n=0, 1, 2, ...), the values are written to the PEs memory as scalar constants. This is much slower because for an element to be initialized

Figure 6.3 Host Corner-Turning

as a constant, the other PEs are first masked off by writing 0's to their write enable registers. After that, the constant is loaded into the controller write buffer, and finally loaded to all cvar elements using a LDK (load-constant) instruction. The WE registers are then restored to their previous values. If more than one element is to be loaded, this process is repeated for each element. Therefore to speed up the initialization of cvar elements, an effort must be made to initialize them consecutively. This can be achieved simply by initializing the elements using a for loop, with the initial value of the index starting at the 8nth PE. To complement this, a cvar load\_elements() function is provided which takes as arguments a pointer to the integer array, the size of the elements in the integer array, the cvar variable, and the number of cvar elements to be initialized. In both of these methods, the CRAM compiler automatically uses the transpose-WRITE method unless the number of cvar elements to be initialized is less than eight.

All elements of a cvar can be loaded with a uniform value by making the assignment without the [] operator. For example, for a cint variable y, all its elements can be loaded with 7 by using the expression y = 7. This uses a load-constant instruction with all WE registers enabled (by default, WE registers are always enabled). This is faster than the transpose-WRITE method since it requires only one load (to load the value into the controller write buffer) and one CRAM instruction (LDK).

Reading the value of a cvar element is almost the reverse of the write process described above. If CRAM is a byte-wide memory, eight cvar elements, including the one to be read, are read from CRAM to the controller read buffer using the READ instruction. These values are then transferred to the host read buffer, where the required value is transposed and returned to the assignment statement. Since eight elements were read, any subsequent assignment to the elements whose values are in the host read buffer will use these values without the need to read them from the CRAM chip. This is done until the elements in the read buffer are marked 'dirty', which happens when the cvar variable is used as a destination operand in an instruction.

### 6.3.2 Parallel Array-Based Data Transposition

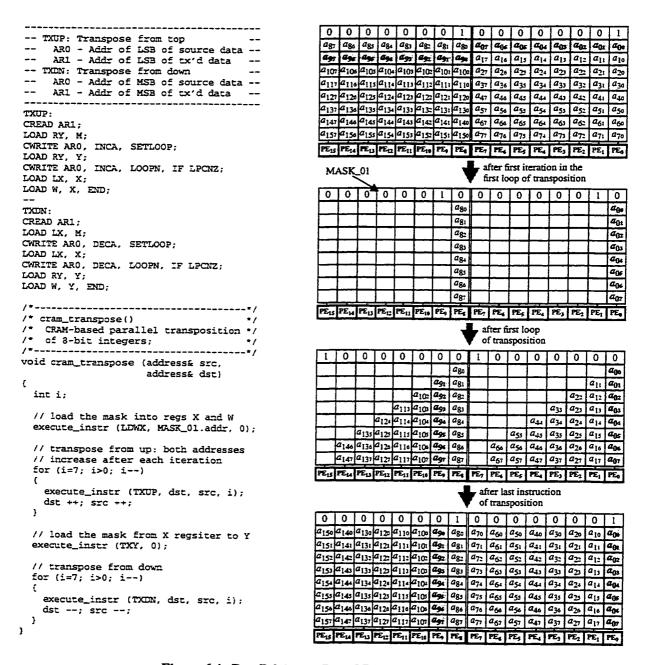

To transpose the elements of an n-bit CRAM variable on the PE array itself, the data is loaded onto the CRAM array in the normal host (parallel) format, with n elements spread across n PEs. The data is then transposed in groups of n PEs by rotating the  $n \times n$  bits. Typically, the minimum value of n is 8 since the byte is the smallest storage unit on most standard computers. Figure 6.4 illustrates array-based data transposition. For clarity, only

Figure 6.4 Parallel Array-Based Data Transposition

the first 16 elements of an 8-bit CRAM variable are shown. The exact steps are described in the actual transpose microroutines (TXUP and TXDN) and the C++ function (cram\_transpose()).

If i is the number of the PE in the n-PE group, and j is the memory row of the PE, then data transposition is performed by moving the bits in the  $n \times n$  window such that

$$a'_{ij} = a_{ji}, \ 0 \le i, j < n$$

(6.1)

where a' is the transposed version of a. This is a symmetrical transformation and hence to transform data from CRAM format to host format, exactly the same operation is performed.

The TXUP and TXDN microroutines each executes (5 + 2i) microinstructions, where i is the loop count variable in the transpose loops of the C++ cram\_transpose() function. Each of these loops is executed (n-1) times (n) is the number of bits of the CRAM variable). Also note that before the transpose microroutine is executed, the WLEN register is first set to i. This makes the number of microinstructions executed for each transpose microroutine call equal to (6 + 2i). Therefore, the total number of microinstructions executed in each of the transpose loops in cram\_transpose() is equal to

$$M_{tx} = 6(n-1) + 2\sum_{i=1}^{n-1} i$$

(6.2)

For a CRAM system of cycle time  $T_c$ , the total time to transpose data,  $T_x$ , is equal to the time to execute the  $2M_{tx}$  transposition microinstructions and six initialization microinstructions. The initialization instructions are used to update address extensions for MASK\_01, src and dst operands, plus two microinstructions for LDWX, and one for TXY. Therefore,  $T_x$  is given by

$$T_x = \left\{ 2 \left[ 6(n-1) + 2 \sum_{i=1}^{n-1} i \right] + 6 \right\} T_c$$

(6.3)

Simplifying Equation 6.3 gives

$$T_x = 2(n^2 + 5n - 3)T_c ag{6.4}$$

Like all array-based PE operations, this time is constant for all numbers of elements equal

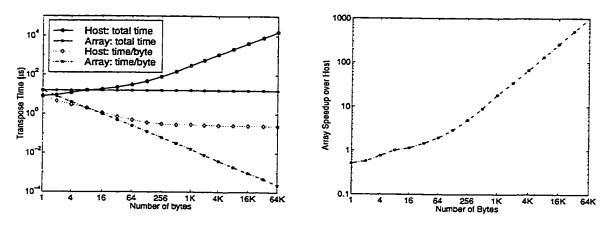

to or less than the number of PEs. Therefore, as the number of PE increases, the equivalent time to transpose an element decreases because of the parallelism in the PE array. For an 8-bit CRAM variable, the number of microinstructions executed in Equation 6.4 is equal to 202, and the transpose time for a 50 ns CRAM system is 10.1 µs. Figure 6.5 shows the performance of transposing a varying number of elements of an 8-bit CRAM variable using either the PE array of a 50 ns 64K-PE PCI CRAM system or a 133 MHz Pentium host PC. It is evident from the figure that host-corner turning is beneficial only if a very small number of elements (less than 8) is to be accessed.

Figure 6.5 Array-Based vs. Host-Based Transposition

#### Transposing N-byte Variables

The transpose time for an *n*-bit variable has a complexity of  $O(n^2)$ . Therefore the transpose time for 16-bit and 32-bit variables would be almost 4 times and 16 times, respectively, the transpose time of 8-bit variables. More precisely, using Equation 6.4, the transpose time for a 16-bit and 32-bit variable is 3.3 times and 11.7 times, respectively, the transpose time of an 8-bit CRAM variable.

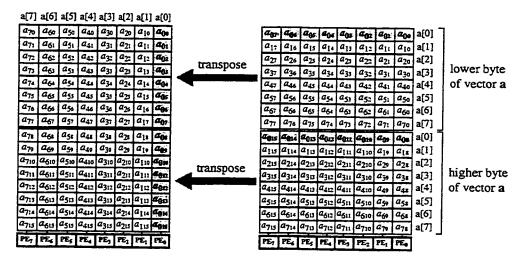

To reduce the time of transposing multi-byte variables, a procedure that has a complexity of O(n) has been developed. This involves loading corresponding bytes of 8 consecutive elements in 8 consecutive memory rows, and then transposing them as 8-bit variables. Figure 6.6 illustrates this for a 16-bit variable. There is no extra overhead for this data arrangement because it is supported in the CRAM controller by simply loading the Buffer Address Increment register with N prior to issuing the WRITE instruction.

Using this approach, the transpose time for an N-byte CRAM variable is only N times that of a 1-byte (8-bit) CRAM variable.

Figure 6.6 Transposing N-Byte Variables

### **6.3.3** Effect on Performance

The performance of data transposition is usually measured relative to the I/O overhead of transferring data between the bit-serial system and its host. This is so because in most cases the need to transpose data arises because data on the host has to be used by the bit-serial system and vice versa. An ideal data transposer adds nothing to the I/O overhead.

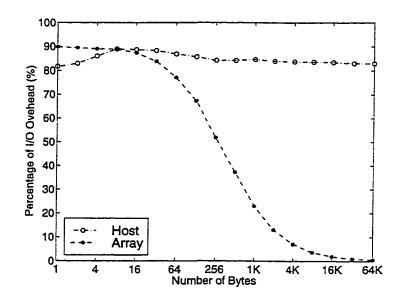

Figure 6.7 shows the data transpose time as a percentage of the total I/O overhead (data transposing + data transfer). Again, this is for a 50 ns CRAM system interfaced through a PCI bus to a 133 MHz Pentium PC. If the number of bytes to be transferred and transposed is small, both corner-turning approaches constitutes a very high percentage (more than 80%) of the total I/O overhead. But as the number of bytes increases, the percentage contribution of array-based transposition decreases, while that of host transposition remains almost constant. In other words, data transfer time increases in both cases, data transposition time when using the parallelism of the PE array remains constant, while the time of transposing data on the host also increases with the number of bytes. Typically, a CRAM system would have more than 4K PEs. This means that parallel CRAM variables would have 4K elements or more. For this case, data transposition using the PE array contributes less than 10% to the total I/O overhead. This number is as low as

0.5% for a 64K-PE PCI CRAM system. Note that the percentage contribution of data transposition is even smaller for slower buses because of the higher data transfer time. Also, when calculated as a percentage of the total execution time of an application (I/O overhead + code execution time), the effect of data transposition drops even further.

Figure 6.7 Data Transpose Time as Percentage of Total I/O Overhead

#### 6.4 CRAM Assembler

#### 6.4.1 Introduction

For applications that require explicit control of the raw hardware, applications can be written directly using the CRAM Controller Assembly Language (also known simply as the CRAM Assembly Language). This assembly code can either be mixed with the CRAM C++ code and tagged with the keywords CASM and END CASM, or it can written as separate code. If mixed with C++ code, the CRAM assembler (CASM) is used as a preprocessor before compiling the mixed code with a C++ compiler. In this case, CASM simply converts the assembly code into a C++ function to transfer the instruction to the controller instruction FIFO.

As with most assembly languages, it is very unlikely that a typical application programmer will ever use CRAM assembly code, except in situations where assembly

CRAM Assembler

code offers considerable speed-up when compared to C++ code. Otherwise, CASM is a vital software development tool and has been used in, among other things, developing the CRAM C++ library and the CRAM C++ simulator, and generating input files for the controller VHDL simulations. The following section briefly describes the CRAM assembly language.

### 6.4.2 CRAM Assembly Language

A complete listing of the CRAM Assembly Language is found in Appendix C.1. This includes the syntax and usage examples of all the instructions in the language. The following sections give a very brief description of the instructions:

• CRAM Memory Variable Instructions: These are instructions that operate on CRAM memory variables (cvar). They include instructions to perform arithmetic, logical, relational, and search operations, as well as to shift, load, copy, set, and clear CRAM variables. Some of these instructions can have an immediate value as one of its source operands. A few of the logical operations are provided with what are called 'boolean instructions' in order to avoid the overhead of setting up the word-length (WLEN) register for operations involving boolean CRAM variables (see Appendix C.1 for details). A few examples of cvar instructions are shown below.

#### **Examples**

```

ADD #24, #16, #8;  // mem[24] = mem[16] + mem[8]

INC #24, #16;  // mem[24] = mem[16] + 1

MAX #27, #16;  // mem[17] = (is maximum element of mem[16])

MCLR #18;  // mem[18] = 0

MOV ARO, AR1;  // mem[AR0] = mem[AR1]

```

• **CRAM PE Register Instructions:** These are instructions that operate on PE registers. They include instructions to set or clear registers, and instructions to load PE registers from either other PE registers, or from cbool or cboolref variables.

#### **Examples**

```

CLR X Y; // all X and Y PE registers are set to 0

LDPE X, !#16; // load all X registers with inverse of mem[16]

TXPE X, Y; // load X registers with contents of Y registers

```

CRAM Assembler

CRAM Controller Instructions: CRAM controller instructions include instructions to load, increment and decrement controller registers, as well as instructions for reading and writing data between CRAM and the controller. There is also a conditional read-bank instruction (RDBNK) used to scan a cbool or cboolref variable to check if there is a 1 at any PE position. This is done by first reading the byte of the variable corresponding to the first eight PEs. If this byte contains a 1 on any of its eight bits, the byte is saved in the DTR register and the RDBNK instruction terminates. Otherwise the bank address register (CBA) is incremented to point to the byte corresponding to the next eight PEs, and the cycle is repeated. This is repeated until either a 1 is found or all the bits of the variable have been scanned. The results of the scan (CBA and DTR) can be used by the host processor to compute the index of a PE that yielded a true value to a search or comparison.

**RDBNK** AR0; // loop (DTR = mem[AR0]) until mem[AR0] != 0

# 6.4.3 Using cvar Addresses and C++ Integer Variables

One special feature of the CRAM assembly language is that when it is mixed in CRAM C++ code, one can use the address of a C++ defined cvar variable where ever it is legal to use #ARO, #AR1, and #AR2. The address of a cvar is specified as var.addr, where var is the cvar variable. Any valid expression of addr can be used in the assembly code, e.g. var.addr+2 for the address pointing to bit 2 (the third bit) of var. Similarly, any integer defined in the C++ code can be used where ever an immediate value or a cvar address is allowed in the assembly code. This allows easy optimization of part of the CRAM C++ code using CRAM assembly code.

#### Example

### 6.5 CRAM Microcode Assembler

The CRAM Microcode Assembler (CMASM), simply known as the CRAM Microassembler, is used as a high-level development tool when generating microinstruction routines. Instead of writing microinstructions in their native binary format, CRAM Microassembly Language is used. Typically, this is high-level language for low-level PE/RAM operations (e.g. AND X, Y M X; i.e. let each PE do an AND operation of the contents of registers Y M, and X, and write the result into X), and CRAM controller microinstruction execution control (e.g. SETLOOP...LOOPN IF LPCNZ; i.e. execute these microinstructions until the loop counter is zero).

Microinstruction routines for all operators and functions in the CRAM C++ library and the CRAM Assembly Language have already been generated (using CMASM) and comes together with the CRAM software library. Still there might be need to extend the C++ library or CASM, especially if a certain application-specific function occurs so frequently in application source codes as to warrant being implemented as a microroutine in the controller control store. In this case, the programmer can use CMASM to generate the microinstructions and append them to the existing ones. Otherwise, like CASM, the microassembler is mainly used by the CRAM designers in system development and analysis work. Details of the Microassembly Language can be found in Appendix C.2.

### 6.6 Grouping of Microroutines

As described in Chapter 3, the ALU result of a CRAM PE is derived from the truth table of its three input registers. Therefore, source operand registers are specified in terms of an 8-bit truth-table value, and this value is unique for each operation. This, together with the specification of destination operands, makes the number of microinstructions required for an operation much bigger when compared to standard processors. For example, with four possible destination registers (W, X, Y) and six possible source registers (X, Y, M, !X, !Y, !M), an instruction to move the contents (or inverse) of a register to another requires 34 unique 14-bit values of COP-TTOP combinations (6-bit COP and 8-bit TTOP).

To reduce the number of microinstructions in the control store, microroutines of all

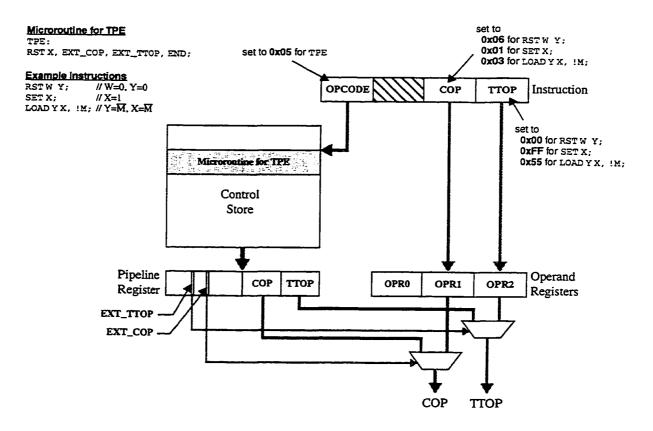

instructions that differ by TTOP and/or COP in only one corresponding microinstruction have been grouped together. For each group, only one representative microroutine is loaded into the control store. The different values of TTOP and/or COP for the specific instructions in the group are coded in the unused operand fields of the instruction issued from the host. This has three advantages when compared to using bits in the instruction to point to specific microroutines or microinstruction subroutines. First, the size of the control store is reduced since we don't have to store the other microroutines or microinstruction subroutines. Second, the level of address decoding and multiplexing for the microprogram sequencer is reduced. This reduces both the area and critical path of the sequencer. Third, this approach further justifies the use of a uniform RISC-like instruction format for the macroinstructions because the wastage of bandwidth due to unused fields of the instruction word is now smaller. As mentioned earlier, a uniform instruction format results in simpler and faster instruction decoding and flow. Figure 6.8 illustrates microroutine grouping for instructions that set, clear, or transfer data between PE registers.

Figure 6.8 Grouping of Microroutines

Microroutines with more than one microinstruction are also grouped and executed in a similar way, with external TTOP and/or COP being selected only for the one specific microinstruction. Note that microroutine grouping is possible only if the instruction has less than three operands. Table 6.4 shows all instruction groups and those where microroutine grouping has been applied. Using this approach has reduced the number of microinstructions for basic operations from 462 to 197, i.e. a more than 57% reduction in the required size of the control store.

| Instruction<br>Group                                                  | No. of instructions | Total no. of microinstructions | <sup>†</sup> Grouped instructions | Microinstructions in control store |

|-----------------------------------------------------------------------|---------------------|--------------------------------|-----------------------------------|------------------------------------|

| No operation                                                          | 1                   | 1                              | -                                 | 1                                  |

| Controller-to-CRAM access                                             | 4                   | 4                              | -                                 | 4                                  |

| Controller instructions                                               | 9                   | 9                              | 1x9                               | 1                                  |

| PE reg-to-reg transfer, set, reset                                    | 48                  | 48                             | 1x48                              | I                                  |

| Load PE-reg from memory                                               | 14                  | 28                             | 1x14                              | 2                                  |

| Load mem from PE-reg or constant,<br>Extend result of logical operate | 20                  | 40                             | 2x8, 1x10<br>1x9                  | 6                                  |

| Memory-to-memory move, Extend operand of logical operate              | 8                   | 24                             | 1x5<br>1x2                        | 9                                  |

| Add/sub, logical operate two cvar's                                   | 7                   | 39                             | -                                 | 39                                 |

| Add/sub cvar & constant                                               | 3                   | 18                             | -                                 | 18                                 |

| Logical operate cvar & constant                                       | 3                   | 12                             | 1x3                               | 4                                  |

| Increment, decrement, negate,<br>Extend operand of add/sub            | 16                  | 81                             | 2x3, 1x2<br>2x2                   | 18                                 |

| Extend constant of add/sub                                            | 6                   | 27                             | 3x2 <sup>‡</sup>                  | 15                                 |

| Extend constant of logical operate                                    | 3                   | 9                              | 1x3                               | 3                                  |

| Extend result of arithmetic operations                                | 12                  | 47                             | 2x6 <sup>‡</sup>                  | 10                                 |

| Compare two cvar's                                                    | 2                   | 8                              | 1x2                               | 4                                  |

| Compare cvar and constant                                             | 3                   | 9                              | 1x3                               | 3                                  |

| Extend operand of compare                                             | 6                   | 12                             | 2x3                               | 4                                  |

| maximum/minimum search                                                | 2                   | 18                             | 1x2                               | 9                                  |

| PE Shifts                                                             | 4                   | 18                             | -                                 | 18                                 |

| Data-parallel conditions                                              | 2                   | 14                             | -                                 | 14                                 |

| Data transpose                                                        | 2                   | 14                             | -                                 | 14                                 |

| Total                                                                 | 175                 | 462                            | -                                 | 197                                |

<sup>†</sup>Example: 2x3 means 2 groups of 3 instructions each.

Table 6.4 Instruction Groups

<sup>&</sup>lt;sup>‡</sup>Partial or irregular grouping.

### 6.7 CRAM C++ Simulator

#### 6.7.1 Introduction

The CRAM C++ simulator is a tool that is used to simulate the behavior of a CRAM system. This can be used by both hardware and software designers. Hardware designers can use the simulator to explore different architectures of CRAM, its controller, and overall system design before committing to the actual hardware implementation. This would improve both the quality and performance of the design, while reducing the number of architectural errors that are only apparent after a design has been simulated or implemented. CRAM software tools designers can use the simulator to test and debug their tools, and applications developers can test their programs and extract more accurate timing information. The fact that the simulator offers a generic number of processing elements (PEs) makes it an ideal tool for performance analysis. While small prototype systems can easily be implemented at this stage of CRAM research work, the potential advantages of CRAM can only be demonstrated relevantly on systems with a large number of PEs. The simulator allows this to be easily realized.

For the simulator to be an accurate architecture exploration tool as well as yield more accurate program execution and timing behavior, the simulation model of the CRAM PEs and the CRAM controller is based on the hardware description of the actual implementations rather than on just their behavior. The disadvantage of this is that it makes the design of the simulator more complex and the simulator runs slower than that based purely on the behavior of the components. However, such a simulator gives out a behavior that is closer to that obtained by the design hardware description (VHDL/Verilog) used in the actual design and implementation phases. This reduces the number of changes required when moving from an architecture obtained through simulation to that which is to be implemented using a hardware description language. It also yields more accurate timing information than that obtained in a behavioral simulator because in the latter a number of processes are usually bundled up in a single simplistic behavior.

The CRAM simulator is not an independent tool. Rather, it is designed to be a library that, when needed, can be linked with an application together with the CRAM C++

CRAM C++ Simulator

library. In this way, the execution of a program on the host, up to the point where the host transfers data onto the CRAM card or simulation model, is not a simulation but the real thing. This has some advantages. First, the complexity of the simulator is minimized since very few host features need be incorporated into the simulator. In particular, only the simulation of the CRAM card driver, and the timing information of the host system buses are required. All other aspects of program compilation and execution are already taken care of by the CRAM compiler. The second advantage is that even when you are using the simulator instead of an actual CRAM card, the timing information and program execution as related to the host system (except for transfers over the system bus) is exactly the same. This is especially important during the design and fine-tuning of the CRAM C++ library and other software tools.

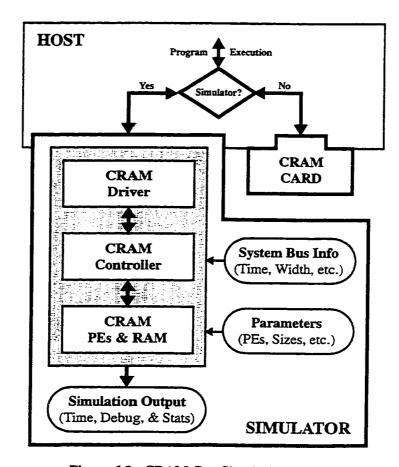

#### 6.7.2 Simulation Model

Figure 6.9 shows the CRAM C++ simulation model. When code executes on the host system, the simulator is invoked only when the host transfers data to the CRAM system. A single line in the CRAM compiler checks if the execution is on a simulator or on an actual CRAM card. If on a simulator, the host transfers data to the CRAM system by calling the simulator CRAM driver, otherwise the real driver is used. The simulation models of the CRAM system and the host environment are described in Section 6.7.3 to Section 6.7.5, and the different outputs of the simulator are described in Section 6.7.6 to Section 6.7.8.

### 6.7.3 Host Objects

The CRAM driver is the only component of the host system that is incorporated into the simulator. It is used as the link between the actual host system and the simulation model of the CRAM system. It simulates both the driver as well as different system buses (PCI, ISA, etc.). A link to the host system is through a function call to the driver (as would be done on a real system), while a link to the CRAM controller simulation model is through a function call that emulates the sequence of bus signals required to complete the data transfer on a specific system bus. Currently, only the ISA bus protocol is implemented in detail. The other buses are simulated by specifying the generic parameters

CRAM C++ Simulator

of the bus model such as bus width, bus speed, and whether the bus supports burst transfers.

Like all other models in the simulator, the host simulation model is implemented as a C++ class. Its class constructor is used, among other things, to model what happens when the CRAM driver is being initialized, such as the loading of microinstructions into the CRAM control store. Most timing parameters are also initialized at this time.

Figure 6.9 CRAM C++ Simulation Model

#### 6.7.4 CRAM Controller

The simulation model of the CRAM controller is a hardware description (using C++) of the controller core components as well as the CRAM-host interface. Components are described as classes, with functions used to describe specific component features such as external and internal access and instruction execution. The flow of an instruction through the instruction execution unit (IXU) is described the same way as in the hardware, i.e.

instruction read from FIFO to IR, then executed in the microprogram sequencer using microinstructions, PE or RAM functionality decoded, address and data multiplexed with TTOP and COP and driven onto the CRAM bus, and finally the CRAM control signals (OPS, MCK, RW, etc.) asserted. All the other components are also modeled with such detailed hardware description. Such modeling is very easy to do if the real hardware was designed using a hardware description language such as VHDL or Verilog. This detailed modeling yields more accurate simulation and timing.

Like in the host simulation model, only the CRAM-ISA interface is described in detail. The other interfaces are simulated by specifying generic parameters of the bus model used in the host simulation model. Other generics in the controller model include the sizes (depths) of the instruction FIFO, the read/write buffers and the control store, as well as the size of the CRAM data and address buses.

#### 6.7.5 CRAM PEs and RAM

The simulation model of the CRAM chips include the low-level hardware description of the PE architecture and the CRAM external interface. Other features of CRAM that relate to its computational nature (such as the bus-tie and shift operation) are also modeled based on how they connect and function in hardware. On the other hand, the memory component of CRAM is simply modeled as arrays of PE local memory since the hardware design of the memory is not a principal focus of the CRAM project. A generic number of PEs and memory bits/PE is used to simulate CRAMs of different sizes.

### 6.7.6 Timing Information

This measures the duration of time during specific stages of program execution from the host processor, via the system bus, to the CRAM controller, through the controller instruction execution unit, to the CRAM chip. This information can be used by both hardware and software designers. For example, the hardware designer can decide to adjust the size of the instruction FIFO or change the instruction pipeline scheme by studying the time that is spent filling an empty instruction queue or the time that the host processor has to wait before another CRAM instruction can be transferred to the CRAM controller.

CRAM software tools designers can evaluate the times that the host processor spends executing a specific CRAM C++ library routine and then decide whether to optimize or remove the routine. Applications designers can assess the time that an application takes to run on a CRAM system. Currently, the major timing parameters reported by the simulator include:

- Host Execution Time: The time that the host processor is executing some instructions

while there are no instructions in the CRAM instruction queue, i.e. no parallel host/

CRAM activity.

- Instruction Load Time: The time taken by the host processor to load instructions into an empty CRAM instruction queue. This can be used, among other things, to determine the effect that the system bus transfer rate or the size of the instruction FIFO has on the overall program execution time.

- Microinstruction Load Time: The time that CRAM microinstructions are being loaded into the control store while the CRAM instruction queue is empty. This time is used to study the effect of the control store size as well as the make-up, size and selection of CRAM microroutines. Microinstruction load time does not include the time to load the initial microinstructions since this happens at boot-up during CRAM driver initialization. Therefore for a system with a control store big enough to require no microinstruction refilling, this parameter is always zero.

- Data Access Time: The time that the CRAM buffers are being accessed by the host

processor while the CRAM instruction queue is empty. This time is used to study the

effect of the size and configuration of the CRAM data buffers, as well as how an application data transfer loads and styles affect how fast it runs on a CRAM system.

- Register Access Time: The time that the CRAM memory-mapped registers are being

accessed by the host processor while the CRAM instruction queue is empty.

- Pipeline Fill Time: The time to fill an empty CRAM instruction queue (FIFO⇒IR⇒Pipeline Reg) when an instruction begins executing from the FIFO. This is useful in studying, among other things, the effects of the FIFO size, the instruction

pipeline scheme and depth, and the inability of the host processor and the CRAM library to keep the CRAM instruction queue always full.

- Microinstruction Execution Time: The time taken to execute all CRAM microinstructions of routines invoked in an application. This is the major component of the total execution time of a program, and is calculated by multiplying the total number of microinstructions executed with the controller cycle time.

- Total Execution Time: This is the total time taken to run a program on a CRAM system. It is simply the sum of all the timing parameters described above.

All the timing parameters above accumulate as the program executes, but each can be individually reset at any point in the program or library routine in order to allow timing of specific features of a program or CRAM library routine. Note that most timing parameters are evaluated only when there is no concurrent execution of instructions in the CRAM controller because this is the only time that they contribute to the total execution time of a program. It must also be mentioned that there may be other uses of these parameters other than the ones mentioned here.

### 6.7.7 Debugging Information

The simulator outputs various information that can be used to debug an application, CRAM library routines, microinstruction routines, or even the CRAM software tools themselves. The main debug information includes:

• CRAM Memory Image: This gives the state, in binary format, of the local memory of each PE. The image is displayed with each PE and its local memory forming a single column of the memory array. The memory image can be displayed at any point in the application code or CRAM library routine, and the number of memory rows to be displayed can be specified. This, together with the fact that memory rows allocated to CRAM variables are grouped and separated from others, allows that a malfunctioning microroutine, library routine or part of an application code be debugged by simply looking at how they actually update the CRAM variables they are supposed to affect.

- Microinstruction Execution: As each microinstruction is being executed, its 32 bits, plus the resulting status of the CRAM address, data, and control buses are displayed.

This may be used to debug microroutines or the simulation model of the controller.

- Assembly Code Listing: This lists the CRAM assembly code as the program executes. This feature is actually incorporated into the CRAM compiler and is activated using a #define statement. It may be used to debug CRAM C++ library routines.

- **Bus Transfers:** This displays the address and data of transfers between the host and the CRAM system.

#### 6.7.8 Program Execution Statistics

Apart from timing and debugging information, a few statistics are reported by the simulator during program execution. These include:

- Number of Specific Instructions: Specific assembly code instructions may be counted. Typically, these are instructions used to update CRAM controller registers, such as LDWLEN and LDAXn. Such information may be used to optimize microroutines, the architecture of the controller, and the formats of both macroinstructions and microinstructions.