# System Design for a Computational-RAM Logic-In-Memory Parallel-Processing Machine

by

Peter M. Nyasulu, B.Sc., M.Eng.

A thesis submitted to the

Faculty of Graduate Studies and Research

in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy

Ottawa-Carleton Institute for Electrical and Computer Engineering,

Department of Electronics,

Faculty of Engineering,

Carleton University,

Ottawa, Ontario, Canada

May, 1999

© Peter M. Nyasulu, 1999

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your Sie Votre référence

Our lile Notre reférence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-42803-6

# The undersigned recommend to the Faculty of Graduate Studies and Research acceptance of this thesis

"System Design for a Computational-RAM Logic-in-Memory

Parallel-Processing Machine"

submitted by Peter M. Nyasulu (B.Sc., M.Eng.) in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Chairman, Department of Electronics

Professor Jim Wight

Thesis Co-supervisor

Thesis Co-supervisor

Professor Ralph Mason

Professor Martin Snelgrove

External Examiner

Dr. Lluis Paris

MOSAID Technologies Incorporated

Carleton University

May, 1999

## **Abstract**

Integrating several 1-bit processing elements at the sense amplifiers of a standard RAM improves the performance of massively-parallel applications because of the inherent parallelism and high data bandwidth inside the memory chip. However, implementing such a logic-in-memory system on a host computer poses several challenges because of the small bandwidth at the host system buses, and the different data formats used on the two systems. In this thesis, solutions to these system design issues, including control of the processing elements, interface to the host, data transposition, and application programming, are considered.

A minimal-hardware controller provides high utilization of processing elements while using a simple and general-purpose architecture. A buffer-based host interface unit enhances external data transfers, and minimizes the effect of the host on the performance of the logic-in-memory system. A parallel array-based corner-turning scheme reduces the time to convert data between bit-serial and bit-parallel formats. High-level programming tools, implemented with and using the standard C++ language, hide low-level architectural details of the system, allowing software developers and system analysts to concentrate on implementation details.

Two controller prototypes that interface to the PCI and ISA host buses, and one system prototype, with 64 processing elements and implemented as an ISA expansion card, demonstrate working models of this logic-in-memory system. Simulations using systems with a larger number of processing elements show that the logic-in-memory system yields significant performance speedup over uniprocessor systems when executing massively-parallel applications. Comparisons with other logic-in-memory systems and conventional supercomputers show comparable speed while using less and simpler hardware.

## Acknowledgments

I am very grateful to the many people who have contributed to the successful completion of my doctoral studies.

I thank my thesis supervisors, Professor Martin Snelgrove and Professor Ralph Mason, for their guidance and support. I also thank my colleagues, Duncan Elliott, Thinh Le, Christian Cojocaru, Robert Mackenzie, and Philip Lauzon, for their cooperation throughout my research work.

I have also benefited greatly, both academically and financially, from working on the microelectronics bridge camps with Professor John Knight. I am therefore very grateful to him for giving me this opportunity. I also thank Professor Tadeusz Kwasniewski for his support and advice during my early years as a graduate student at Carleton.

I thank the sponsors of my scholarship, the Canadian Commonwealth Scholarship and Fellowship Plan, and acknowledge the help I received from my program managers at Canadian Bureau for International Education and International Council for Canadian Studies.

Studying so far away from home can be very stressful. For this, I am very grateful to the Malawian community in Ottawa and Montreal for the wonderful times we shared together.

I thank my parents and relatives in Malawi for their prayers and love. Most of all I thank my wife and best friend, Stella Nyakasambara, for her unfailing confidence in me, for her patience and love, and for all the help she has provided and all the sacrifices she has made.

# **Table of Contents**

| Abstract |      |        |                                                           |          |

|----------|------|--------|-----------------------------------------------------------|----------|

| Cł       | apt  | er 1:  | Introduction                                              |          |

|          | 1.1  |        | outational RAM                                            |          |

|          | 1.2  |        | cation to Parallel-Processing                             |          |

|          | 1.3  |        | m Design                                                  |          |

|          | 1.4  |        | s Scope                                                   |          |

|          | 1.5  |        | s Contributions                                           |          |

|          | 1.6  |        | s Organization                                            |          |

| Ch       | apte | er 2:  | Logic-In-Memory Systems                                   | o        |

|          | 2.1  |        | uction                                                    |          |

|          | 2.2  | Logic- | -in-Memory Systems                                        | 13       |

|          |      | 2.2.1  |                                                           | 13       |

|          |      | 2.2.2  | Terasys Processor In Memory (PIM) Array                   | 15       |

|          |      | 2.2.3  | MIT Pixel-Parallel Image Processing System                | 16       |

|          |      | 2.2.4  | Intelligent RAM (IRAM)                                    | 18       |

|          |      | 2.2.5  | An Integrated Graphics Accelerator and Frame Buffer       |          |

|          |      | 2.2.6  | A Memory-Based Parallel Processor for Vector Quantization |          |

|          | 2.3  | Other  | Common SIMD Control Path Strategies                       | 20       |

|          |      | 2.3.1  | Hierarchical Controllers                                  | 20       |

|          |      | 2.3.2  | Standard Microprogram Sequencers                          |          |

|          |      | 2.3.3  | High-Performance Processors                               | 21       |

|          | 2.4  | Sumn   | nary                                                      | 22       |

| Ch       | apte | er 3:  | Computational RAM                                         | 23       |

|          | 3.1  | Archit | ecture                                                    | 2.A      |

|          |      | 3.1.1  | RAM with SIMD Processors                                  | 24       |

|          |      | 3.1.2  | Processing Element (PE)                                   | 24       |

|          |      | 3.1.3  | CRAM Computations                                         | 24<br>26 |

|          | 3.2  |        | ypes                                                      | 20       |

|          |      | 3.2.1  | A 64-PE, 128 bits/PE CRAM (C64p128)                       | 0∠<br>20 |

|          |      | -      | ==, -= 0.00.1 = 0.10 m. (OUTP120)                         | ∠٥       |

|          |      | 3.2.2  | A 64-PE, 1 Kbits/PE CRAM (C64p1K)                         | 28       |

|                                           | 3.2.4 A 1024-PE, 16 Kbits/PE CRAM (C1Kp16K)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                           |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 3.3                                       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |

| Chapt                                     | ter 4: CRAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                           |

| 4.1                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |

| 4.2                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38                           |

|                                           | 4.2.1 CRAM-ISA Interface Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39                           |

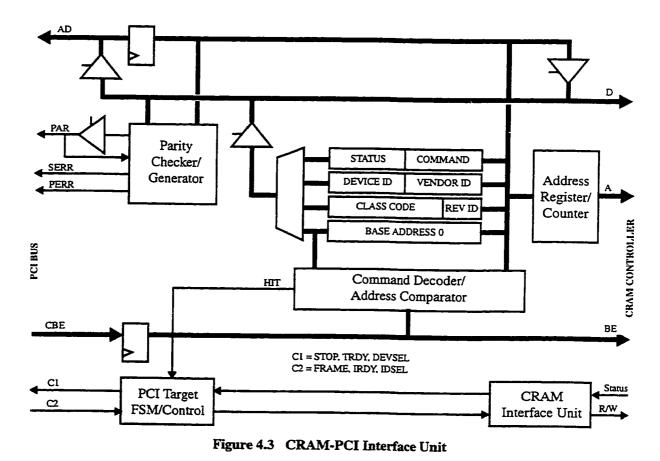

|                                           | 4.2.2 CRAM-PCI Interface Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                           |

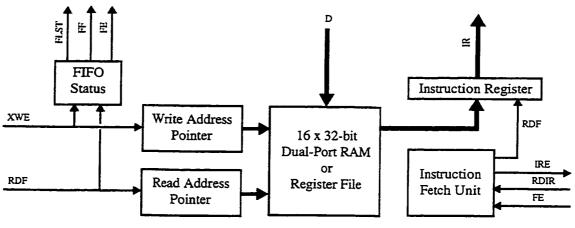

| 4.3                                       | Instruction Queue Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41                           |

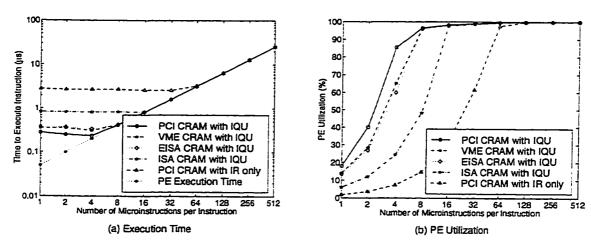

|                                           | 4.3.1 Effect of IQU on Performance of PE Array Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41                           |

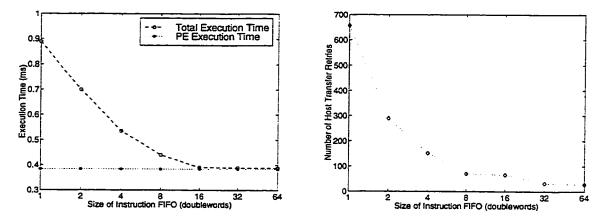

|                                           | 4.3.2 Instruction Fetch Unit and FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46                           |

| 4.4                                       | Instruction Execution Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47                           |

|                                           | 4.4.1 Instruction Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48                           |

|                                           | 4.4.2 Microinstruction Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49                           |

|                                           | 4.4.3 Microprogram Sequencer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                           |

|                                           | 4.4.4 A Simplified Microprogram Sequencer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |

|                                           | 4.4.5 Control Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                              |

|                                           | 4.4.6 Address Unit (ADU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57                           |

| 4.5                                       | Read/Write Buffers and Constant Broadcast Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58                           |

|                                           | 4.5.1 Effect of Read/Write Buffers on Variable Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60                           |

|                                           | 4.5.2 Constant Broadcast Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 64                           |

| 4.6                                       | User-Accessible Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68                           |

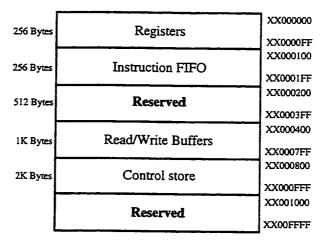

| 4.7                                       | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60                           |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |

| 4.8                                       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |

| 4.8                                       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70                           |

| 4.8                                       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70                           |

| 4.8                                       | Summaryer 5: CRAM System Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70                           |

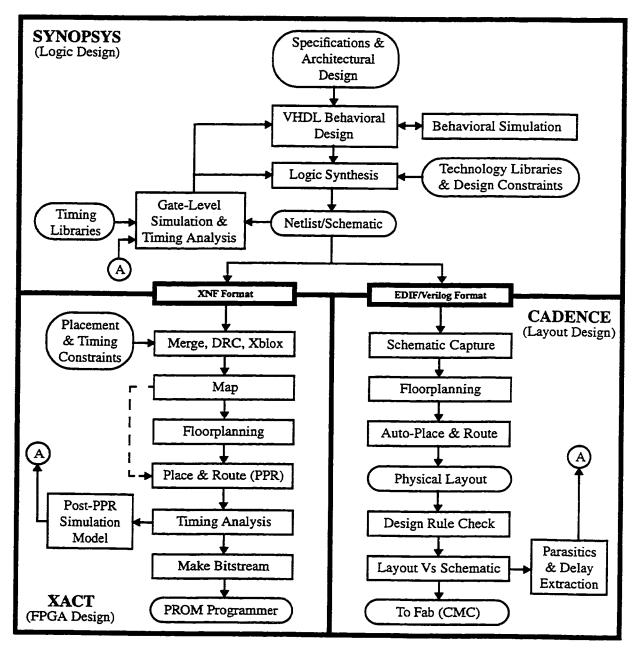

| 4.8 <b>Chapt</b>                          | er 5: CRAM System Implementation  Controller Logic Design and Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 707172                       |

| 4.8 <b>Chapt</b>                          | er 5: CRAM System Implementation  Controller Logic Design and Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 707172                       |

| 4.8 <b>Chapt</b>                          | er 5: CRAM System Implementation  Controller Logic Design and Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70717272                     |

| 4.8 <b>Chapt</b>                          | er 5: CRAM System Implementation  Controller Logic Design and Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7071727272                   |

| 4.8 <b>Chapt</b>                          | er 5: CRAM System Implementation  Controller Logic Design and Verification  5.1.1 Design Flow  5.1.2 VHDL Behavioral Description and Simulation  5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation  5.1.4 Xilinx FPGA Design Flow                                                                                                                                                                                                                                                                                                                          | 707172727475                 |

| 4.8<br><b>Chapt</b><br>5.1                | er 5: CRAM System Implementation  Controller Logic Design and Verification  5.1.1 Design Flow  5.1.2 VHDL Behavioral Description and Simulation  5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation  5.1.4 Xilinx FPGA Design Flow  5.1.5 ASIC Layout Design Flow  5.1.6 CRAM System VHDL Simulation Model                                                                                                                                                                                                                                                  | 70717272747576               |

| 4.8 <b>Chapt</b>                          | er 5: CRAM System Implementation  Controller Logic Design and Verification  5.1.1 Design Flow  5.1.2 VHDL Behavioral Description and Simulation  5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation  5.1.4 Xilinx FPGA Design Flow  5.1.5 ASIC Layout Design Flow  5.1.6 CRAM System VHDL Simulation Model                                                                                                                                                                                                                                                  | 70717272747576               |

| 4.8<br><b>Chapt</b><br>5.1                | er 5: CRAM System Implementation  Controller Logic Design and Verification  5.1.1 Design Flow  5.1.2 VHDL Behavioral Description and Simulation  5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation  5.1.4 Xilinx FPGA Design Flow  5.1.5 ASIC Layout Design Flow  5.1.6 CRAM System VHDL Simulation Model  CRAM Controller Implementation and Testing                                                                                                                                                                                                      | 7071727274757676             |

| 4.8<br><b>Chapt</b><br>5.1                | er 5: CRAM System Implementation  Controller Logic Design and Verification  5.1.1 Design Flow  5.1.2 VHDL Behavioral Description and Simulation  5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation  5.1.4 Xilinx FPGA Design Flow  5.1.5 ASIC Layout Design Flow  5.1.6 CRAM System VHDL Simulation Model  CRAM Controller Implementation and Testing  5.2.1 Xilinx Implementation                                                                                                                                                                         | 707172727475767678           |

| 4.8<br><b>Chapt</b><br>5.1                | er 5: CRAM System Implementation  Controller Logic Design and Verification  5.1.1 Design Flow  5.1.2 VHDL Behavioral Description and Simulation  5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation  5.1.4 Xilinx FPGA Design Flow  5.1.5 ASIC Layout Design Flow  5.1.6 CRAM System VHDL Simulation Model  CRAM Controller Implementation and Testing  5.2.1 Xilinx Implementation  5.2.2 ASIC Simulation                                                                                                                                                  | 70717272747576767878         |

| 4.8<br><b>Chapt</b><br>5.1                | er 5: CRAM System Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70717272747576767878         |

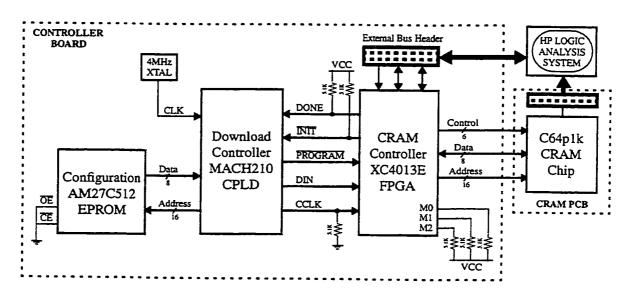

| 4.8 <b>Chapt</b> 5.1                      | er 5: CRAM System Implementation  Controller Logic Design and Verification 5.1.1 Design Flow 5.1.2 VHDL Behavioral Description and Simulation 5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation 5.1.4 Xilinx FPGA Design Flow 5.1.5 ASIC Layout Design Flow 5.1.6 CRAM System VHDL Simulation Model CRAM Controller Implementation and Testing 5.2.1 Xilinx Implementation 5.2.2 ASIC Simulation 5.2.3 CRAM Controller Prototype Testing ISA CRAM System Prototype                                                                                         | 707172727475767678808183     |

| 4.8 <b>Chapt</b> 5.1 5.2                  | er 5: CRAM System Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 707172727475767678808183     |

| 4.8  Chapte 5.1  5.2  5.3 5.4             | er 5: CRAM System Implementation  Controller Logic Design and Verification  5.1.1 Design Flow  5.1.2 VHDL Behavioral Description and Simulation  5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation  5.1.4 Xilinx FPGA Design Flow  5.1.5 ASIC Layout Design Flow  5.1.6 CRAM System VHDL Simulation Model  CRAM Controller Implementation and Testing  5.2.1 Xilinx Implementation  5.2.2 ASIC Simulation  5.2.3 CRAM Controller Prototype Testing  ISA CRAM System Prototype  Summary                                                                     | 7071727275767678808183       |

| 4.8  Chapte 5.1  5.2  5.3 5.4             | er 5: CRAM System Implementation  Controller Logic Design and Verification  5.1.1 Design Flow  5.1.2 VHDL Behavioral Description and Simulation  5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation  5.1.4 Xilinx FPGA Design Flow  5.1.5 ASIC Layout Design Flow  5.1.6 CRAM System VHDL Simulation Model  CRAM Controller Implementation and Testing  5.2.1 Xilinx Implementation  5.2.2 ASIC Simulation  5.2.3 CRAM Controller Prototype Testing  ISA CRAM System Prototype  Summary  Er 6: CRAM System Software Tools                                   | 70717272747576767880818384   |

| 4.8  Chapte 5.1  5.2  5.3 5.4  Chapte     | er 5: CRAM System Implementation  Controller Logic Design and Verification  5.1.1 Design Flow  5.1.2 VHDL Behavioral Description and Simulation  5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation  5.1.4 Xilinx FPGA Design Flow  5.1.5 ASIC Layout Design Flow  5.1.6 CRAM System VHDL Simulation Model  CRAM Controller Implementation and Testing  5.2.1 Xilinx Implementation  5.2.2 ASIC Simulation  5.2.3 CRAM Controller Prototype Testing  ISA CRAM System Prototype  Summary  er 6: CRAM System Software Tools  Introduction                     | 70717272757676787880818183   |

| 4.8  Chapte 5.1  5.2  5.3 5.4  Chapte 6.1 | er 5: CRAM System Implementation  Controller Logic Design and Verification 5.1.1 Design Flow 5.1.2 VHDL Behavioral Description and Simulation 5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation 5.1.4 Xilinx FPGA Design Flow 5.1.5 ASIC Layout Design Flow 5.1.6 CRAM System VHDL Simulation Model CRAM Controller Implementation and Testing 5.2.1 Xilinx Implementation 5.2.2 ASIC Simulation 5.2.3 CRAM Controller Prototype Testing ISA CRAM System Prototype Summary  er 6: CRAM System Software Tools Introduction CRAM Compiler (CRAM C++ Library) | 70717272757676788081838485   |

| 4.8  Chapte 5.1  5.2  5.3 5.4  Chapte 6.1 | er 5: CRAM System Implementation  Controller Logic Design and Verification  5.1.1 Design Flow  5.1.2 VHDL Behavioral Description and Simulation  5.1.3 Logic synthesis, Timing Analysis, and Gate-Level Simulation  5.1.4 Xilinx FPGA Design Flow  5.1.5 ASIC Layout Design Flow  5.1.6 CRAM System VHDL Simulation Model  CRAM Controller Implementation and Testing  5.2.1 Xilinx Implementation  5.2.2 ASIC Simulation  5.2.3 CRAM Controller Prototype Testing  ISA CRAM System Prototype  Summary  er 6: CRAM System Software Tools  Introduction                     | 7071727275767678808183848587 |

|       | 6.2.3 Memory Allocation                              | 91  |

|-------|------------------------------------------------------|-----|

|       | 6.2.4 Overloaded Operators                           | 92  |

|       | 6.2.5 Library Functions                              |     |

|       | 6.2.6 Data-Parallel Conditional Statements           | 94  |

|       | 6.2.7 Operations with Scalar Constants               |     |

|       | 6.2.8 Operand Extension                              |     |

|       | 6.2.9 Support Classes                                | 97  |

|       | 6.2.10 CRAM System Objects and Their Initialization  | 99  |

| 6.3   | Corner-Turning: Host Access of CRAM Variables        | 100 |

|       | 6.3.1 Host-Based Data Transposition                  |     |

|       | 6.3.2 Parallel Array-Based Data Transposition        |     |

|       | 6.3.3 Effect on Performance                          |     |

| 6.4   | CRAM Assembler                                       | 107 |

|       | 6.4.1 Introduction                                   | 107 |

|       | 6.4.2 CRAM Assembly Language                         | 108 |

|       | 6.4.3 Using cvar Addresses and C++ Integer Variables | 109 |

| 6.5   | CRAM Microcode Assembler                             | 110 |

| 6.6   | O                                                    | 110 |

| 6.7   | CRAM C++ Simulator                                   | 113 |

|       | 6.7.1 Introduction                                   |     |

|       | 6.7.2 Simulation Model                               | 114 |

|       | 6.7.3 Host Objects                                   | 114 |

|       | 6.7.4 CRAM Controller                                |     |

|       | 6.7.5 CRAM PEs and RAM                               | 116 |

|       | 6.7.6 Timing Information                             | 116 |

|       | 6.7.7 Debugging Information                          |     |

|       | 6.7.8 Program Execution Statistics                   | 119 |

| 6.8   | Summary                                              | 120 |

|       |                                                      |     |

| Chapt | er 7: Applications and Performance Analysis          | 121 |

| 7.1   | Analysis Methodology and Parameters                  | 122 |

| 7.2   | Basic Arithmetic, Logic and Memory Operations        | 123 |

| 7.3   | Low-Level Image Processing                           |     |

|       | 7.3.1 Brightness Adjustment                          | 127 |

|       | 7.3.2 Spatial Average Low-Pass Filtering             | 127 |

|       | 7.3.3 Edge Detection and Enhancement                 | 130 |

|       | 7.3.4 Segmentation                                   | 131 |

| 7.4   | Database Applications                                | 132 |

|       | 7.4.1 Basic Searches                                 | 133 |

|       | 7.4.2 Least Mean Squared (LMS) Match                 | 134 |

| 7.5   | Image and Video Compression                          | 135 |

|       | 7.5.1 Vector Quantization                            | 135 |

|       | 7.5.2 MPEG-2 Motion Estimation                       | 138 |

| 7.6   | Performance Analysis                                 | 141 |

|       | 7.6.1 Applications Performance Summary               | 141 |

|       | 7.6.2 Controller and System Performance              | 142 |

|       | -                                                    |     |

|        | 7.6.3 Degree of Parallelism                              | 145 |

|--------|----------------------------------------------------------|-----|

|        | 7.6.4 Comparison with other SIMD Systems                 |     |

| 7.7    | <del>-</del>                                             |     |

| Chapt  | er 8: Conclusions and Future Work                        | 150 |

| 8.1    | Summary                                                  | 150 |

| 8.2    | Future Work                                              |     |

|        | 8.2.1 An On-Chip Controller and a MIMD-SIMD CRAM System. |     |

|        | 8.2.2 A Pipelined Constant-Sensitive PE                  |     |

|        | 8.2.3 Other Work                                         |     |

| Refere | ences                                                    | 155 |

| Appen  | dix A: CRAM Controller Architectural Details             | 159 |

| Appen  | dix B: CRAM System PCBs and Pinouts                      | 166 |

| Appen  | dix C: CRAM Software Details                             | 168 |

| Appen  | dix D: Applications Source Code                          | 173 |

# **List of Figures**

| Figure 1.1:  | CRAM Architecture and Processing Element                             |                      |

|--------------|----------------------------------------------------------------------|----------------------|

| Figure 1.2:  | Implementation of Image Inversion on CRAM                            |                      |

| Figure 1.3:  | CRAM in a Typical Computer System                                    |                      |

| Figure 2.1:  | Memory Bandwidth in a Computer System                                | 1                    |

| Figure 2.2:  | Integrated Memory Array Processor Configuration                      |                      |

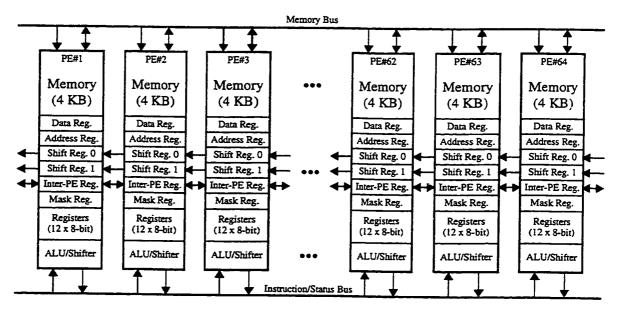

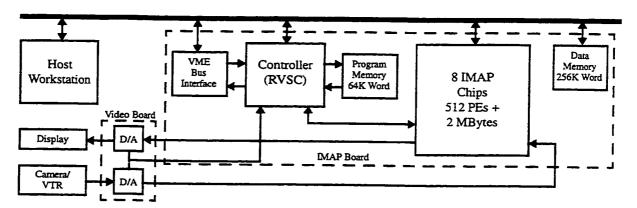

| Figure 2.3:  | RVS-2 Configuration                                                  |                      |

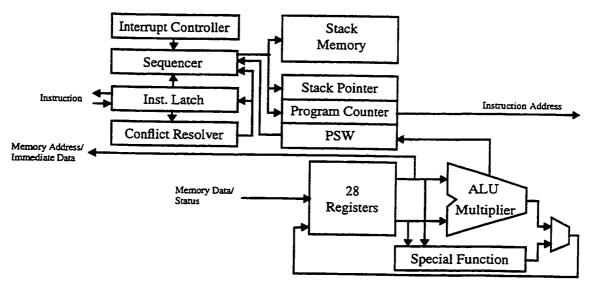

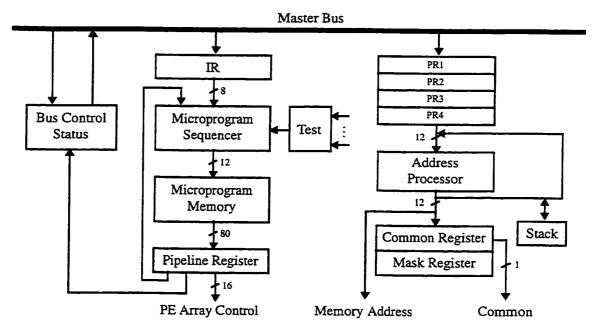

| Figure 2.4:  | RVS-2 Controller (RVSC)                                              | 14                   |

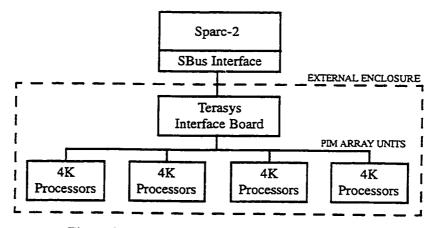

| Figure 2.5:  | A 16K Processor Terasys Workstation                                  |                      |

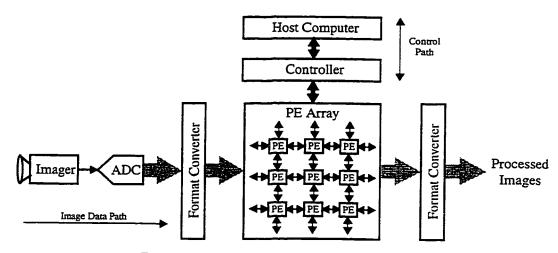

| Figure 2.6:  | MIT Image Processing System                                          |                      |

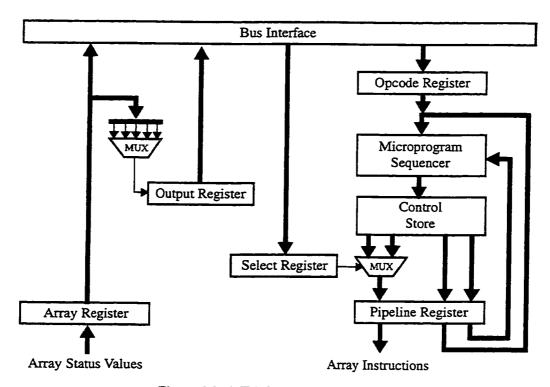

| Figure 2.7:  | MIT Controller Architecture                                          | 17                   |

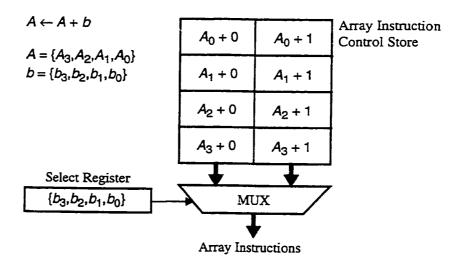

| Figure 2.8:  | Instruction Selection                                                |                      |

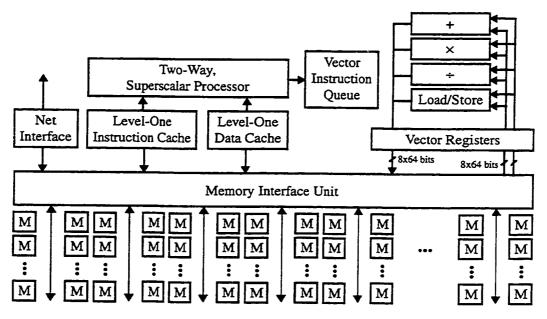

| Figure 2.9:  | Organization of an IRAM Vector Processor                             | 18                   |

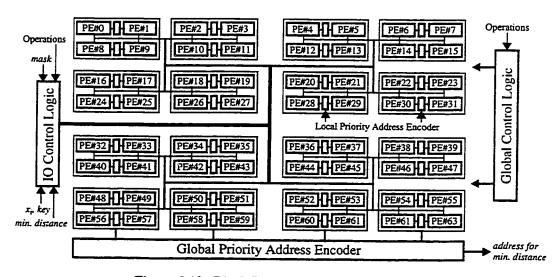

| Figure 2.10: | Block Diagram of the FMPP-VQ64                                       | 10                   |

| Figure 2.11: | VASTOR Controller Hierarchy                                          | 20                   |

| Figure 2.12: | LUCAS Control Unit                                                   | 21                   |

| Figure 3.1:  | CRAM Architecture                                                    | 24                   |

| Figure 3.2:  | Baseline Processing Element                                          | 25                   |

| Figure 3.3:  | Extended Processing Element                                          | 25                   |

| Figure 3.4:  | Setting PE Opcodes (TTOP and COP)                                    | 20                   |

| Figure 3.5:  | PE 4-bit Addition                                                    | 27                   |

| Figure 3.6:  | PE Cycle External Timing                                             | 20                   |

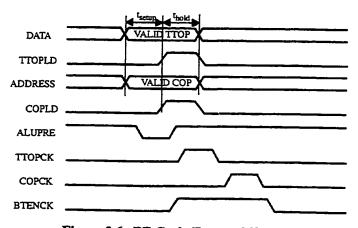

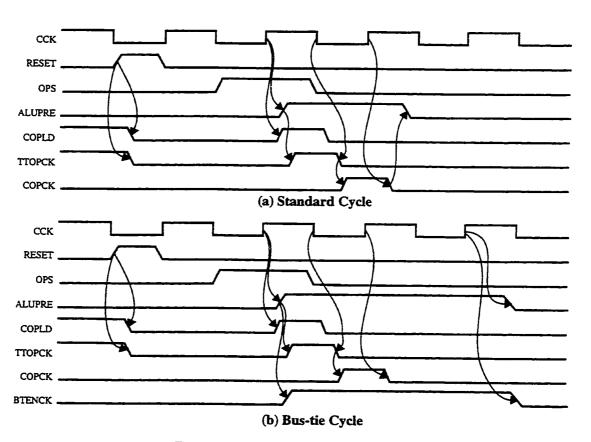

| Figure 3.7:  | PE Cycle Internal Timing                                             | 30                   |

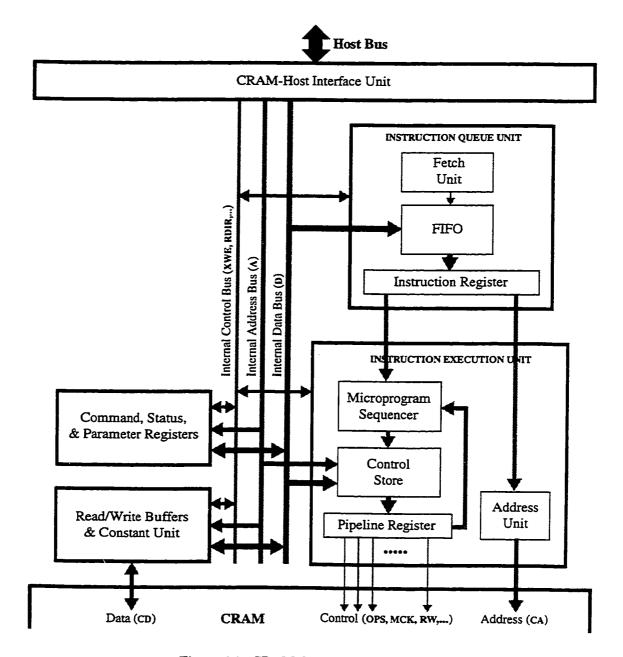

| Figure 4.1:  | CRAM Controller Architecture                                         | 30                   |

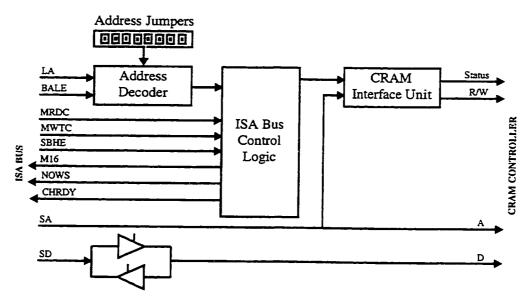

| Figure 4.2:  | CRAM-ISA Interface Unit                                              | 30                   |

| Figure 4.3:  | CRAM-PCI Interface Unit                                              | ود<br>۸۵             |

| Figure 4.4:  | Instruction Queue Unit                                               | <del>.4</del> 0      |

| Figure 4.5:  | Effect of IQU on Controller Performance                              | <del></del>          |

| Figure 4.6:  | Effect of FIFO Size on Performance                                   | <del>. 17</del>      |

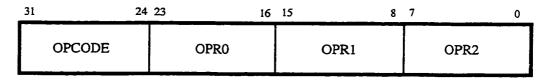

| Figure 4.7:  | instruction Format                                                   | +/<br>∧Q             |

| Figure 4.8:  | Microinstruction Word                                                | <del>۲۰۰۰</del> ۰۰۰۰ |

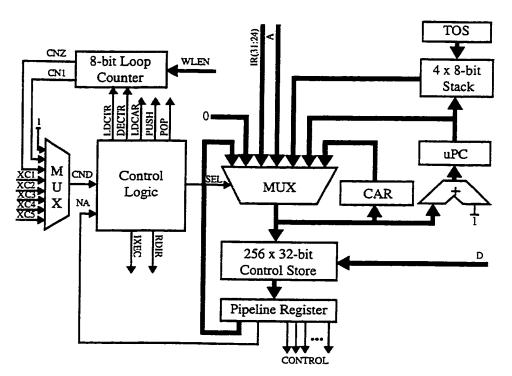

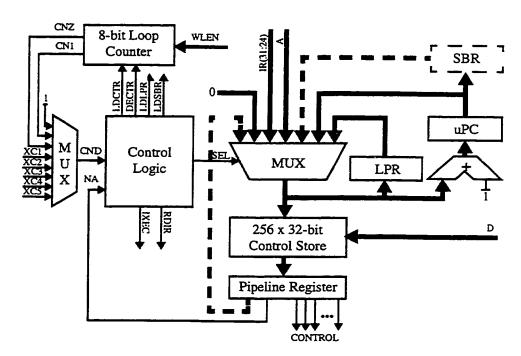

| Figure 4.9:  | Microprogram Sequencer                                               | 43<br>51             |

|              | A Simplified Microprogram Sequencer                                  | 51                   |

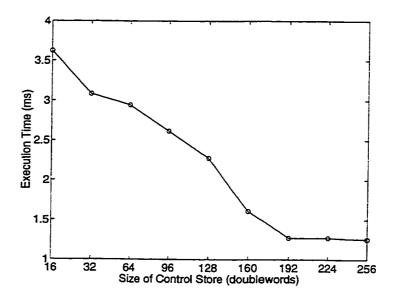

| Figure 4.11: | Effect of Control Store Size on Performance                          | 55<br>56             |

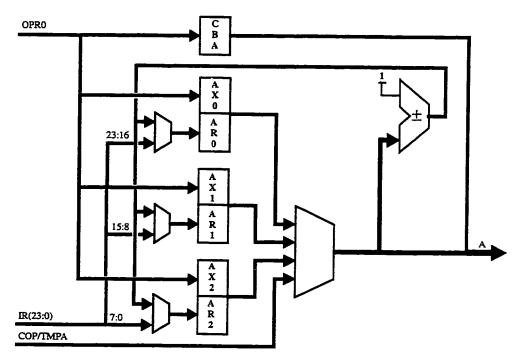

| Figure 4.12: | Address unit                                                         | 50<br>50             |

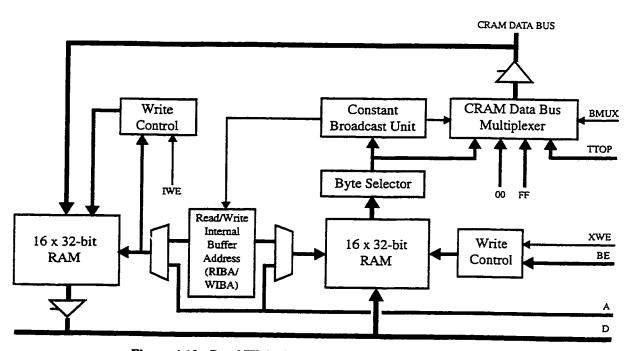

| Figure 4.13: | Read/Write Buffer and Constant Broadcast Unit                        | o                    |

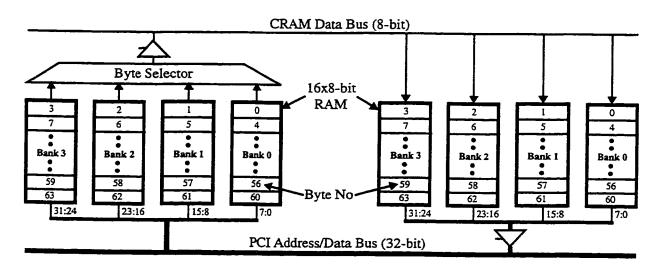

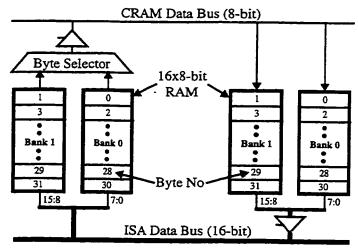

| Figure 4.14: | Data Buffers Organization                                            | رد<br>60             |

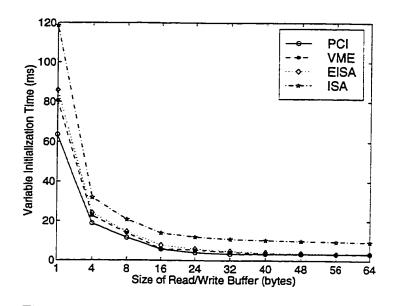

| Figure 4.15: | Effect of R/W Buffers on Variable Initialization                     | 60                   |

| Figure 4.16: | Constant Broadcast Unit                                              | 05                   |

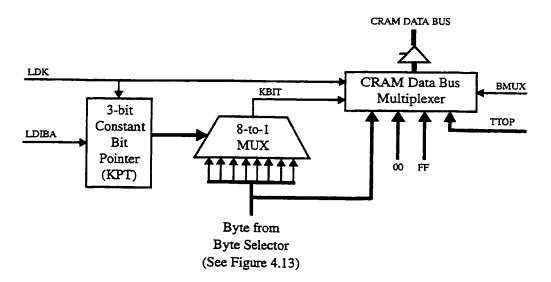

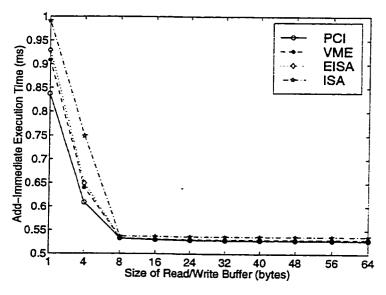

| Figure 4.17: | Effect of Buffer and Constant Unit on Operate-Immediate Instructions | UJ                   |

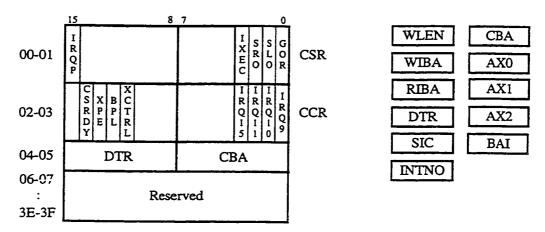

| Figure 4.18: | User-Accessible Registers                                            | 0/                   |

| Figure 4.19: | CRAM Controller Memory Map                                           | 09                   |

| Figure 5.1:  | Design Flow                                                          | 69<br>73             |

| _            | U                                                                    | / ~                  |

| Figure 5.2:  | CRAM System VHDL Simulation Model                           | 77  |

|--------------|-------------------------------------------------------------|-----|

| Figure 5.3:  | CRAM Controller Test Fixture                                |     |

| Figure 5.4:  | CRAM System ISA Card                                        |     |

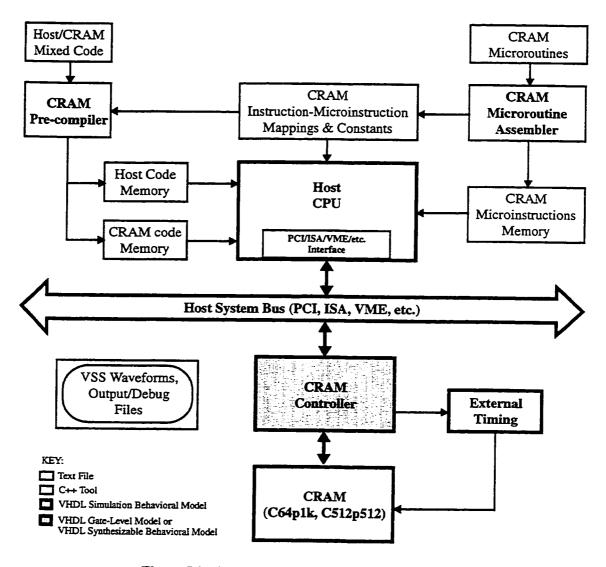

| Figure 6.1:  | CRAM System Software Tools                                  |     |

| Figure 6.2:  | Definitions of CRAM Data Types                              | 88  |

| Figure 6.3:  | Host Corner-Turning                                         |     |

| Figure 6.4:  | Parallel Array-Based Data Transposition                     | 103 |

| Figure 6.5:  | Array-Based vs. Host-Based Transposition                    | 105 |

| Figure 6.6:  | Transposing N-Byte Variables                                | 106 |

| Figure 6.7:  | Data Transpose Time as Percentage of Total I/O Overhead     | 107 |

| Figure 6.8:  | Grouping of Microroutines                                   | 111 |

| Figure 6.9:  | CRAM C++ Simulation Model                                   |     |

| Figure 7.1:  | Effect of Degree of Parallelism on Basic Operations         | 124 |

| Figure 7.2:  | Effect of Operand Size on Basic Operations                  | 125 |

| Figure 7.3:  | Computing in a 3 x 3 Pixel Neighborhood                     | 129 |

| Figure 7.4:  | The Laplacian Edge Detection Operator                       | 130 |

| Figure 7.5:  | CRAM Implementation of Vector Quantization                  | 137 |

| Figure 7.6:  | Motion Estimation                                           | 138 |

| Figure 7.7:  | CRAM Implementation of Motion Estimation                    | 140 |

| Figure 7.8:  | Effect of Controller on Applications Execution Times        | 143 |

| Figure 7.9:  | Effect of Degree of Parallelism on Applications Performance | 145 |

| Figure 7.10: | CRAM Speedup for Small Number of PEs                        | 146 |

| Figure 8.1:  | A MIMD-SIMD CRAM System                                     | 153 |

| Figure A.1:  | PCI Device's Configuration Header                           | 162 |

| Figure B.1:  | ISA CRAM System PCB Layout                                  | 166 |

# **List of Tables**

| Table 4.1:  | Percentage of Short-Sequence Instructions                                      | 45  |

|-------------|--------------------------------------------------------------------------------|-----|

| Table 4.2:  | Minimum Buffer Size for $T_{exe} \ge T_{xload}$ during Variable Initialization |     |

| Table 4.3:  | CRAM Parameter Registers                                                       | 68  |

| Table 5.1:  | CRAM Controller FPGA Device Utilization                                        | 79  |

| Table 5.2:  | CRAM Controller Functional Blocks FPGA Utilization                             |     |

| Table 5.3:  | Area of CRAM Controller in TSMC 0.35 mm Technology                             |     |

| Table 6.1:  | CRAM C++ Operators                                                             | 92  |

| Table 6.2:  | CRAM Library Functions                                                         |     |

| Table 6.3:  | Optimizations for Operations with Constants                                    | 96  |

| Table 6.4:  | Instruction Groups                                                             | 112 |

| Table 7.1:  | CRAM Basic Operations                                                          | 123 |

| Table 7.2:  | Performance of Basic Operations                                                | 124 |

| Table 7.3:  | Performance of Basic Searches                                                  | 133 |

| Table 7.4:  | Applications Performance Summary                                               |     |

| Table 7.5:  | Controller and System Performance                                              | 144 |

| Table 7.6:  | System Comparisons                                                             | 148 |

| Table A.1:  | Next Address Instructions                                                      | 159 |

| Table A.2:  | Microsequencer Conditions                                                      |     |

| Table A.3:  | CRAM Functions                                                                 | 160 |

| Table A.4:  | CRAM Controller Instructions                                                   | 160 |

| Table A.5:  | Auxiliary Controller Instructions                                              |     |

| Table A.6:  | Command Register                                                               | 161 |

| Table A.7:  | Status Register                                                                | 162 |

| Table A.8:  | CRAM PCI Command Registers                                                     |     |

| Table A.9:  | CRAM PCI Status Register                                                       | 164 |

| Table A.10: | CRAM PCI Base Address Register 0                                               | 165 |

| Table A.11: | PCI Command Types                                                              | 165 |

|             |                                                                                |     |

## **List of Abbreviations**

ACU .....Array Control Unit ALU .....Arithmetic Logic Unit ASIC .....Application-Specific Integrated Circuit BiCMOS ......Bipolar Complementary Metal Oxide Semiconductor BPE ......Baseline Processing Element CAD ......Computer-Aided Design CAM .....Content-Addressable Memory CASM ......CRAM Assembler CD.....Compact Disc CLB.....Configurable Logic Block CMASM......CRAM Microcode Assembler CMC.....Canadian Microelectronics Corporation CMOS ......Complementary Metal Oxide Semiconductor COP.....Control Opcode CPLD .....Complex Programmable Logic Device CPU.....Central Processing Unit CRAM.....Computational Random Access Memory DRAM......Dynamic Random Access Memory DRC ......Design Rule Check EDIF..... Electronic Design Interchange Format EISA.....Extended Industry Standard Architecture EPROM.....Erasable Programmable Read-Only Memory FIFO.....First In First Out FIR .....Finite Impulse Response FPGA .....Field Programmable Gate Array FSM .....Finite State Machine GIPS.....Giga Instructions Per Second IMAP.....Integrated Memory Array Processor

| ICIntegrated Circuit                                 |

|------------------------------------------------------|

| IO (I/O)Input/Output                                 |

| IOBInput/Output Block                                |

| IQUInstruction Queue Unit                            |

| IRInstruction Register                               |

| IRAMIntelligent Random Access Memory                 |

| ISAIndustry Standard Architecture                    |

| LMSLeast Means Squared                               |

| LSILarge Scale Integration                           |

| LVSLayout Versus Schematic                           |

| MAEMean Absolute Error                               |

| MCKMemory Clock                                      |

| MIMDMultiple Instruction Multiple Data               |

| MIPSMillion Instructions Per Second                  |

| MPEGMoving Picture Expert Group                      |

| MPPMassively Parallel Processing/Processor           |

| MSEMean Squared Error                                |

| MUXMultiplexer                                       |

| n-D $n$ -dimensional ( $n = 1, 2, 3,$ )              |

| NNSNearest Neighbor Search                           |

| OPSOperate Strobe                                    |

| PCPersonal Computer                                  |

| PCBPrinted Circuit Board                             |

| PCIPeripheral Component Interconnect                 |

| PEProcessing Element                                 |

| PIMProcessor In Memory                               |

| PIPRAMParallel Image Processing Random Access memory |

| PPRPartition, Place and Route                        |

| PROMProgrammable Read-Only Memory                    |

| RAMRandom Access Memory                              |

| RegRegister                                          |

RISC.....Reduced Instruction Set Computer ROM.....Read-Only Memory RTL ......Register Transfer Level RW (R/W) .....Read/Write SDF .....Standard Delay Format SSD .....Sum of Squared Differences SIMD.....Single Instruction Multiple Data SRAM .....Static Random Access Memory TMPA.....Temporary or Mask Address TTOP.....Truth-Table Opcode VHDL .....VHSIC Hardware Description Language VHSIC.....Very High-Speed Integrated Circuit VME.....Versa Module Eurocard VQ.....Vector Quantization VRAM.....Video Random Access Memory VSS .....VHDL System Simulator XNF.....Xilinx Format XPE.....Extended Processing Element **PCI Bus Signals:** AD.....Address/Data bus CBE.....Command and Byte Enable DEVSEL .....Device Select FRAME.....Cycle Frame IDSEL .....Initialization Device Select IRDY.....Initiator Ready

PAR .....Parity

PERR .....Parity Error

SERR .....System Error

TRDY .....Target Ready

STOP.....Stop Transaction

## ISA Bus Signals:

| BALEI | Bus Address Latch Enable   |

|-------|----------------------------|

| CHRDY | Channel Ready              |

| IRQnI | interrupt Request Line n   |

| LA    | Higher address bus (23:17) |

| M16   | Memory 16-bit Chip Select  |

| MRDC  | Memory Read Control        |

| MWTC  | Memory Write Control       |

| NOWS  | No Wait State              |

| SA    | Lower address bus (19:0)   |

| SBHES | ystem Byte High Enable     |

| SD    | Data bus                   |

|       |                            |

## Chapter 1

## Introduction

The idea of merging logic and memory on a single chip was conceived as a correction measure for the wide performance gap between the CPU (microprocessor) and its main memory (DRAM) [1]. Traditionally, microprocessors and DRAM are fabricated on totally different technology processes. Microprocessor fabrication lines are usually optimized to yield fast logic, whereas DRAM processes are designed to reduce leakage current and increase cell density. This has resulted in a processor-memory performance gap that increases by more than 50% every year [2]. While a number of solutions, such as sophisticated cache schemes and pipelined processors, have been used to correct this gap, these have not been totally effective and the processor-memory performance gap continues to be a major obstacle to improved computer system performance. In the continuing effort to improve system performance, some recent research work has concentrated on equipping standard memories with some processing power. The primary objective of these logic-in-memory or processing-in-memory systems is to utilize the high data bandwidth and inherent parallelism that is available inside the memory chip. This not only improves system performance, but also improves power consumption and in some cases reduces system cost.

Computational RAM (CRAM) is one of the pioneering research projects in logic-inmemory systems. The following sections give a brief overview of CRAM, and outlines the scope, contributions and organization of this thesis.

#### 1.1 Computational RAM

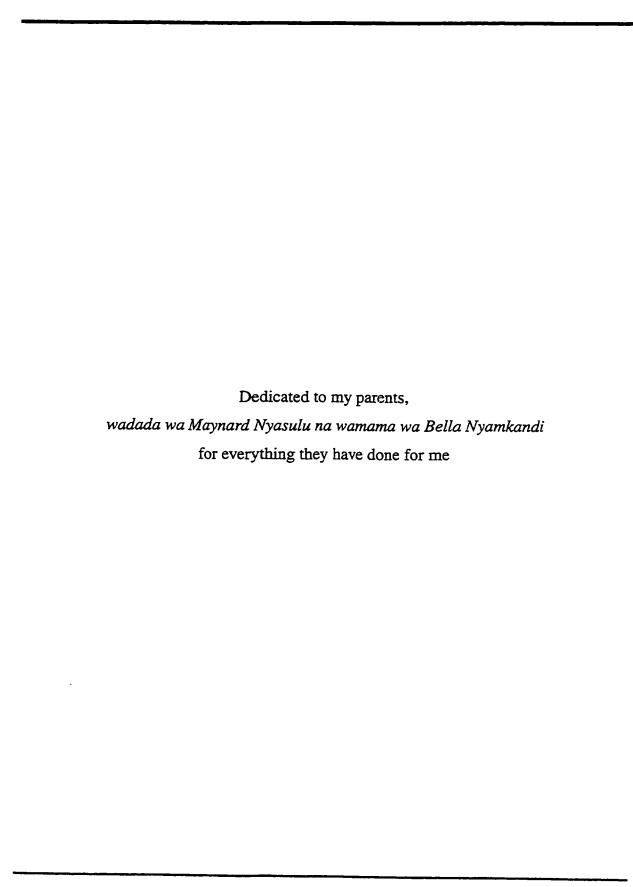

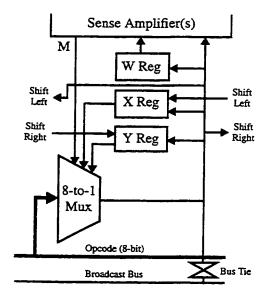

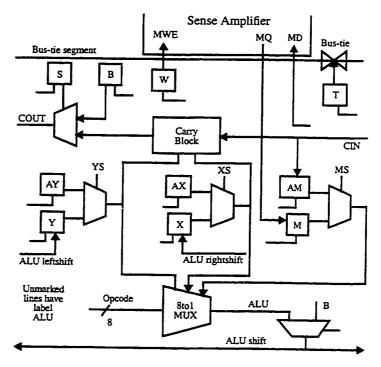

CRAM is a SIMD-memory hybrid in which very simple 1-bit processing elements (PEs) are integrated at the sense amplifiers of a standard RAM [3]. CRAM is designed to increase the speed of executing massively-parallel applications by utilizing the high bandwidth available at the sense amplifiers. Several PEs have access to the data at the sense amplifiers and operate on it without the need to read the data out of the RAM and transmit it over long buses to the processor. This improves performance and reduces power consumption. Figure 1.1 shows the architecture of CRAM and the 1-bit PE.

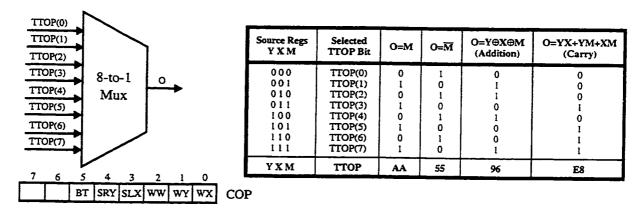

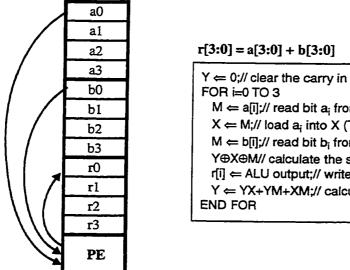

The computational logic of a PE consists of an 8-to-1 multiplexer and 3 registers (Y, X, M). The PE computes the result of an operation by using the 3 bits from the registers to select any one bit of the 8-bit instruction. Therefore, a PE instruction is simply the multiplexer truth table output for all 8 possible register combinations for that particular operation. For example, to have a PE result of '1', the instruction is set to 0xFF so that any combination of Y-X-M selects '1' as the output of the multiplexer. The W register is used for conditional write-back of the result to the local memory of the PE. The shift ports and the bus tie are used for inter-PE communication.

Since the PEs are only 1-bit wide, a single operation generally requires several instructions. For example, an n-bit addition requires (6n + 1) instructions. However, by making the PEs small, a number of them can be integrated in the pitch of one or a few sense amplifiers in order to increase the degree of computational parallelism.

Figure 1.1 CRAM Architecture and Processing Element

### 1.2 Application to Parallel-Processing

Applications most suited for CRAM, like most massively parallel SIMD machines, are those that have fine grain parallelism and regular communication patterns. Such applications can be found in numerous fields including image processing, databases, video and image compression, digital signal processing, computer-aided design, graphics, and numerical analysis [4], [5], [6], [7]. Specific applications that have been studied for CRAM implementation include image convolution, FIR filters, data mining, fault simulation, and the satisfiability problem [4], as well as general image processing techniques, discrete cosine transform, run-length encoding, scalable and hierarchical vector quantization, and other MPEG-2 algorithms [5]. A few CRAM applications are described in this thesis. These include low-level image processing, basic database applications, vector quantization, and motion estimation.

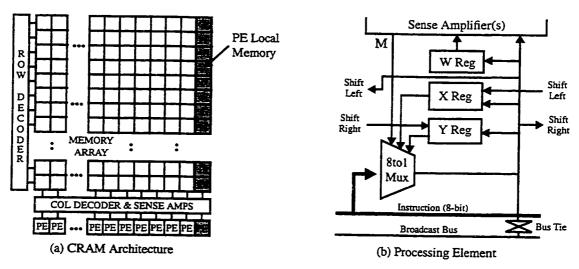

Figure 1.2 illustrates the implementation of image inversion for a 256 x 256 8-bit image on a 64K-PE CRAM (image inversion is useful in the display of medical images and in producing negative prints of images). The image is spread out across the PEs, with one pixel per PE. All PEs perform the inversion operation in parallel. While each PE takes 24 instructions to invert its pixel, i.e. 1.2 µs for a 20 MHz CRAM, the fact that this is done in parallel for all the 65536 pixels still results in high speedup over a high-performance uniprocessor system. For example, a 400 MHz Pentium processor theoretically takes 7.5 ns to invert one pixel (two memory accesses and one computation). But since it has to

Figure 1.2 Implementation of Image Inversion on CRAM

process 64K pixels sequentially, its total execution time of 0.5 ms is more than 400 times slower than that of the CRAM system. Note that this is just a theoretical number used for illustration. As shown later in the thesis, practical speedups may be slightly lower or higher because of CRAM system design issues. Also, a uniprocessor memory access may not be executed in one CPU cycle because memory systems usually have slower cycle times.

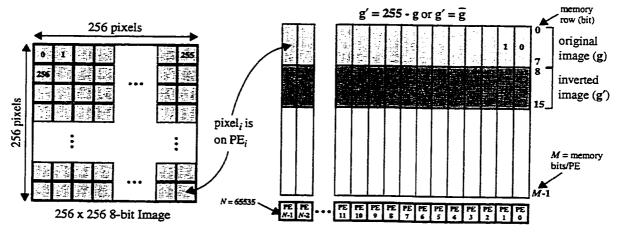

#### 1.3 System Design

As shown later in the thesis, most logic-in-memory systems are designed for specific applications and are implemented mostly on the VME bus or the Sbus. On the other hand, CRAM is designed to be a general-purpose parallel-processing system that can be used on a variety of platforms. One platform specifically targeted in our initial prototypes is the widely-used personal computer (PC) environment. Figure 1.3 shows possible implementations and use of CRAM systems in a typical PC-like environment. The dotted CRAM system is the case where CRAM either replaces or coexists with the standard RAM as the computer main memory or as video RAM. The implementations on the PCI local bus and the expansion buses (shaded boxes) are the ones developed in this work. The main use of the CRAM controller is to allow CRAM application programs to be run from the host computer. The controller acts as a PE array controller as well as an interface to the host bus.

Implementing a CRAM system on a host computer such as the PC poses several challenges. Considering that even a simple operation such as addition requires several instructions to be issued to the 1-bit PEs, the first challenge is to control the PEs and attain high PE utilization while using the small bandwidth of the host buses. Otherwise the PEs would be idle most of the time, thus reducing the overall advantage of CRAM over a uniprocessor system. Second, unlike most SIMD systems that are implemented using several PCBs and housed in large cabinets, a PC-based CRAM system has to be implemented on a single standard-size PC card. This means using as few external components as possible. The third challenge in using CRAM on a standard computer is due to the different data formats used on the two systems. CRAM is bit-serial, while most

conversion or data transposition when data is transferred between the two systems. This difference in data formats also means that programming tools on the host can not be directly used to write programs for CRAM. Therefore, new software tools have to be developed for CRAM, or existing tools on the host have to be modified or enhanced to support CRAM data types. Finally, there is need to minimize any extra CRAM hardware in order to reduce system costs as well as facilitate future integration of all CRAM hardware on a single chip.

Figure 1.3 CRAM in a Typical Computer System

## 1.4 Thesis Scope

The scope of this thesis encompasses the study of the system design challenges outlined in Section 1.3. The thesis argues and proves that even with the limitations imposed by the host computer, i.e. small bandwidth, bit-parallel data format, and constrained PCB size, it is still possible to build a minimal-hardware and general-purpose CRAM system that yields significant performance speedup over conventional uniprocessor systems when executing massively-parallel applications. The main system design issues covered in this work include the following:

- Design and implementation of a minimal-hardware and high-performance PE controller that also enhances the use of CRAM as a general-purpose parallel-processing system.

- Design and implementation of a CRAM-host interface that minimizes the effect of the host on the performance of a CRAM system. This allows the implementation of CRAM on a wide variety of platforms.

- Design and implementation of data transposition schemes that offer reasonable compromise between area/hardware and performance.

- Implementation of a CRAM system prototype to demonstrate a working model of the whole CRAM concept.

- Analysis of the general implementation and performance of CRAM applications.

- Analysis of the effect of different CRAM architectural features on the overall performance of a CRAM system.

A secondary objective of this thesis is to develop a set of high-level software tools that can be used for application programming, system simulation, architectural analysis, and other CRAM development work. Since the CRAM prototypes implemented so far are very small, almost all the analysis work reported in this thesis is based on simulations using the C++ CRAM system simulator developed in this work.

#### 1.5 Thesis Contributions

This thesis contributes to the general system design, implementation, and analysis of a logic-in-memory parallel-processing machine. The major design contributions include:

- A novel constant broadcast unit that improves the performance of operations with constant values by more than 35%. It also simplifies the use of variable-size constants, and reduces the size of the control store, thus reducing the area of the CRAM controller.

- A FIFO-based instruction queue that improves the performance of short-sequence instructions by a factor as high as tenfold. It also allows the CRAM controller to approach an ideal PE controller (100% PE utilization) at a small number of microinstructions per instruction. This translates in increased performance for a wider range of applications.

- The use of read/write buffers for data transfers from the host to CRAM that simplifies synchronization, eases electrical and physical loading of the host bus, and may reduce the time of loading data onto CRAM by as much as 80%.

- A new parallel array-based data transposition approach that is more than a hundred times faster than host-based software transposition, and contributes less than 10% of the total I/O overhead for CRAM systems with more than 4K PEs.

- A simple but innovative approach of grouping microroutines that reduces the required size of the microprogram memory by more than 50%. This small size (less than 256 32-bit words) makes an on-chip control store feasible, even in standard ASIC technologies and FPGAs, and hence reduces the number of components on a CRAM PCB.

- A general-purpose architecture for the controller that enhances the use of CRAM as a general-purpose parallel-processing system.

The major implementation contributions include:

- A CRAM C++ library that is used to write CRAM application programs using the standard C++ language and standard C++ compilers.

- A CRAM C++ simulator that can be used by both hardware and software designers to analyze CRAM architectural features as well as the performance of applications.

- Implementation of two controller prototypes and an ISA-based 64-PE CRAM system

prototype to demonstrate working models of the CRAM concept.

In terms of system analysis,

- this work demonstrates that using the design features described above minimizes the effect of the host computer on the performance of a CRAM system. This is important for CRAM as a general-purpose system because it means that CRAM can be implemented on a variety of platforms, including slow host systems such as ISA-based computers and embedded systems that use slow microcontrollers.

- It is also shown that even with a bandwidth-limited host, a CRAM system still yields

reasonably high performance for a variety of massively-parallel applications because

of the performance-enhancement features of the CRAM controller.

- Using practical applications, this work highlights architectural bottlenecks of CRAM,

especially the inter-PE communication network.

Finally, the thesis proposes two new CRAM ideas: an on-chip CRAM controller and a MIMD-SIMD CRAM system, and a pipelined constant-sensitive CRAM PE.

### 1.6 Thesis Organization

This chapter has outlined the background, motivation, scope and contributions of this thesis. Chapter 2 outlines the reasons behind logic-in-memory systems and describes work related to CRAM. Chapter 3 summarizes the architectural details of CRAM and lists CRAM prototype chips implemented so far. Chapter 4 to Chapter 7 discuss the primary contributions of this thesis. Chapter 4 describes the architecture of the CRAM controller and its interface to the host processor. Chapter 5 discusses the design, implementation, and testing of CRAM prototypes. Chapter 6 describes the different CRAM system software tools that have been developed in this work. Applications and performance analysis of a CRAM system are described in Chapter 7. Chapter 8 summarizes major accomplishments and suggests ideas for future work.

Appendix A provides architectural and implementation details of the CRAM controller. Appendix B provides PCB layout and pinouts of the CRAM system prototypes. Details of CRAM software tools are described in Appendix C. Appendix D lists the C++ source code for all applications described in this thesis.

## Chapter 2

## **Logic-In-Memory Systems**

This chapter discusses the background of logic-in-memory systems, and gives examples of CRAM-related work. Section 2.1 discusses the rationale for logic-in-memory systems and outlines the major advantages of these systems. Section 2.2 presents some of the more advanced and well-known logic-in-memory systems, with emphasis on the architecture and size of the processing elements (PEs), as well as system design issues (such as control of the PEs and the interface to the host). Since most logic-in-memory systems are SIMD systems, a brief review of other common SIMD PE control strategies is also given in Section 2.3. The architecture of CRAM itself is presented in Chapter 3.

#### 2.1 Introduction

The idea of logic-in-memory has been around for years. One of the earliest documented cases is the logic-in-memory computer proposed by Harold Stone [1]. Stone argued that since the cost of components was to become heavily dependent on the number of package pins and not on the chip gate count, it was logical to equip the memory with some processing power so that operations can be performed directly in memory and take advantage of the inherent parallelism. This enhanced logic-in-memory cache would then be used as a high-speed buffer between the CPU and the main memory. It can therefore be seen that much of the initial motivation for a logic-in-memory system was to bridge the speed gap between a CPU and its memory. This holds true even today.

The main reason for the differences in speed between the CPU (microprocessor) and its memory (DRAM) has been due to the fact that different fabrication processes are used for the two. Microprocessor fabrication processes are usually optimized for fast transistors and have many metal layers. This results in fast logic, accelerates communication, and simplifies power distribution. On the other hand, DRAM processes have more polysilicon layers in order to have small memory cells. They also have high threshold voltages and thicker oxides in order to reduce leakage current. This increases the density of the DRAM, and also reduces its refresh rate. Because of these differences in processes, microprocessor performance has been improving at a rate of 60% per year, while DRAM access time has been improving at less than 10% a year [2]. This widening performance gap between the processor and the memory is now the major obstacle to improved computer system performance. Using sophisticated multi-level caches has only partially solved the problem since these caches increase memory latency and also do little to increase memory bandwidth because they (SRAMs) are traditionally constrained by their narrow data bus widths. SRAMs are also very expensive when compared to DRAMs.

One solution to the processor-memory performance gap is to combine logic and memory on the same chip. The complexity of the logic that is merged into memory depends on the desired system performance and cost. On one end, a small number of complex full-featured processors or CPUs are integrated into memory. This allows the logic-in-memory system to perform all computations done by a standard microprocessor.

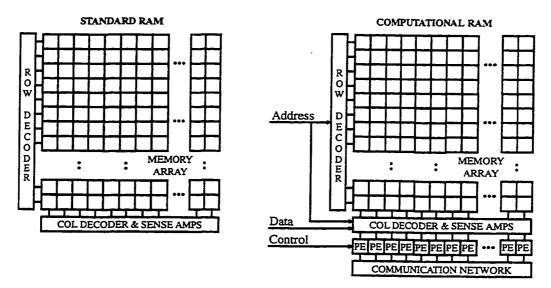

However, this type of system is expensive because of the size of the processors, and it is also difficult to implement a complex logic system in a DRAM process. The other type of logic-in-memory system, such as Computational RAM (CRAM) [3], integrates very simple single-bit processing elements (PEs) at the sense amplifiers of a standard RAM. The PEs add about 5-10% to the area of the RAM, and because of their simplicity, it is easier to implement them even in a DRAM process. Also, since the PEs are small, a big number of them can be integrated in a RAM chip, thus increasing the degree of computational parallelism. The following are advantages of logic-in-memory systems, with particular emphasis on CRAM-type systems:

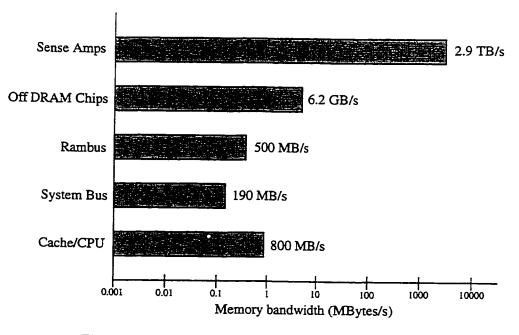

High Memory bandwidth: Typically, the data available at the RAM sense amplifiers is more than a 1000 times the width of the RAM external bus (which is typically 1, 8, 16, or 32 bits wide). Therefore, processing elements integrated at the sense amplifiers can utilize this high bandwidth to speed up the execution of parallel applications. Figure 2.1 shows the bandwidths available at different points in a computer system. This comparison [8] is based on a system with 256 MBytes of 16 Mb, 50ns DRAM chips, and a 100 MHz CPU with a 64-bit bus.

Figure 2.1 Memory Bandwidth in a Computer System

- Lower Power Consumption: Logic-in-memory systems improve power consumption. First, since most of the computations are done on the memory chip, there are fewer external memory accesses which would otherwise consume energy in driving the high-capacitance off-chip buses. Second, in a standard RAM chip, a single memory access drives several hundreds of bitlines even though a few tens of data bits are made available to the external RAM bus. This is an obvious wastage of energy. In a logic-in-memory system that integrates PEs at the RAM sense amplifiers, almost all the data bits driven onto the sense amplifiers are used in the computation, thus improving the efficiency of power consumption. For example, in a comparison done in [9], a 200 MHz Pentium accessing its cache transfers data over 10 cm of 32-bit buses. Assuming a 20 pF capacitance per data bit, and a 3.3 V power supply, this data transfer results in energy consumption of about 110 pJ per data bit. On the other hand, the PE's of an equivalent CRAM system with 16 x 1024b CRAM chips and a 50 ns cycle time, access their data over 5 mm metal lines with a total of about 1 pF per line. This results in power consumption of about 5.5 pJ.

- Reduced Board Size: A logic-in-memory system may result in fewer chips than a

system implemented with discrete RAM and CPU chips. Also, for systems that require

modest computation power but whose board area is precious, such as in portable electronic devices, a single chip with merged logic and memory is more attractive.