## A Robust, Efficient Physical Layer Transport Protocol for Packets

by

### Paul Langner, B.Eng., M.Eng., P.Eng.

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electronics

Carleton University Ottawa, Ontario September, 1999

© copyright 1999, Paul Langner

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre reference

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-48347-9

The undersigned recommend to the Faculty of Graduate Studies and Research acceptance of the thesis,

### "A Robust, Efficient Physical Layer Transport Protocol for Packets"

submitted by

Paul Langner, B.Eng., M.Eng., P.Eng.

in partial fulfilment of the requirements for the degree of Doctor of Philosophy, Engineering.

Chair, Department of Electronics

Thesis Co-supervisor

Thesis Co-supervisor

External Examiner

Carleton University September, 1999

### **Abstract**

While the majority of data transmitted in today's telecommunications networks is packet oriented, there is no robust physical layer framing mechanism designed specifically for packet data. As a result, the packet data must be mapped either into ATM cells and then into a SONET/SDH frame, or encapsulated in PPP, HDLC, and then into SONET/SDH.

In this thesis, the various methods of format synchronization are explored in the context of packet transmission. A novel, packet oriented physical layer framing protocol based on CRC-16 packet boundary delineation is developed that is both robust and efficient. This protocol is then analyzed from a performance analysis perspective. Finally the physical implementation of an integrated circuit containing transmit/receive framers using this protocol and its performance is examined.

# **Acknowledgements**

I wish to express my gratitude to my thesis supervisors, Ralph Mason and Martin Snelgrove (thanks Martin for putting up with me all those years), and to Northern Telecom, Fujitsu, and Lucent for funding me to do my Ph.D. I would also like to thank Subra Dravida, Enrique Valencia-Hernandez, and James Manchester for valuable discussions on the SDL framing and scrambling structure, and Ed Roberts for his unwavering support of SDL. Finally I would like to thank my parents, my father-in-law, and my wife for their support and encouragement over the years.

| Section                                                      | Page  |

|--------------------------------------------------------------|-------|

| 1 Introduction                                               |       |

| 1.1 Background and Objective                                 | 1     |

| 1.2 Thesis Organization                                      | 3     |

| 1.3 Statement of Contribution                                | 4     |

| 2 Packet Transmission Today                                  | 6     |

| 2.1 Introduction                                             | 6     |

| 2.2 Packets                                                  | 6     |

| 2.3 The ATM "Cell Tax"                                       | 10    |

| 2.4 Packet over SONET/SDH (POS)                              | 13    |

| 2.5 Multiprotocol Label Switching (MPLS)                     | 16    |

| 3 Format Synchronization                                     | 17    |

| 3.1 Introduction                                             | 17    |

| 3.2 Digital Frame Boundary Delineation on Point-to-Point Lin | ks 17 |

| 3.3 Synchronous Formats                                      | 18    |

| 3.3.1 Confidence Counters                                    | 23    |

| 3.3.2 Error Correction                                       |       |

| 3.3.3 Other Modifications                                    |       |

| 3.3.4 Parallel Framers                                       |       |

| 3.4 Asynchronous Frames                                      |       |

| 4 Scrambling Overview                                        |       |

| 4.1 Introduction                                             |       |

| 4.2 Scramblers                                               |       |

| 4.3 Self-Synchronizing Scramblers                            |       |

| 4.3.1 Self-Synchronizing Scrambler Issues                    |       |

| 4.3.2 Method of Attack                                       |       |

| 4.4 Independent Scramblers                                   |       |

| 4.4.1 Frame Synchronized                                     |       |

| 4.4.2 Distributed Sampling                                   | 37    |

| Section                                                                                                                                                                                                     | Page                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 4.4.3 Set-Reset                                                                                                                                                                                             |                         |

| 5 Protocol Design                                                                                                                                                                                           | 42                      |

| 5.1 Introduction                                                                                                                                                                                            |                         |

| 5.2 Goals                                                                                                                                                                                                   | 42                      |

| 5.2.1 POS Deficiencies                                                                                                                                                                                      | 42                      |

| 5.2.2 New Protocol Goals                                                                                                                                                                                    |                         |

| 5.3 Protocol Design                                                                                                                                                                                         | 44                      |

| 5.3.1 Robust Framing                                                                                                                                                                                        |                         |

| 5.3.2 Framer and Frame Marker Engineering                                                                                                                                                                   |                         |

| 5.3.3 Parallel Framers                                                                                                                                                                                      |                         |

| 5.3.3.1 Signal Flow Equations from a Transition M<br>5.3.3.2 Examination of Signal Flow Graph Repres<br>5.3.3.3 Matrix Formula for MTTF<br>5.3.3.4 Transition Matrix for N Parallel Framers<br>5.3.3.5 MTTF | entations54<br>56<br>57 |

| 5.3.3.6 MTTF Results                                                                                                                                                                                        |                         |

| 5.3.4 CRC-16                                                                                                                                                                                                |                         |

| 5.3.5 Null Fill                                                                                                                                                                                             | - <del>-</del>          |

| 5.3.6 DC Balance and Transition Density                                                                                                                                                                     |                         |

| 5.3.7 Scrambling                                                                                                                                                                                            | Design 66<br>68<br>69   |

| 5.3.8 OAM Messaging                                                                                                                                                                                         | 70                      |

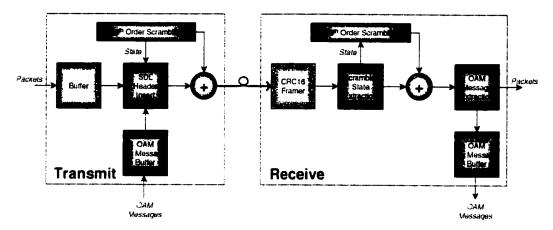

| 5.4 Estimated Performance                                                                                                                                                                                   | 71                      |

| 6 SDL Performance                                                                                                                                                                                           | 73                      |

| 6.1 Introduction                                                                                                                                                                                            | 73                      |

| 6.2 Mean Time to Frame (MTTF)                                                                                                                                                                               | 73                      |

| 6.2.1 Results                                                                                                                                                                                               |                         |

| 6.3 Mean Time to Synchronization (MTTS)                                                                                                                                                                     |                         |

| 6.4 Probability of False Frame (PFF)                                                                                                                                                                        |                         |

| 6.5 Probability of False Synchronization (PFS)                                                                                                                                                              |                         |

| Section                                                                                           | Page                 |

|---------------------------------------------------------------------------------------------------|----------------------|

| 6.6 Probability of Loss of Frame (PLF)                                                            | . 78                 |

| 7 Implementation                                                                                  | .80                  |

| 7.1 Introduction                                                                                  | . 80                 |

| 7.2 Design Specification                                                                          | . 80                 |

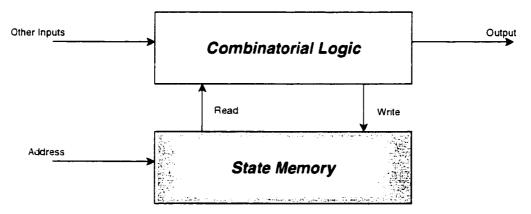

| 7.2.1 State Memory                                                                                | 80                   |

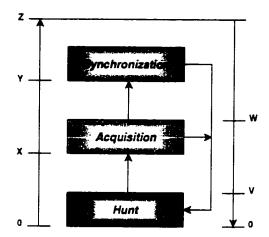

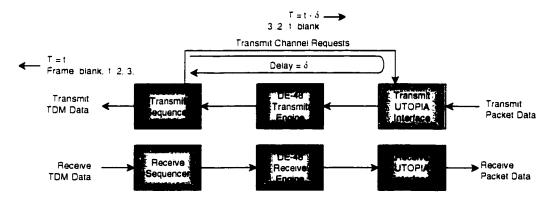

| 7.3 Data Engine Operation                                                                         | . 81                 |

| 7.3.1 Overview                                                                                    |                      |

| 7.4 Implementation Specifics                                                                      |                      |

| 7.4.1 Design Philosophy                                                                           | 84                   |

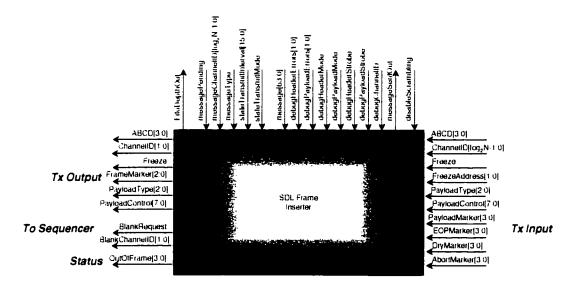

| 7.5 SDL Frame Inserter                                                                            | . 86                 |

| 7.5.1 Interfaces                                                                                  |                      |

| 7.5.3 Transmit Output                                                                             | 87                   |

| 7.5.4 Status Output                                                                               |                      |

| 7.5.5 Sequencer Output                                                                            |                      |

| 7.5.6 Control Interface                                                                           |                      |

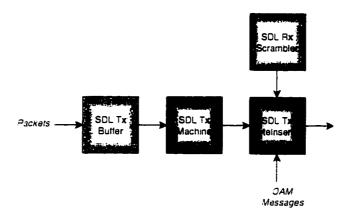

| 7.5.7.1 SDL Tx Buffer 7.5.7.2 SDL Tx Machine 7.5.7.3 SDL Tx Scrambler 7.5.7.4 SDL Tx ByteInserter | 91<br>93<br>95       |

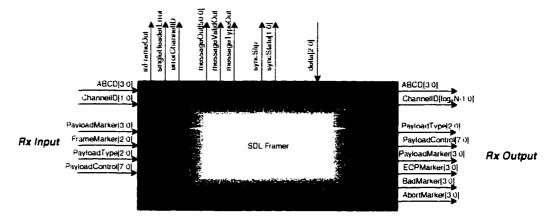

| 7.6 SDL Framer                                                                                    | 96                   |

| 7.6.1 Interfaces                                                                                  |                      |

| 7.6.1.1 Receive Input                                                                             | 96<br>97<br>98       |

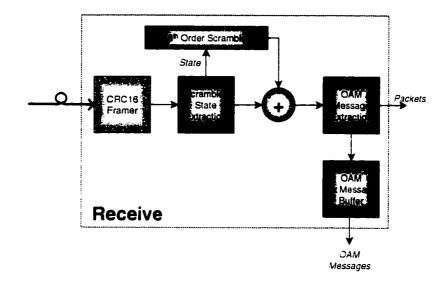

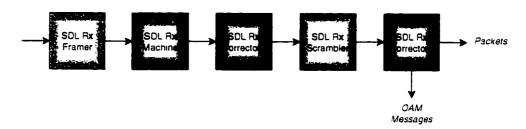

| 7.6.2 SDL Framer Details                                                                          | . 99                 |

| 7.6.2.1 SDL Rx Framer                                                                             | .102<br>.103<br>.104 |

| Section F                                                                  | age        |

|----------------------------------------------------------------------------|------------|

| 8 Results1                                                                 | 06         |

| 8.1 Introduction                                                           | 106        |

| 8.2 Die                                                                    | 106        |

| 8.3 Package                                                                | 107        |

| 8.4 Test Board                                                             | 107        |

| 8.5 Results                                                                | 801        |

| 9 Summary and Suggestions for Future Work                                  | 09         |

| 9.1 Introduction                                                           | 109        |

| 9.2 Summary                                                                | 09         |

| 9.3 Standards Status                                                       | 10         |

| 9.3.1 IETF                                                                 | 10         |

| 9.3.2 ITU                                                                  | 10         |

| 9.3.3 OIF                                                                  |            |

| 9.3.4 10G Ethernet                                                         |            |

| 9.3.5 System I/O                                                           |            |

| 9.4 Future Work                                                            | 11         |

| Appendix A: Examples                                                       | 13         |

| A.1 Examples1                                                              | 13         |

| Appendix B: Derivation of Ones/Zeroes Density and Transitio Equations      |            |

| B.1 Ones/Zeroes Density                                                    | 14         |

| B.2 Transition Density                                                     |            |

| Appendix C: Galois Fields, Linear Feedback Shift Registers, a Cyclic Codes |            |

| C.1 Primitive Polynomials and Finite Fields                                | 19         |

| C.1.1 Galois Fields                                                        | 19         |

| C.1.2 Addition and Multiplication in a Galois field1                       |            |

| C.1.2.1 Vector Representation of $GF(q^m)$                                 | 122<br>123 |

| Section                                                                                                 | Page                    |

|---------------------------------------------------------------------------------------------------------|-------------------------|

| C.1.3 Minimal Polynomials and the Factoring of x <sup>n</sup> - 1 C.2 Linear Feedback Shift Registers   |                         |

| C.2.1 Parallel LFSR Operations                                                                          | . 133                   |

| C.3 Linear Block Codes                                                                                  | . 135                   |

| C.3.1 Cyclic Codes                                                                                      | . 137                   |

| Appendix D: How To Sabotage a POS Link                                                                  | 142                     |

| D.1 The POS Standard                                                                                    | . 142                   |

| D.2 Attacking the x <sup>43</sup> + 1 Scrambler                                                         | . 144                   |

| D.2.1 The SONET/SDH Frame Structure                                                                     | . 147                   |

| D.2.3 Line Spectra                                                                                      | _                       |

| Appendix E: Explanation of Header CRC Transform                                                         | 151                     |

| E.1 Discussion                                                                                          | . 151                   |

| Appendix F: SDL Specification                                                                           | 154                     |

| F.1 Specifications                                                                                      |                         |

| F.1.1 Formats  F.1.2 Special Payloads  F.1.3 Scrambling  F.1.4 Framing  F.1.5 Scrambler Synchronization | . 159<br>. 160<br>. 162 |

| F.1.6 OAM Messages                                                                                      |                         |

| Appendix G: MATLAB MTTF Program                                                                         |                         |

| G.1 Program                                                                                             | . 167                   |

| Appendix H: DC Balanced Barker Program                                                                  | 170                     |

| H.1 Program                                                                                             |                         |

| Appendix I: TDAT042G5 Product Brief                                                                     |                         |

| Section                                      | Page |

|----------------------------------------------|------|

| Appendix J: SDL IETF Draft                   | 178  |

| J.1 Draft                                    | 178  |

| Appendix K: SDL Packet over Fiber IETF Draft | 205  |

| K.1 Draft                                    | 205  |

| References                                   | 230  |

# List of Figures

| Figure                                                                                            | Page      |

|---------------------------------------------------------------------------------------------------|-----------|

| Figure 2.1: TCP packet format with IPv4 header                                                    | 7         |

| Figure 2.2: UDP packet format with IPv4 header                                                    | 7         |

| Figure 2.3: Internet packet size probability distribution                                         | 8         |

| Figure 2.4: Internet packet size distribution after major mode                                    | removal 9 |

| Figure 2.5: ATM cell structure                                                                    | 11        |

| Figure 2.6: RFC1483 AAL-5 Classical IP Mapping                                                    | 11        |

| Figure 2.7: RFC1662 PPP encapsulation                                                             | 13        |

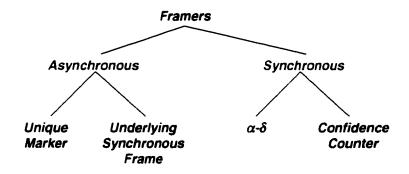

| Figure 3.1: Taxonomy of framers                                                                   | 18        |

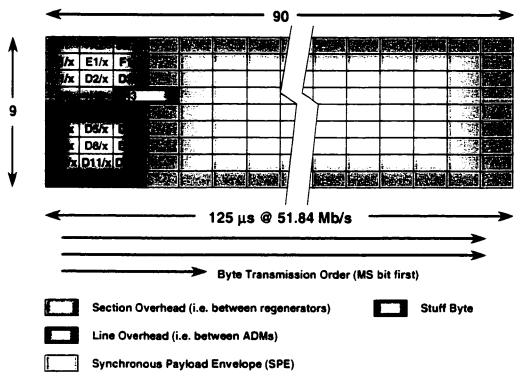

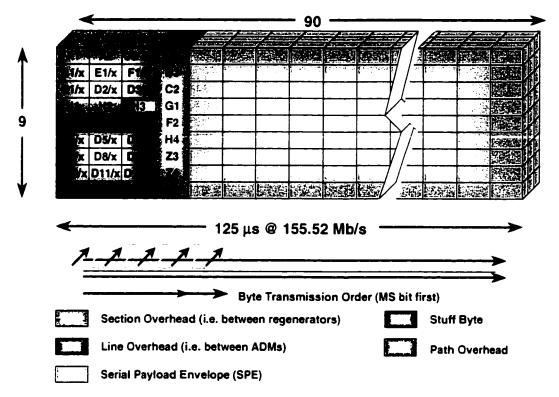

| Figure 3.2: SONET STS-1 frame structure                                                           | 19        |

| Figure 3.3: Standard $\alpha$ - $\delta$ framer                                                   | 20        |

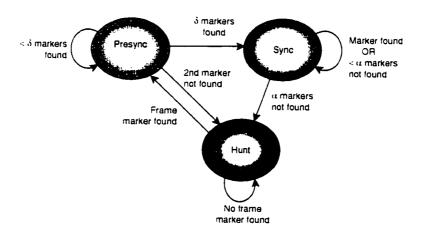

| Figure 3.4: Analysis state transition diagram of $\alpha\text{-}\delta$ framer                    | 22        |

| Figure 3.5: General confidence counter                                                            | 24        |

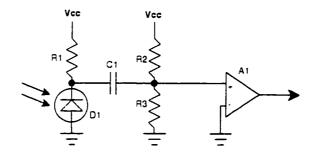

| Figure 4.1: AC coupled optical receiver                                                           | 29        |

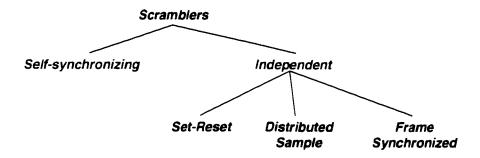

| Figure 4.2: Taxonomy of scramblers                                                                | 31        |

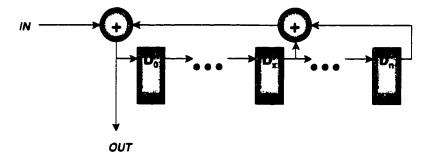

| Figure 4.3: Generic self-synchronizing scrambler                                                  | 31        |

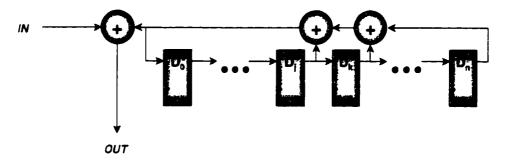

| Figure 4.4: Generic self-synchronizing unscrambler                                                | 32        |

| Figure 4.5: An independent scrambler                                                              | 36        |

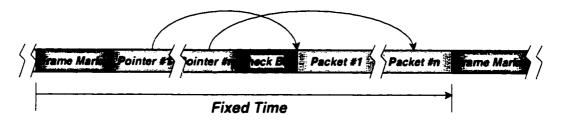

| Figure 5.1: Fixed frame with error corrected pointers                                             | 45        |

| Figure 5.2: Asynchronous frame marker with pointer                                                | 46        |

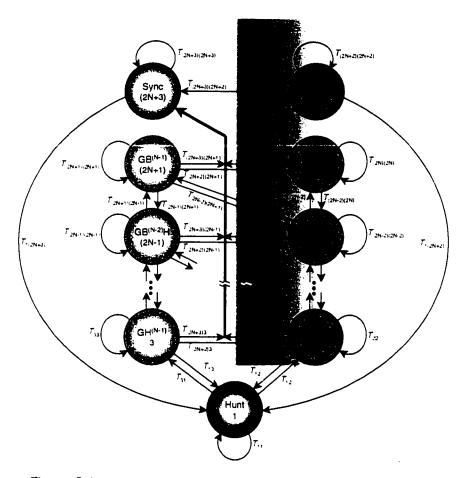

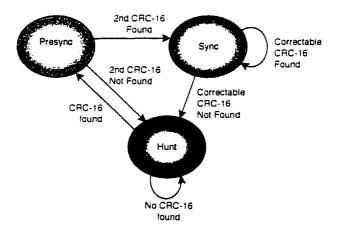

| Figure 5.3: Analysis state transition diagram of single SDL fra                                   | ımer 50   |

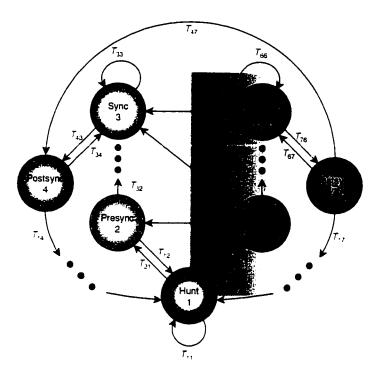

| Figure 5.4: Analysis state transition diagram of N parallel fran                                  | ners51    |

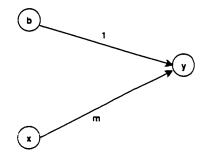

| Figure 5.5: Signal flow example of $y = mx + b \dots$                                             | 55        |

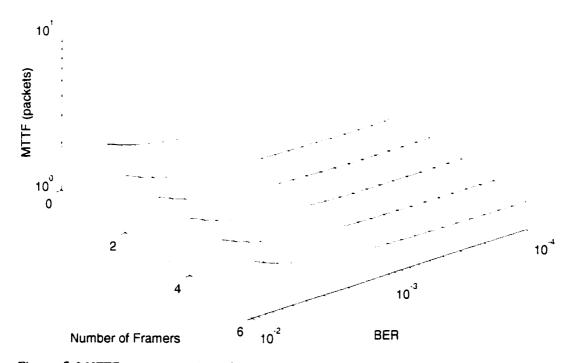

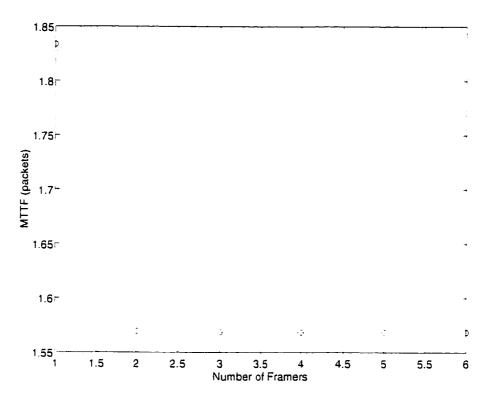

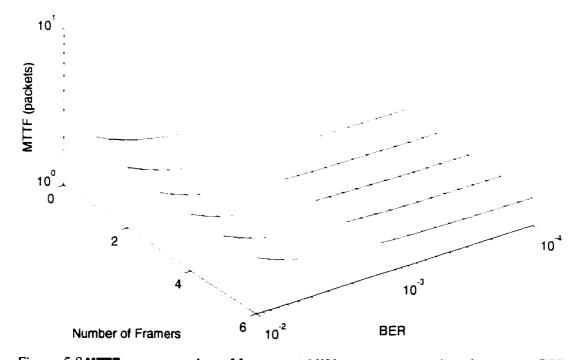

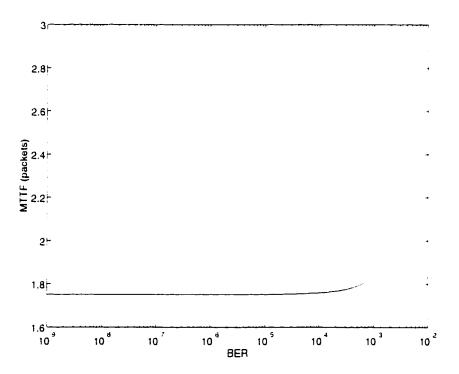

| Figure 5.6: MTTF versus number of framers at 356 byte averapacket size versus BER                 | age<br>59 |

| Figure 5.7: MTTF versus number of framers at 356 byte avera packet size at BER = 10 <sup>-3</sup> | age<br>60 |

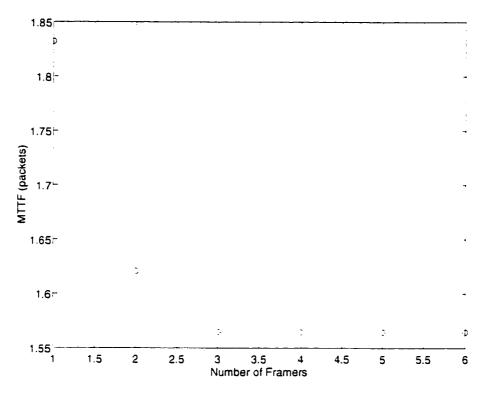

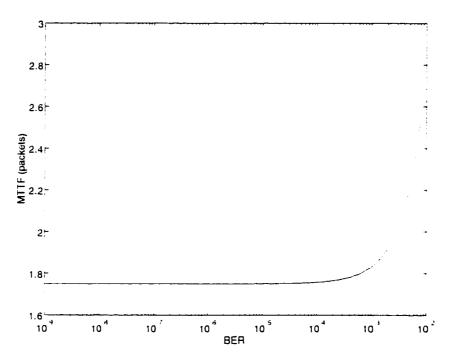

| Figure 5.8: MTTF versus number of framers at 64K byte averages packet size versus BER             | age<br>60 |

# List of Figures

| Figure |                                                                                              | Page |

|--------|----------------------------------------------------------------------------------------------|------|

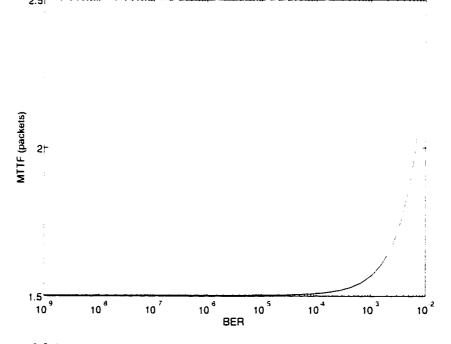

| Figure | 5.9: MTTF versus number of framers at 64K byte average packet size at BER = 10 <sup>-3</sup> | 61   |

| Figure | 5.10: Null fill header                                                                       | 63   |

| Figure | 5.11: Autocorrelation of DC balanced "Barker" sequence 0xB6AB31E0                            | 66   |

| Figure | 5.12: Scrambler state packet                                                                 | 70   |

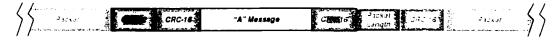

| Figure | 5.13: "A" and "B" messages                                                                   | 71   |

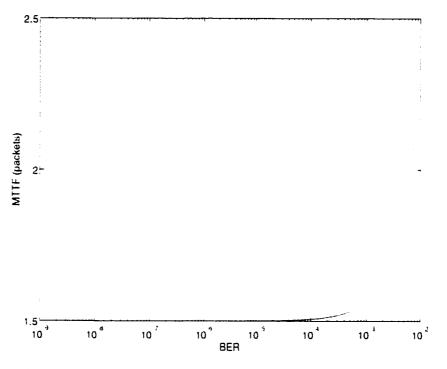

| Figure | 6.1: Single framer MTTF versus BER at 356 byte average packet length                         | . 74 |

| Figure | 6.2: Single framer MTTF versus BER at 64K byte average packet length                         | . 75 |

|        | 6.3: Quad framer MTTF versus BER at 356 byte average packet length                           | . 75 |

| Figure | 6.4: Quad framer MTTF versus BER at 64K byte average packet length                           | . 76 |

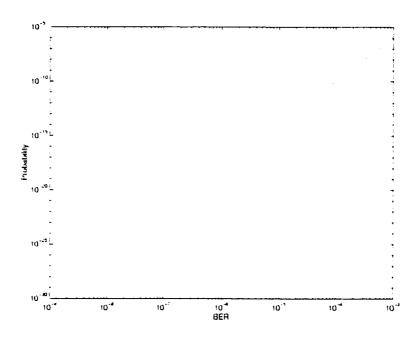

| Figure | 6.5: Probability of missing synchronization packet versus BER                                | . 77 |

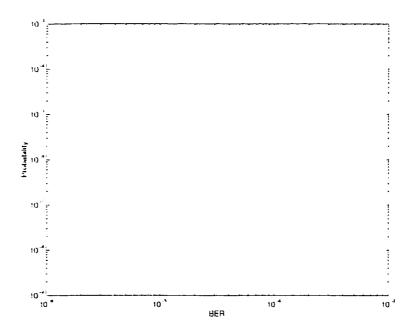

| Figure | 6.6: Probability of Loss of Frame versus BER for single bit correction                       | . 78 |

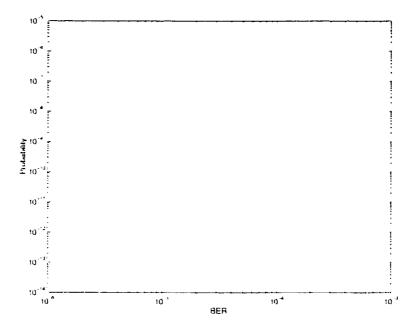

| Figure | 6.7: Probability of Loss of Frame versus BER for double bit correction                       | . 79 |

| Figure | 7.1: Operation for a single clock cycle update                                               | . 81 |

| Figure | 7.2: Transmit sequencing                                                                     | . 83 |

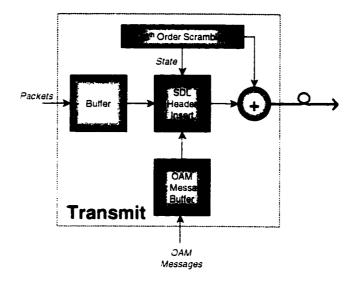

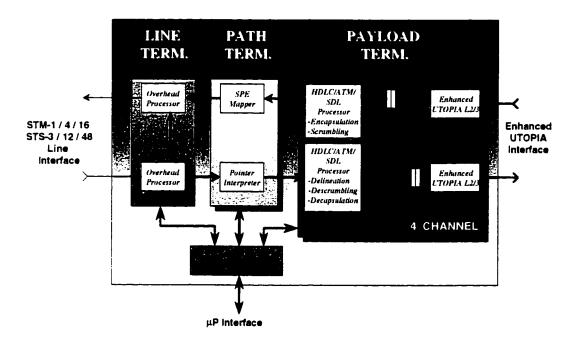

| Figure | 7.3: Framer Tx/Rx block diagram                                                              | . 84 |

| Figure | 7.4: SDL Frame Inserter Interfaces                                                           | . 86 |

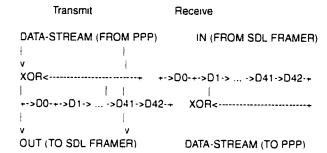

| Figure | 7.5: Functional implementation                                                               | . 92 |

| Figure | 7.6: Actual implementation                                                                   | . 92 |

| Figure | 7.7: SDL Framer Interfaces                                                                   | . 97 |

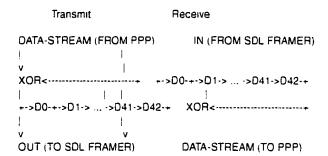

| Figure | 7.8: Functional implementation                                                               | 100  |

| Figure | 7.9: Actual implementation                                                                   | 100  |

| Figure | 8.1: TDAT042G5 die layout                                                                    | 106  |

# List of Figures

| Figure                                                                                     | Page  |

|--------------------------------------------------------------------------------------------|-------|

| Figure 8.2: Packaged TDAT042G5 and lower rate version                                      | . 107 |

| Figure 8.3: TDAT042G5 OC-48 test board                                                     | . 107 |

| Figure 8.4: TDAT042G5 OC-48 test set                                                       | . 108 |

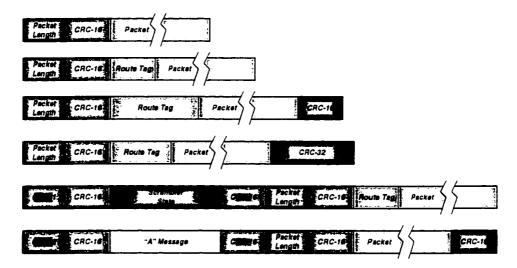

| Figure A.1: SDL packet examples                                                            | . 113 |

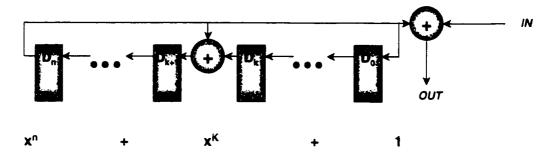

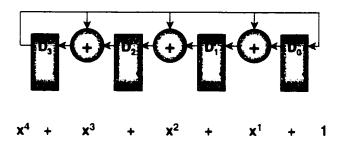

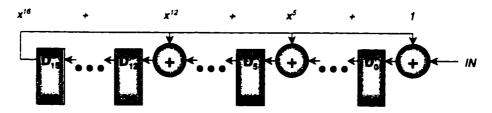

| Figure C.1: LFSR canonical form #1                                                         | . 130 |

| Figure C.2: LFSR canonical form #2                                                         | . 130 |

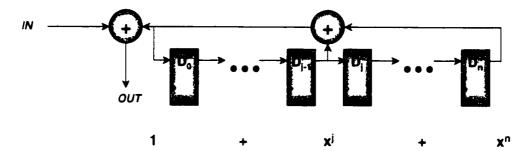

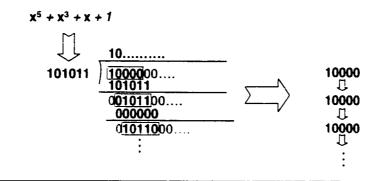

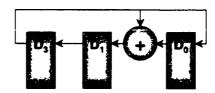

| Figure C.3: Binary division example                                                        | . 131 |

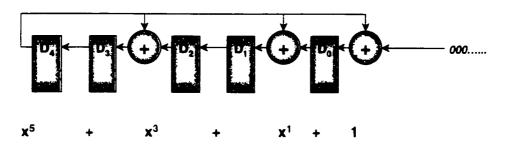

| Figure C.4: Canonical form #1 LFSR example                                                 | . 132 |

| Figure C.5: LFSR generator for vector representation of GF(8)                              | . 134 |

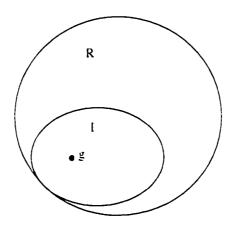

| Figure C.6: Illustration of ideal concept                                                  | . 139 |

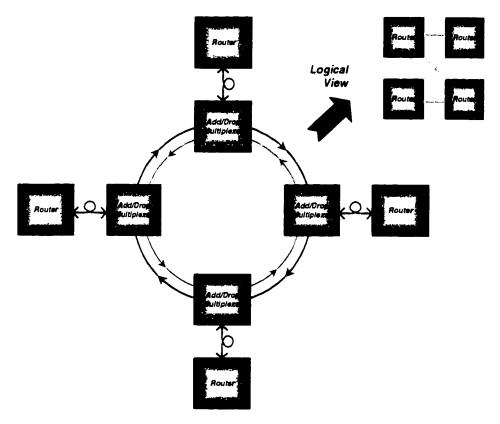

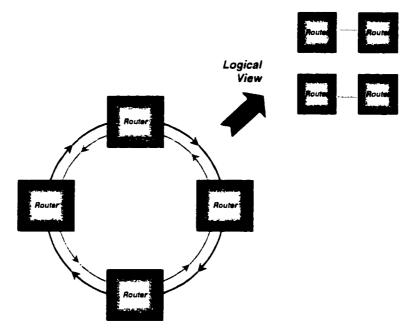

| Figure D.1: Ring based router network                                                      | . 143 |

| Figure D.2: "Big, fat pipe" network                                                        | . 144 |

| Figure D.3: STS-3 frame structure viewed as 3 stacked STS-1 frames at point of generation  | . 146 |

| Figure D.4: Average power spectral density of scrambler output during a long run of zeroes | . 150 |

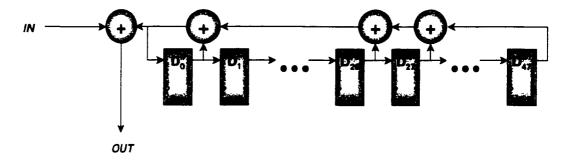

| Figure E.1: LFSR implementation of CRC16 division operation                                | . 151 |

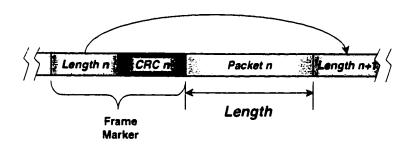

| Figure F.1: SDL frame boundary delineation                                                 | . 154 |

| Figure F.2: SDL header                                                                     | . 155 |

| Figure F.3: Fill header                                                                    | . 159 |

| Figure F.4: Special payload packet format                                                  | . 159 |

| Figure F.5: x <sup>48</sup> scrambler                                                      | . 161 |

| Figure F.6: SDL framing state machine                                                      | . 162 |

| Figure F.7: Scrambler state header and packet                                              | . 164 |

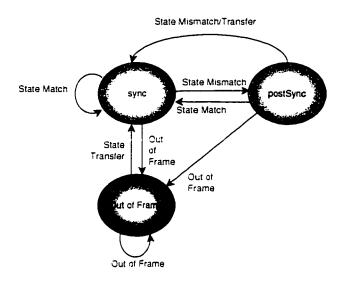

| Figure F.8: Scrambler synchronization state machine                                        | . 165 |

| Figure F.9: "A" Message header and packet                                                  | . 166 |

| Figure F.10: "B" Message header                                                            | . 166 |

# List of Tables

| <br>Table Pag                                                                               | E |

|---------------------------------------------------------------------------------------------|---|

| Table 2.1: Probability of occurrence of major packet modes 8                                |   |

| Table 2.2: Classical IP transport inefficiency (percent ATM payload not used for IP packet) |   |

| Table 5.1: Transport taxes associated with various formats72                                |   |

| Table 7.1: Transmit input signal interface                                                  |   |

| Table 7.2: Transmit output signal interface                                                 |   |

| Table 7.3: Pointer Interpreter signal interface                                             |   |

| Table 7.4: Sequencer transmit signal interface                                              |   |

| Table 7.5: Control signal interface                                                         |   |

| Table 7.6: Allowed header counts versus header type94                                       |   |

| Table 7.7: Receive input signal interface                                                   |   |

| Table 7.8: Receive output signal interface                                                  |   |

| Table 7.9: Control signal interface                                                         |   |

| Table 7.10: Allowed header counts versus header type102                                     |   |

| Table C.1: Addition table for GF(3)121                                                      |   |

| Table C.2: Multiplication table for GF(3)                                                   |   |

| Table C.3: Addition table for GF(2)122                                                      |   |

| Table C.4: Multiplication table for GF(2)                                                   |   |

| Table C.5: Multiplication table for GF(7)                                                   |   |

| Table C.6: Exponential Representation of GF(8)                                              |   |

| Table C.7: Exponential and vector Representation of GF(8) 127                               |   |

| Table C.8: Minimal polynomials for GF(8)                                                    |   |

| Table C.9: Binary (7,3) cyclic code words141                                                |   |

| Table D.1: Number of payload bytes per SONET frame type 146                                 |   |

| Table D.2: DC Balance attack probabilities for STS-3c payload 147                           |   |

| Table D.3: Transition attack probabilities for STS-3c payload 147                           |   |

| Table D.4: DC Balance attack probabilities for STS-12c payload 148                          |   |

| Table D.5: Transition attack probabilities for STS-12c payload 148                          |   |

# List of Tables

| Table                                                          | Page  |

|----------------------------------------------------------------|-------|

| Table D.6: DC Balance attack probabilities for STS-48c payload | . 148 |

| Table D.7: Transition attack probabilities for STS-48c payload | . 149 |

| Table F.1: Length offset values                                | . 156 |

# List of Symbols

| LIST OF SYTTIDOS    |                                                                                             |  |

|---------------------|---------------------------------------------------------------------------------------------|--|

| Symbol              | Definition                                                                                  |  |

| α                   | The number of events required to drop out of frame sync in an $\alpha-\delta$ framer.       |  |

| α                   | A primitive root of a Galois field polynomial.                                              |  |

| δ                   | The number of events required to acquire frame sync in an $\alpha-\delta$ framer.           |  |

| β                   | The probability of a logic one occurring in an incoming binary data stream.                 |  |

| $\partial, c(x)$    | A codeword.                                                                                 |  |

| $d_{min}$           | The minimum distance of a code.                                                             |  |

| ť                   | Normalized frequency.                                                                       |  |

| g(x)                | A generator polynomial for a Galois field code.                                             |  |

| i, j, k, m, n       | General counting variables                                                                  |  |

| मो                  | A message vector.                                                                           |  |

| ते                  | The current state of a transition matrix.                                                   |  |

| p                   | The probability of an event occurring.                                                      |  |

| $p_{nm}$            | The probability of transitioning from node $m$ to node $n$ in a state transition diagram.   |  |

| p(n, m)             | The probability of a random binary vector of length $n$ having $m$ or fewer zeroes or ones. |  |

| p(n, 2t)            | The probability of a random binary vector of length $n$ having $2t$ or fewer transitions.   |  |

| p(x)                | A Galois field primitive polynomial.                                                        |  |

| *                   | The remainder after Galois field division.                                                  |  |

| x                   | A finite field variable.                                                                    |  |

| В                   | A framer in a bad presync state.                                                            |  |

| $B_n$               | The n <sup>th</sup> Bernoulli number.                                                       |  |

| BER                 | Bit Error Rate.                                                                             |  |

| D                   | A delay operator equivalent to one unit time interval.                                      |  |

| $D_n$               | The n <sup>th</sup> flip-flop.                                                              |  |

| $\vec{\mathcal{D}}$ | A vector representing the state of all of the flip-flops in                                 |  |

# List of Symbols

| LIST OF SYTTIDOIS  |                                                                                                                                               |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol             | Definition                                                                                                                                    |  |

|                    | a circuit.                                                                                                                                    |  |

| D(n, m)            | The number of binary vectors of length $n$ having $m$ or fewer zeroes or ones.                                                                |  |

| F                  | A framer in the false frame state.                                                                                                            |  |

| G                  | A framer in a good presync state.                                                                                                             |  |

| $\vec{C}$          | A generator polynomial for a Galois field code.                                                                                               |  |

| $GF(q^m)$          | The Galois field constructed using $m$ -dimensional $q$ -ary vectors.                                                                         |  |

| Н                  | A framer in the hunt state.                                                                                                                   |  |

| 7                  | The identity matrix.                                                                                                                          |  |

| L                  | The number of ones in a period of a self-synchronizing scrambler's impulse response.                                                          |  |

| $L_n$              | The n <sup>th</sup> bit in the length field of an SDL header.                                                                                 |  |

| $L_{ m AVG}$       | The average number of bits in a packet.                                                                                                       |  |

| $L_{ m CRC}$       | The number of bits in a CRC                                                                                                                   |  |

| $L_F$              | The number of bits between frame patterns.                                                                                                    |  |

| $L_P$              | The number of bits in a frame pattern.                                                                                                        |  |

| $L_{ m Marker}$    | The number of bits in a frame marker.                                                                                                         |  |

| $L_{\mathrm{Max}}$ | The maximum number of bits in a packet.                                                                                                       |  |

| M(x)               | A minimal Galois field polynomial.                                                                                                            |  |

| P                  | The number of bits in a self-synchronizing scrambler's impulse response.                                                                      |  |

| $P_{XY}$           | The probability of a framer transitioning from frame state $Y$ to frame state $X$ , where the frame state may be any one of $H, B, G, F, S$ . |  |

| $P_{x}$            | The probability of event $x$ occurring.                                                                                                       |  |

| S                  | A framer in the sync state.                                                                                                                   |  |

| S(f)               | Power spectral density.                                                                                                                       |  |

| T                  | Normalized period.                                                                                                                            |  |

| $T_{nm}$           | The multiplicative weight associated with an edge                                                                                             |  |

# Symbol Definition between the start node m and the destination node n in a state transition diagram. T(n, t)The number of binary vectors of length n having t or fewer transitions when repeated ad infinitum. $\uparrow$ A transition matrix. $\uparrow$ A Galois field magic number.

### Glossary Term Definition AAL ATM Adaptation Layer - the logical layer responsible for SAR operations for ATM. **ACK** Acknowledgement - the most common is a 40 byte (20) TCP, 20 IP) packet used in the TCP protocol to ensure guaranteed delivery of TCP/IP datagrams whose bytes are sequence numbered. **ADM** Add Drop Multiplexer - a piece of SONET/SDH equipment designed to interface to a protected ring carrying multiple channels, some of which pass through, and others which are dropped. **ANSI** American National Standards Institute - a North American standards body, similar to ITU. **ATM** Asynchronous Transfer Mode - a packet switched format employing 53 byte packets called cells, which have 5 bytes of header information, and 48 bytes of payload. Backbone A term used to describe the SONET/SDH ring based telecommunications network running at speeds typically greater than or equal to 155 Mb/s. Bellcore Bell Communications Research - the industry standards consortium set up to provide network standards for North American telecommunications. Since the breakup of AT&T, its power is waning. BER Bit Error Rate. BIP Bit Interleaved Parity - a parity check typically used in transmission systems to detect payload corruption. **BIST** Built in self test - typically refers to a circuit associated with embedded memory structures in integrated circuits that performs testing on the memory at power-up. Call Setup A term typically associated with connection oriented protocols (such as ATM) used to describe the initiation

procedure involved in setting up the connection.

# Glossary

### Term

### Definition

### **Circuit Switched**

A term used to describe a (typically) constant bit rate digital connection that is similar to a "patch panel" connection. This is in contrast to a packet switched network.

Collision Based This refers to a physical layer protocol that uses a non-arbitrated, shared medium and can detect and deal with collisions due to simultaneous transmission.

### Connectionless Protocol

A term used to describe a communications protocol which does not have to maintain a constant connection between the source and destination (i.e. with keep-alives, etc.). An example is UDP.

### **Connection Oriented Protocol**

A term used to describe a communications protocol which maintains a constant connection between the source and destination (i.e. with keep-alives, etc.) An example is TCP.

CPE

Customer Premises Equipment - privately owned telecommunications equipment used to build LANs.

CRC

Cyclic Redundancy Check - a field appended (typically) to a message based on cyclic codes to provide a statistical guarantee of the message's correctness.

CSU/DSU

Customer Service Unit / Data Service Unit - a box (it used to be 2 boxes) that provides a data connection over a leased line using proprietary mappings into the payload of the leased line - i.e. T1, etc.

Datagram

A data message, that is typically transmitted as the payload in UDP or TCP.

DARPA

Defense Advance Research Projects Agency - a Department of Defense agency focused on funding advanced research projects of military interest.

**Ethernet**

collision-based, physical layer protocol for constructing LANs using either twisted pair (increasingly popular) or coaxial cable. Popular forms today are 10BaseT and 100BaseT which are 10 Mb/s and 100 Mb/s Ethernet over twisted pair, respectively.

# Glossary

| alossal y   |                                                                                                                                                                                                             |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Term        | Definition                                                                                                                                                                                                  |  |  |

| ETSI        | European Telecommunications Standards Institute - a European industry standards body similar to Bellcore.                                                                                                   |  |  |

| Frame Relay | A popular circuit switched data transport protocol used for packet networks and intended for ATM internetworking.                                                                                           |  |  |

| HDLC        | High-level Data Link Control - a simple framing method designed for packets.                                                                                                                                |  |  |

| HEC         | Header Error Check - the CRC used in the header of ATM cells.                                                                                                                                               |  |  |

| IETF        | Internet Engineering Task Force - the standards body that controls the standards for the Internet, IP, TCP, etc.                                                                                            |  |  |

| IP, IPv4    | Internet Protocol - a connection-less protocol used for packet delivery. See [5].                                                                                                                           |  |  |

| ITU         | International Telecommunications Union - the international standards body governing telecommunications standards for SDH countries.                                                                         |  |  |

| Keep-Alive  | A facet of a connection oriented protocol which maintains the link status with timers, etc.                                                                                                                 |  |  |

| LAN         | Local Area Network - a term used to describe a CPE network, as opposed to the WAN.                                                                                                                          |  |  |

| LFSR        | Linear Feedback Shift Register - a shift register used to implement the hardware equivalent of long division in a finite field.                                                                             |  |  |

| LSB         | Least Significant Bit.                                                                                                                                                                                      |  |  |

| MAC         | Media Access Control - the digital signalling layer associated with an Ethernet link.                                                                                                                       |  |  |

| MPOA        | Multiprotocol Over ATM - an encapsulation method used to transport protocols such as TCP over ATM.                                                                                                          |  |  |

| MPLS        | Multiprotocol Label Switching - also referred to as tag<br>switching (as pioneered by Cisco), this involves<br>attaching a tag to the packet for ease of routing<br>purposes (similar to a VCI/VPI in ATM). |  |  |

| MSB         | Most Significant Bit.                                                                                                                                                                                       |  |  |

| MTTF        | Mean Time To Frame.                                                                                                                                                                                         |  |  |

| MTTS        | Mean Time To Synchronization.                                                                                                                                                                               |  |  |

| Glossary       |                                                                                                                                                                                                                                          |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Term           | Definition                                                                                                                                                                                                                               |  |

| OAM&P          | Operation, Administration, Maintenance and Provisioning - this refers to the control scheme of a network.                                                                                                                                |  |

| OC-n           | Optical Carrier - n. The SONET line rate corresponding to n x 51.84 Mb/s.                                                                                                                                                                |  |

| Packet Switch  | hed                                                                                                                                                                                                                                      |  |

|                | A term used to describe a network which switches individual packets on the fly, based on the information contained within the packet.                                                                                                    |  |

| PDH            | Pleisiochronous Digital Hierarchy - the first set of digital carriers defined for the public data network. An example of this is a T1 connection.                                                                                        |  |

| PLF            | Probability of Loss of Frame.                                                                                                                                                                                                            |  |

| PFF            | Probability of False Frame.                                                                                                                                                                                                              |  |

| PFS            | Probability of False Synchronization.                                                                                                                                                                                                    |  |

| PPP            | Point-to-Point Protocol - an encapsulation method for datagrams that was designed to handle dial-up connections and identify the protocol of the encapsulated datagram. See [15].                                                        |  |

| PSTN           | Public Switched Telephony Network- the telecommunications network, sometimes referred to as the WAN.                                                                                                                                     |  |

| Quality of Ser | rvice                                                                                                                                                                                                                                    |  |

|                | A term used to describe the parameters associated with a connection with regards to delay, maximum burst size, etc It is important when trying to simultaneously switch real-time services (such as voice and video) with data services. |  |

| RFC            | Request for Comments - the final form of an IETF standard.                                                                                                                                                                               |  |

| SAR            | Segmentation and Reassembly.                                                                                                                                                                                                             |  |

| scan           | A test methodology for integrated circuits that involves connecting flip-flops together in a serial chain to allow values to be read and written, allowing the verification of the combinatorial logic within the integrated circuit.    |  |

| Glossary      |                                                                                                                                                                                                                                                                                                          |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Term          | Definition                                                                                                                                                                                                                                                                                               |  |  |

| SDH           | Synchronous Digital Hierarchy - the ITU version of SONET.                                                                                                                                                                                                                                                |  |  |

| SDL           | Simple Data Link - the link-layer protocol that this thesis discusses.                                                                                                                                                                                                                                   |  |  |

| SONET         | Synchronous Optical Network - a standard developed by Bellcore in the late 1980s to allow for the transport of high-speed, circuit-switched data via optics. Common rates are based on multiples of 51.84 Mb/s and include 155 Mb/s (OC-3), 622 Mb/s (OC-12), 2488 Mb/s (OC-48), and 9952 Mb/s (OC-192). |  |  |

| STS           | Synchronous Transport Stream - the 51.84 Mb/s (an STS-1) frame structure that forms the basis of SONET.                                                                                                                                                                                                  |  |  |

| T1            | A 1.544 Mb/s line which is one of the PDH rates.                                                                                                                                                                                                                                                         |  |  |

| TCP           | Transmission Control Protocol - the secure delivery mechanism for IPv4 packets. See [6].                                                                                                                                                                                                                 |  |  |

| TDM           | Time Division Multiplex - a multiplexing scheme using fixed time slots in a repeating fashion. An example of this is STS-1 channelization in SONET.                                                                                                                                                      |  |  |

| UDP           | User Datagram Protocol - another delivery mechanism for IPv4 packets, typically used for non-critical data. See [4].                                                                                                                                                                                     |  |  |

| UTOPIA        | Universal Test & Operations Interface for ATM - a popular physical layer interface for ATM cells. The Level 2 standard is the most common and is typically implemented as a 16 bit wide 50 MHz bus with handshake signals. The proposed Level 3 standard operates at 100 MHz with 32 bits.               |  |  |

| UTOPIA POS-PH | UTOPIA POS-PHY                                                                                                                                                                                                                                                                                           |  |  |

|               | A defacto standard extension of UTOPIA to handle packets other than 53 bytes in length. This involves partial packet transfer (typically 64 bytes) and some additional handshake flags.                                                                                                                  |  |  |

| VCI           | Virtual Circuit Identifier - a 16 bit field in an ATM cell header identifying the virtual circuit, which is a local connection identifier.                                                                                                                                                               |  |  |

# Term Definition VPI Virtual Path Identifier - an 8 or 16 bit field in an ATM cell header identifying the virtual path, which is a local connection identifier for a bundle of VCIs. VT Virtual Tributary - the sub-STS-1 rate frame structure used by SONET to transport PDH signals. The smallest increment is a VT1.5 which is roughly 1.5 Mb/s. WAN Wide Area Network - a datacom name for the PSTN. X.25 An old ITU packet transport standard.

Introduction 1-

### 1.1 Background and Objective<sup>†</sup>

Since data transmission statistics for the Internet have been tracked (~1969), data traffic volume has been roughly doubling[1] every year. It is estimated that in 1996 - 1997, voice and data traffic in the backbone reached parity in North America, with the rest of the world roughly 1 - 2 years behind[2]<sup>‡</sup>. This data is almost exclusively packet based[3], and according to current analysis is mainly TCP (transmission control protocol) or UDP (user datagram protocol) packets which implies IPv4 (internet protocol version 4) payloads[4][5][6].

Since the backbone is virtually all SONET/SDH (Synchronous Optical Network / Synchronous Digital Hierarchy)[7][8], the only officially sanctioned means of transporting packets within this network is to chop them up and transport them via ATM (asynchronous transfer mode) cells, which are then mapped into SONET/SDH using an approved mapping[9][11]\*. The issue with this is that if you are building a packet switched network, you are forced to build interfaces to the WAN (wide area network) that can talk ATM. While the argument is somewhat

For those not versed in telecom technology, the background to this thesis is that a new, "efficient" standard for transporting packets (packet over SONET) has been developed which has several serious flaws.

<sup>&</sup>lt;sup>‡</sup> This is in contrast to the voice traffic annual growth rate of 17%.

<sup>\*</sup> Note that ITU, Bellcore, ETSI, ANSI, and the ATM Forum all standardize various aspects of SONET/SDH, and all standards are slightly different.

religious in nature, the ATM signalling stack is quite involved, and there are not yet solid, clean mappings from packet network signalling into ATM signalling<sup>†</sup>. The result is that some amount of proprietary implementation is required.

Another argument against ATM is that there is a "cell tax" or overhead associated with mapping packets into cells. The obvious one is the extra 5 overhead bytes per 48 bytes of data in ATM, which equates to 9.4% wastage of bandwidth. More subtle is the fact that TCP uses small (i.e. 40 byte) ACK packets (packets containing only acknowledgement information) which expand to 56 bytes when encapsulated using MPOA (multiprotocol over ATM), thus effectively using 2 cells (106 bytes) to transport 40 bytes[10]-[14]. Depending on the ratio of ACK packets to datagrams, the average efficiency of the network may be quite low. For instance, if for every long datagram, an ACK packet is required, a 35.8% wastage would result (the average of 9.4% and 62.3%).

Consequently, a new standard (RFC1619) was developed to allow the direct mapping of packets into a SONET/SDH payload[15][16]. Unfortunately, this mapping has several flaws, including variable packet size expansion, and susceptibility of loss of packet from a single bit error. This will be discussed in detail later.

<sup>&</sup>lt;sup>7</sup> Especially in the quality of service and call setup area.

Finally, there is the issue of using SONET/SDH as the physical layer transport medium. It has very complex, proprietary signalling associated with it (especially in backbone ring applications), as well as a 4.4% overhead tax<sup>†</sup>.

This thesis addresses all of these issues and proposes a new framing protocol based on CRC-16 (16 bit cyclical redundancy check) packet boundary delineation that will allow robust. efficient mapping of packets into SONET/SDH or directly over fiber.

### 1.2 Thesis Organization

Chapter 2 of this thesis discusses packet transmission technology, from a framing perspective. Chapter 3 explores the different methods of providing frame boundary delineation while Chapter 4 explores the different methods of providing scrambling. In Chapter 5, the design of the new protocol is presented, and in Chapter 6 the performance of this protocol is analyzed. In Chapter 7 the implementation of this protocol in a 0.25 $\mu$  CMOS integrated circuit is discussed, while Chapter 8 presents the measurements of this framer in the lab. Finally Chapter 9 presents suggestions for future work in this field.

<sup>&</sup>lt;sup>†</sup> It should be noted that this signalling scheme is independent of the actual SONET/SDH transport mechanism, and SONET/SDH remains perhaps the most efficient means of transporting TDM traffic ever implemented.

### 1.3 Statement of Contribution

Unless otherwise stated, all of the material dealing with CRC based packet boundary delineation is the result of original work performed by the author over the period 1997 - 1999. Specifically the major contributions are:

- the development of a workable framing protocol from the initial concept of using length based frame delineation with CRC-10 tagging<sup>†</sup>[18].

- the development of the numerical techniques to analyze framing protocols for an arbitrary number of parallel framers.

- 3) the analysis of the framing protocol under various conditions.

- 4) the analysis of the flaws in the current POS (packet over SONET) standard.

- 5) the analysis of how to implement a bit-parallel distributed sample scramblers.

The significant secondary contributions are:

- the design and coding of the framing protocol as two blocks in an integrated circuit (the TDAT042G5).

- 2) the design of the bit-parallel implementation of the 48<sup>th</sup> order set-reset scrambler.

<sup>&</sup>lt;sup>†</sup> The original concept of combining the length of the packet with a CRC was invented in Bell-Labs and used a CRC-10. Unfortunately this scheme was unworkable due to many factors (discussed in Chapter 5).

- 3) The acceptance of SDL as a standard in the ITU in G.707[8], and within the IETF (Appendix J)<sup>†</sup>.

- 4) the design of the scrambler synchronization and "A" and "B" OAM&P (operations, administration, maintenance, & provisioning) messaging channels.

- 5) the discussion on the taxonomy of scramblers.

- 6) The application for a patent on the implementation of the ATM  $x^{31}$  algorithm.

- 7) The application for a patent on the multichannel transmit flow control structure of the data framer section.

<sup>&</sup>lt;sup>†</sup> It is anticipated that the SDL specification will become a standard in the IETF by the end of the year, as all that was required for full standardization was the granting of path signal labels (C2) for SDL by the ITU. This was done in the November ITU T1X1 meeting.

# **Packet Transmission Today**

2-

### 2.1 Introduction

As was mentioned in the introduction, there are two popular methods of transporting packets in today's network: packet over ATM over SONET/SDH over fiber, and packet over PPP (point-to-point protocol) over HDLC (high-level data link control) over SONET/SDH over fiber. In this chapter, both of these methods, as well as packet over ATM over fiber, are explored and the framing associated with them examined.

### 2.2 Packets

The Internet Protocol (IP) originated from work funded by DARPA in the 1970's to construct a reliable computing network for the US Department of Defense. Associated with IP are two additional protocols: TCP and UDP, with TCP being intended for reliable packet delivery, and UDP being intended for more rapid, less reliable, packet delivery (i.e. delay sensitive traffic, like voice). Today, IPv4 in its two principal flavors - TCP and UDP - constitutes the bulk of the data traffic on the Internet. This growth is being driven from the LAN computing environment which is today dominated by TCP/IP transported over Ethernet.

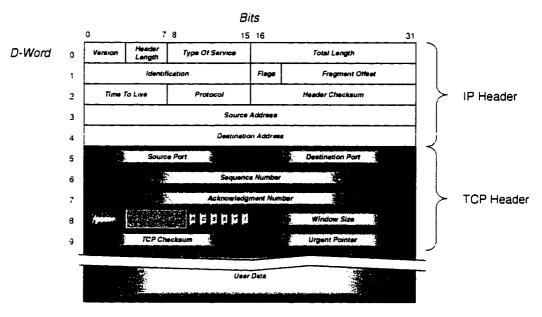

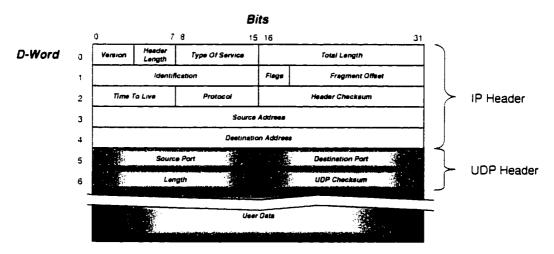

Figures 2.1 and 2.2 illustrate the headers for both TCP and UDP. As can be seen, the difference is in the information in the TCP and UDP fields. Since TCP is

Figure 2.1 TCP packet format with IPv4 header

Figure 2.2 UDP packet format with IPv4 header

intended for reliable communication, there is more information than is required to be conveyed. Every TCP/IP packet has a 32 bit sequence number, and a 32 bit acknowledgment number and together the two constitute the handshake for reliable packet delivery. A problem arises because in most Internet transfer models the connection is asymmetric (i.e. like web surfing), with the bulk of the information

flowing in one direction. The result is that a 40 byte TCP/IP acknowledgment packet containing no user data must be sent in the opposite direction on a 1:1 basis for every information bearing TCP/IP packet. As will be seen, this is significant.

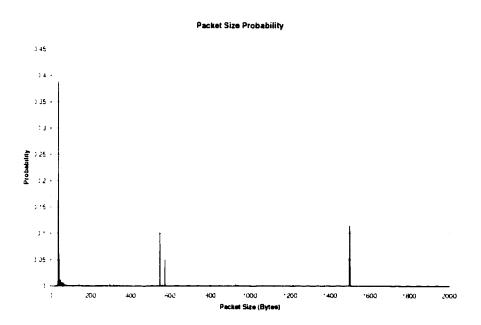

The following figure presents a summary of Internet packet sizes as collected by the

Figure 2.3 Internet packet size probability distribution

National Laboratory for Applied Network Research over a one minute interval on an OC-3 (155 Mb/s) link on MCI's backbone[19]. As can be seen, there are five major packet size modes. These are listed in Table 2.1.

| Major Packet Mode (bytes) | Probability |

|---------------------------|-------------|

| 40                        | 0.39        |

| 44                        | 0.06        |

| 552                       | 0.11        |

Table 2.1 Probability of occurrence of major packet modes

| Major Packet Mode (bytes) | Probability |

|---------------------------|-------------|

| 576                       | 0.05        |

| 1500                      | 0.12        |

Table 2.1 Probability of occurrence of major packet modes

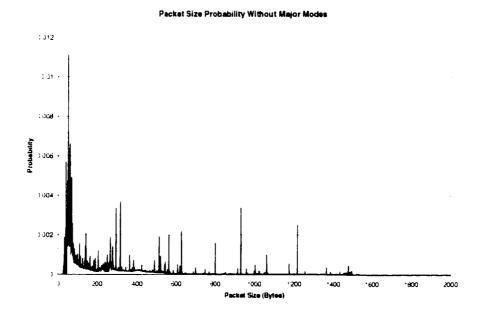

If these major modes are deleted from the histogram, the remaining packet size distribution can be observed in Figure 2.4. As can be seen, while there is a variety

Figure 2.4 Internet packet size distribution after major mode removal

of minor modes, the mass is pretty much distributed between 20 and 600 bytes in length. Interestingly, the largest packet seen is only 4352 bytes in length, despite the fact that the maximum allowable packet size is 65535 bytes<sup>†</sup>. Using the complete data set, the average packet size is 354 bytes, with a complete 39% of these packets

<sup>&</sup>lt;sup>†</sup> The major mode at 1500 bytes is due to this being the upper bound on Ethernet packet sizes.

being 40 byte TCP/IP ACK packets. This implies that a minimum of 78% of all packets on the Internet are TCP/IP based<sup>†</sup>.

### 2.3 The ATM "Cell Tax"

In order to transport data traffic, the public telephone companies (telcos) worked to develop a standard that could transport both voice, video, and data traffic simultaneously. This work was driven from the growth of private companies leasing lines to interconnect their networks. Originally this was done using special boxes called CSU/DSUs (customer service unit / data service unit), but since transporting data over a fixed rate leased line is inefficient there was an incentive for the telcos to build true data networks, and sell data connectivity directly to the businesses. Starting with X.25, this led to frame relay, and eventually ATM (asynchronous transfer mode), which was billed as the "final solution" for integrated networking. ATM promised to offer the ability to transport any type of service simultaneously by employing quality of service guarantees. Unfortunately, while this is now finally true, these promises were made 8 years ago, and it has taken this long for the standards and technology to make this a reality.

<sup>&</sup>lt;sup>†</sup> Dropped packets, larger frame sizes (the number of packets per ACK) will cause this number to grow

<sup>&</sup>lt;sup>‡</sup> This arises from the fact that while the peak bit rate in data traffic is usually as large as the channel will permit, and average bit rate is usually quite small. This allows for the possibility of statistical multiplexing, where many data channels share the same peak bandwidth, and collisions are soaked up in buffers.

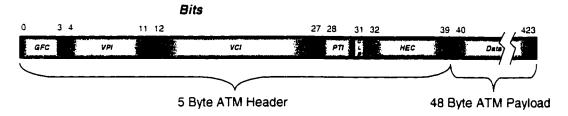

Figure 2.5 shows the structure of an ATM cell. It consists of a 5 byte header and a

Figure 2.5 ATM cell structure

48 byte payload. What is special about it is that the header contains an 8-bit CRC (or HEC - header error check) which provides both the ability to provide a guarantee of the correctness of the bits in the header, and the ability to provide physical layer framing (see Section 3.3). The basic concept is that the ATM cell is like a 48 byte container with dynamic, circuit based routing information contained in the header. Anything to be transported by ATM is cut up into 48 byte chunks and placed into ATM cells, with the start of packet signalled in the header PTI (payload type indicator) field. The process associated with this is referred to as segmentation and reassembly, or SARing. Like all aspects of ATM, there are standards governing how various forms of data can be mapped into ATM using an ATM Adaptation Layer (AAL)[12]. For non-delay sensitive data such as IP packets, AAL-5 is used. Figure

Figure 2.6 RFC1483 AAL-5 Classical IP Mapping

2.6 shows the structure of the classical mapping for IP packets into ATM cells, using RFC1483[13]. In this mapping the header is used to identify the payload, and the trailer is used for integrity checking (i.e. it contains a CRC-32 and the length of the payload). Since this entire message is cut up into 48 byte chunks to fit into the payload of ATM cells, a pad field is needed to take up the slack for messages that are not an even multiple of 48 bytes. Unfortunately, as shown in Table 2.1, this happens to be extremely inefficient for 40 and 44 byte datagrams which require two ATM cells to transfer the message. The inefficiencies inherent in classical IP mapping for the major packet modes are given below in Table 2.2. The inefficiency

| Major Packet Mode (bytes) | Probability | Classical IP mapping inefficiency |

|---------------------------|-------------|-----------------------------------|

| 40                        | 0.39        | 0.58                              |

| 44                        | 0.06        | 0.54                              |

| 552                       | 0.11        | 0.04                              |

| 576                       | 0.05        | 0.08                              |

| 1500                      | 0.12        | 0.02                              |

Table 2.2 Classical IP transport inefficiency (percent ATM payload not used for IP packet)

(or "tax") was calculated by determining the fraction of the ATM payload actually carrying the IP packet. When this calculation is extended over all of the packets in the distribution in Table 2.3. the average inefficiency imposed by classical IP mapping (ignoring ATM header overhead) is found to be 34% (i.e. 34% of all AAL-5 mapped payload is used for purposes other than transporting the IP packet). If we now consider the SONET/SDH (4 bytes in 90), ATM (5 bytes in 53), and

AAL-5 overhead, the total tax incurred by transporting IP packets using the classical IP mapping in ATM is 43%. Clearly this is an issue[18].

# 2.4 Packet over SONET/SDH (POS)

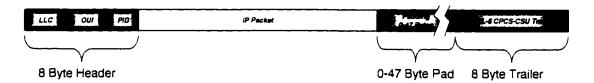

In order to combat this inefficiency, and to avoid having to utilize ATM in a packet based network, the POS standard was proposed[15][16]. This standard dispenses with ATM cells and the AAL-5 layer, and instead uses a PPP (point-to-point protocol) wrapper and directly maps the packets into the SONET/SDH payload<sup>†</sup>. This format is shown in Figure 2.7. The PPP (the same PPP used in dial-up

Figure 2.7 RFC1662 PPP encapsulation

connections) is used to identify the payload type that is being transported. When the standard was written, there was a 2 byte address and control field reserved in the header. Unfortunately, no one ever figured out what to do with these fields (which default to 0xFF03). As a result, these bytes are often not transmitted<sup>‡</sup>. For payload integrity, a CRC-16 or CRC-32 is applied. This CRC field size is negotiated on connection set-up, or is provisioned.

<sup>&</sup>lt;sup>†</sup> When people refer to packet over fiber, it is POS that they are usually referring to, which is packet over SONET over fiber.

<sup>&</sup>lt;sup>‡</sup> This is referred to as a "compressed header".

In order to delineate the packet boundaries, byte escaping is used (versus bit-escaping used on DS-3 (~45 Mb/s) and lower rate connections<sup>†</sup>). The basic concept is that the spaces between packets shall be filled with one or more 0x7E bytes (the HDLC flag). To make this work, all of the natural occurrences of 0x7E within the packet must be changed to something else. In this case, they are replaced with the two byte 0x7D5E combination, with the 0x7D byte indicating that the next byte has been "escaped". All of the naturally occurring 0x7D bytes within the packet must also be escaped. In this case they are replaced with the two byte combination 0x7D5D.

The implication is that the packet will grow in size by an amount proportional to the percentage of 0x7E and 0x7D characters that occur within the packet. If we assume a uniform distribution over all possible bytes, this will cause an average transport tax of roughly 1% (2 bytes in 258). Adding the PPP header we arrive at the final PPP transport taxes of: 6%, 8%, and 10% for 4, 6, and 8 byte PPP overheads. Taking the SONET/SDH overhead inefficiency into account we achieve transport taxes of 10%, 12%, and 14% respectively.

This is far superior to the efficiency of the classical IP mapping into ATM over SONET, and is the reason that so much publicity is surrounding POS (packet over

The reasoning for this is that bit-escaping uses the rule "insert an extra zero after 5 ones in a row". This introduces run length dependencies into the escaping process making it more difficult to pipeline and run in parallel at high speeds, versus byte escaping which only depends on the current byte.

SONET) today. Unfortunately, there are several deficiencies associated with this standard, which became the basis for the work of this thesis. They are:

- A single bit error in an HDLC flag can cause the loss of an entire packet. This

defeats any ability to add error correction at the packet level.