INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the

text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the copy

submitted. Broken or indistinct print, colored or poor quality illustrations and

photographs, print bleedthrough, substandard margins, and improper alignment

can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and

there are missing pages, these will be noted. Also, if unauthorized copyright

material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning

the original, beginning at the upper left-hand comer and continuing from left to

right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white photographic

prints are available for any photographs or illustrations appearing in this copy for

an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

## Computational RAM: A Memory-SIMD Hybrid

by

Duncan George Elliott

A thesis submitted in conformity with the requirements

for the Degree of Doctor of Philosophy,

Graduate Department of Electrical and Computer Engineering

University of Toronto

© 1998 by Duncan George Elliott

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérance

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-41424-8

### **Abstract**

#### Computational RAM: A Memory-SIMD Hybrid

Doctor of Philosophy dissertation, 1998

Duncan George Elliott

Department of Electrical and Computer Engineering

University of Toronto

In this thesis, a novel computer architecture called Computational RAM (CoRAM) is proposed and implemented. CoRAM is semiconductor random access memory with processors incorporated into the design, while retaining a memory interface. CoRAM can be used to build an inexpensive massively-parallel computer. Applications that contain the appropriate parallelism will typically run thousands of times faster on CoRAM than on the CPU. This work includes the design and implementation of the architecture as a working chip with 64 processor elements (PEs), a PE design for a 2048-PE 4 Mbit DRAM, and applications.

CoRAM is the first processor-in-memory architecture that is scalable across many generations of DRAM. This scalability is obtained by pitch-matching narrow 1-bit PEs to the memory and restricting communications to using 1-dimensional interconnects. The PEs are pitch-matched to memory columns so that they can be connected to the sense amplifiers. The 1-bit wide datapath is suitable for a narrow, arrayable VLSI implementation, is compatible with memory redundancy, and has the highest performance/cost ratio among hardware arithmetic algorithms. For scalability, the memory arrays and memory-style packaging limit the internal interprocessor communications to 1-dimensional networks. Of these networks, both a broadcast bus network and a left-right nearest-neighbour network are implemented.

Corrections Corrections that the CPU. By placing SIMD PEs adjacent to those sense amplifiers, this internal memory bandwidth can be better utilized.

The performance of C•RAM has been demonstrated in a wide range of application areas, and speed-ups of several orders of magnitude compared to a typical workstation have been shown in the fields of signal and image processing, database, and CAD.

## Acknowledgments

I am grateful for the support from and technical exchange with MOSAID Technologies and IBM Microelectronics; IC fabrication provided by Northern Telecom through the Canadian Microelectronics Corporation; and support from the Natural Sciences and Engineering Research Council of Canada, Micronet, and the University of Toronto.

Professor David Wheeler of the Computer Laboratory, University of Cambridge introduced me to the idea of putting the computing in the memory chips. My supervisors, Professors Michael Stumm and Martin Snelgrove kept me on track without a single change of topic. Michael Stumm put in more than a reasonable effort in encouraging me and organizing my work. Martin Snelgrove was instrumental in making connections to potential industrial partners and taught me valuable business lessons. I have learned lessons on DRAMs that no textbook could tell from Peter Gillingham, Graham Allan, Randy Torrance, Dick Foss, Iain Scott, David Frank, Howard Kalter, and John Barth. My lab-mates and members of the semiconductor design staff at MOSAID improved the quality and the enjoyment of my learning. Oswin Hall provided the first user feedback on CoRAM and proposed the PE shift register circuit. For strengthening this work by offering their questions and suggestions I also thank: Christian Cojocaru, Dickson Tak Shun Cheung, David Galloway, Robert McKenzie, Wayne Loucks, Tet Yeap, Martin Lefebvre, Jean-Francois Rivest, Sethurman Panchanathan, Wojciech Ziarko, Thinh Le, Glenn Gulak, David Wortman, Graham Jullien, Safwat Zaky, and Zvonko Vranesic.

This dissertation would not have seen the light of day without encouragement from my whole family. I would especially like to thank my wife, Janet Elliott, who was a constant source of enthusiasm, had streams of writing suggestions, and in the end sat me down to write this document.

## **Contents**

| 1 | Intro | duction  | n                                       | 1    |

|---|-------|----------|-----------------------------------------|------|

|   | 1.1   | Disser   | rtation Organization                    | . :  |

| 2 | Prior | Art      |                                         | 7    |

|   | 2.1   | Massiv   | vely Parallel SIMD Processors           | . 7  |

|   | 2.2   | Memo     | ories                                   | . 20 |

|   |       | 2.2.1    | DRAM Circuits                           | . 22 |

|   |       | 2.2.2    | DRAM Chip Interfaces                    | . 24 |

|   |       | 2.2.3    | DRAM IC Process                         | . 25 |

|   |       | 2.2.4    | Redundancy                              | . 27 |

|   |       | 2.2.5    | Smart Memories                          | . 28 |

|   | 2.3   | Summa    | nary                                    | . 29 |

| 3 | Com   | puting i | in the Memory: the Abstraction          | 30   |

|   | 3.1   | Memor    | ry Bandwidth                            | . 31 |

|   | 3.2   | Mainta   | aining Compatibility with Memory        | . 34 |

|   |       | 3.2.1    | Using DRAM IC Processes                 | . 34 |

|   |       | 3.2.2    | Physical Dimensions and Performance     | . 34 |

|   |       | 3.2.3    | Coping with Long Wordlines              | . 35 |

|   |       | 3.2.4    | Redundancy Considerations               | . 36 |

|   |       | 3.2.5    | Packaging Considerations                | . 38 |

|   | 3.3   | Additio  | onal Design Issues                      | . 39 |

|   |       | 3.3.1    | Asymptotic Advantages of Bit-Serial PEs | . 39 |

|   |       | 3.3.2    | PE Aspect Ratio                         | . 42 |

|   | 3.4   | Basic (  | CoRAM Architecture                      | 45   |

|   | 3.5          | Advan                                                                                              | ntages of CoRAM Architecture                                                                                                                                          | <br>46                                                       |

|---|--------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|   |              | 3.5.1                                                                                              | System Cost                                                                                                                                                           | <br>46                                                       |

|   |              | 3.5.2                                                                                              | Performance                                                                                                                                                           | <br>47                                                       |

|   |              | 3.5.3                                                                                              | Scalability                                                                                                                                                           | <br>47                                                       |

|   |              | 3.5.4                                                                                              | Power Consumption                                                                                                                                                     | <br>49                                                       |

|   | 3.6          | Design                                                                                             | n Space Alternatives                                                                                                                                                  | <br>49                                                       |

|   | 3.7          | Summa                                                                                              | nary                                                                                                                                                                  | <br>50                                                       |

| 1 | A wob        | itaatura                                                                                           | al Details                                                                                                                                                            | 52                                                           |

| • |              |                                                                                                    |                                                                                                                                                                       |                                                              |

|   | 4.1          | Proces                                                                                             | ssing Element                                                                                                                                                         |                                                              |

|   |              | 4.1.1                                                                                              | ALU Design                                                                                                                                                            | <br>53                                                       |

|   |              | 4.1.2                                                                                              | Conditional Operations                                                                                                                                                | <br>58                                                       |

|   | 4.2          | Interco                                                                                            | onnection Network                                                                                                                                                     | <br>59                                                       |

|   |              | 4.2.1                                                                                              | Suitability of Interconnection Networks                                                                                                                               | <br>60                                                       |

|   | 4.3          | System                                                                                             | n IO                                                                                                                                                                  | <br>67                                                       |

|   | 4.4          | Summa                                                                                              | nary                                                                                                                                                                  | <br>67                                                       |

|   |              |                                                                                                    |                                                                                                                                                                       |                                                              |

| 5 | Impl         | amantai                                                                                            | ition                                                                                                                                                                 |                                                              |

| 5 | •            | ementa                                                                                             |                                                                                                                                                                       | 69                                                           |

| 5 | Imple<br>5.1 | Prototy                                                                                            | ype                                                                                                                                                                   | <br><b>69</b>                                                |

| 5 | •            |                                                                                                    | ype                                                                                                                                                                   | <br><b>69</b><br>69<br>70                                    |

| 5 | •            | Prototy                                                                                            | ype                                                                                                                                                                   | <br><b>69</b><br>69<br>70                                    |

| 5 | •            | Prototy<br>5.1.1                                                                                   | ype                                                                                                                                                                   | <br><b>69</b><br>69<br>70<br>74                              |

| 5 | •            | Prototy<br>5.1.1<br>5.1.2                                                                          | ype                                                                                                                                                                   | <br><b>69</b><br>69<br>70<br>74                              |

| 5 | 5.1          | Prototy<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                        | ype          Memory          Processor Element          Testing and Performance                                                                                       | <br>69<br>70<br>74<br>81                                     |

| 5 | 5.1          | Prototy<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                        | ype                                                                                                                                                                   | <br>69<br>70<br>74<br>81                                     |

| 5 | 5.1          | Prototy<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>High D                                              | ype                                                                                                                                                                   | <br>69<br>70<br>74<br>81<br>81<br>82                         |

| 5 | 5.1          | Prototy<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>High D<br>5.2.1                                     | Memory  Processor Element  Testing and Performance  Summary  Density Design  Reference DRAM Architecture                                                              | <br>69<br>70<br>74<br>81<br>81<br>82<br>83                   |

| 5 | 5.1          | Prototy<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>High D<br>5.2.1<br>5.2.2                            | Memory  Processor Element  Testing and Performance  Summary  Density Design  Reference DRAM Architecture  C•RAM Memory                                                | <br>69<br>70<br>74<br>81<br>81<br>82<br>83                   |

| 5 | 5.1          | Prototy<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>High D<br>5.2.1<br>5.2.2<br>5.2.3                   | Memory  Processor Element  Testing and Performance  Summary  Density Design  Reference DRAM Architecture  C•RAM Memory  PE-Memory Interface                           | <br>69<br>70<br>74<br>81<br>81<br>82<br>83<br>83             |

| 5 | 5.1          | Prototy<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>High D<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4          | Memory  Processor Element  Testing and Performance  Summary  Density Design  Reference DRAM Architecture  C•RAM Memory  PE-Memory Interface  Processor Element        | <br>69<br>70<br>74<br>81<br>81<br>82<br>83<br>83<br>84<br>85 |

| 5 | 5.1          | Prototy<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>High D<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5 | Memory  Processor Element  Testing and Performance  Summary  Density Design  Reference DRAM Architecture  C•RAM Memory  PE-Memory Interface  Processor Element  Power | <br>69<br>70<br>74<br>81<br>82<br>83<br>83<br>84<br>85<br>88 |

| 6 | Appl        | ications                                    | 95  |

|---|-------------|---------------------------------------------|-----|

|   | 6.1         | Programming Model                           | 95  |

|   | 6.2         | Experimental Method                         | 96  |

|   | 6.3         | Signal Processing and Graphics Applications | 98  |

|   |             | 6.3.1 Convolution                           | 99  |

|   |             | 6.3.2 Vector Quantization Image Compression | 100 |

|   | 6.4         | Database Applications                       | 102 |

|   |             | 6.4.1 Least Squares Match                   | 102 |

|   |             | 6.4.2 Data Mining                           | 103 |

|   | 6.5         | Computer Aided Design Applications          | 106 |

|   |             | 6.5.1 Fault Simulation with Multiple Faults | 106 |

|   | 6.6         | Exhaustive Solution-Space Search            | 108 |

|   |             | 6.6.1 Satisfiability Problem                | 108 |

|   | 6.7         | Memory Operations                           | 110 |

|   |             | 6.7.1 Clearing Memory to Zero               | 110 |

|   | 6.8         | Summary                                     | 110 |

| 7 | Conc        | lusions                                     | 112 |

|   | 7.1         | Future Work                                 | 113 |

| A | Carr        | ying On                                     | 114 |

|   | A.1         | Technology Transfer to Industry             | 114 |

|   | A.2         | Carrying On in Academia                     | 114 |

| В | Impl        | ementation of Common C•RAM Operations       | 116 |

|   | B.1         | Memory Copy                                 | 117 |

|   | B.2         | Addition                                    | 118 |

|   | B.3         | If-else                                     | 119 |

|   | B.4         | Multiplication                              | 119 |

|   | B.5         | Find Minimum Element                        | 120 |

|   | B.6         | Two-dimensional communication               | 121 |

|   | <b>B</b> .7 | Summary                                     | 123 |

| C Opti  | C Optimal Data Placement for Two-Dimensional Grid Problems |     |  |  |  |  |  |  |

|---------|------------------------------------------------------------|-----|--|--|--|--|--|--|

| C.1     | Left-Right Communication                                   | 124 |  |  |  |  |  |  |

| C.2     | Scalable Left-Right Interconnect                           | 125 |  |  |  |  |  |  |

| D Gloss | sary                                                       | 127 |  |  |  |  |  |  |

# **List of Figures**

| 1.1  | Memory cell array incorporating PEs                          | 2  |

|------|--------------------------------------------------------------|----|

| 2.1  | X-Net interprocessor communication network                   | 14 |

| 2.2  | Generic DRAM cell array                                      | 21 |

| 2.3  | DRAM memory cell                                             | 21 |

| 2.4  | DRAM memory column                                           | 23 |

| 3.1  | Conventional workstation architecture                        | 31 |

| 3.2  | Memory bandwidth throughout system                           | 32 |

| 3.3  | Redundant memory columns and PEs                             | 36 |

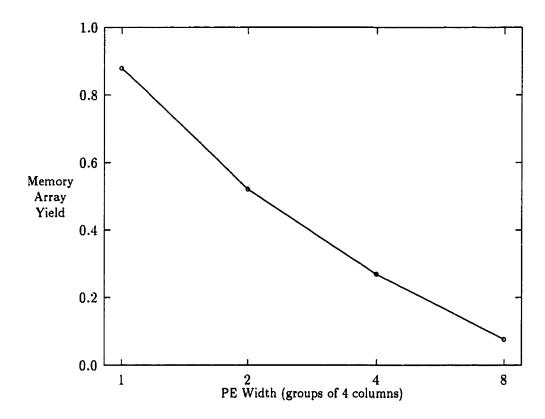

| 3.4  | Yield as a function of PE width                              | 37 |

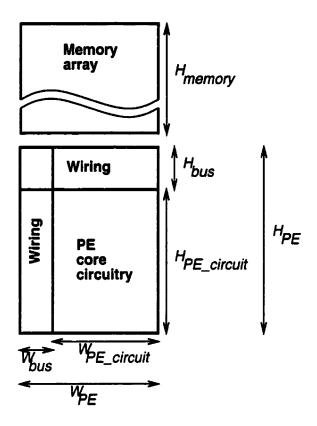

| 3.5  | PE dimensions                                                | 43 |

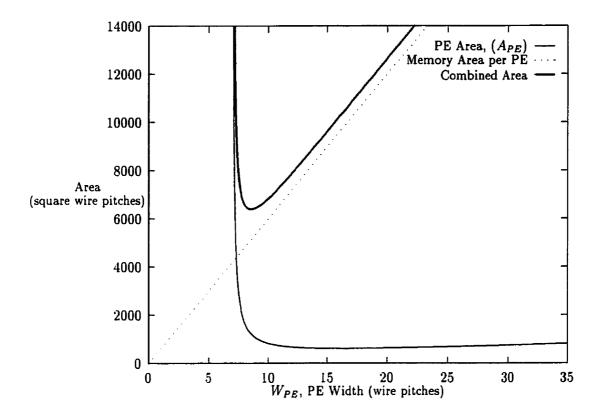

| 3.6  | The effect of PE pitch on chip area per PE                   | 44 |

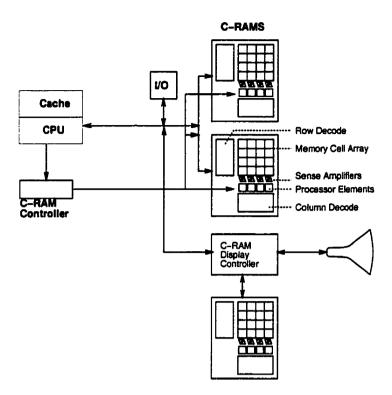

| 3.7  | C•RAM computer architecture                                  | 46 |

| 4.1  | Generic single data register C•RAM PE                        | 54 |

| 4.2  | Arithmetic performance vs. PE area                           | 55 |

| 4.3  | Minimalist NAND processor element                            | 55 |

| 4.4  | 256 Function processor element                               | 57 |

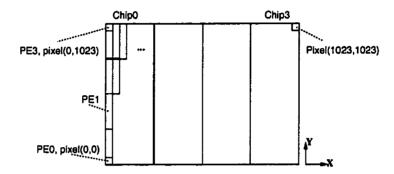

| 4.5  | Shift register interconnection                               | 62 |

| 4.6  | The mapping of pixels to PEs                                 | 62 |

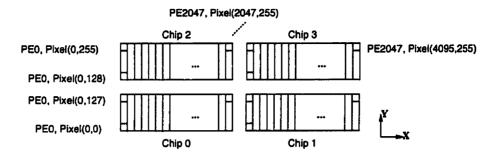

| 4.7  | The mapping of pixels to PEs for scalable interconnection    | 63 |

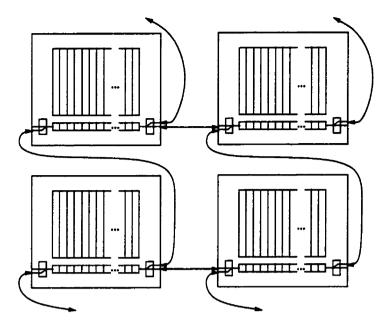

| 4.8  | Scalable left-right (4-pin) interconnection                  | 64 |

| 4.9  | Scalable left-right interconnection with increased bandwidth | 65 |

| 4 10 | 256. Function processor element including interconnection    | 66 |

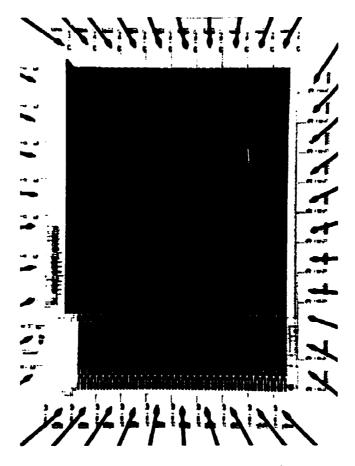

| 5.1  | 64 processor prototype C•RAM die photo                  | 70 |

|------|---------------------------------------------------------|----|

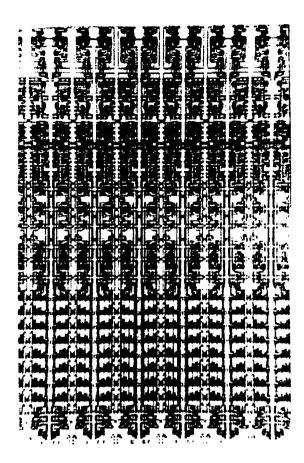

| 5.2  | Detail of 12 C•RAM PEs                                  | 71 |

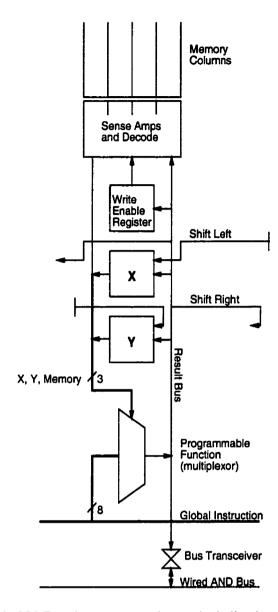

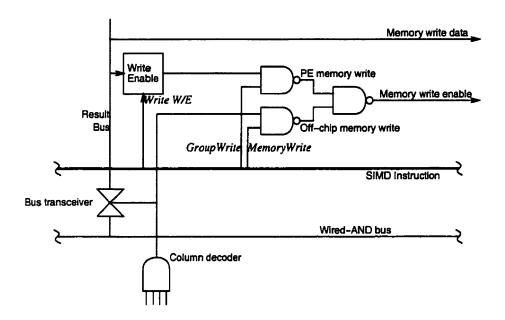

| 5.3  | Prototype processor element architecture                | 72 |

| 5.4  | Detail of write-enable and bus-transceiver control      | 73 |

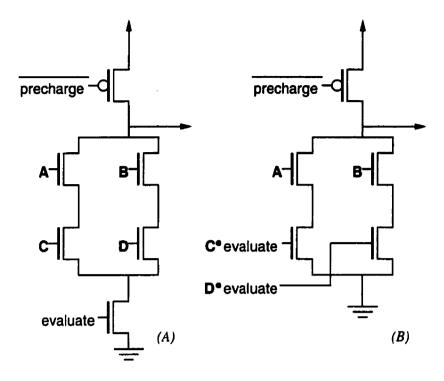

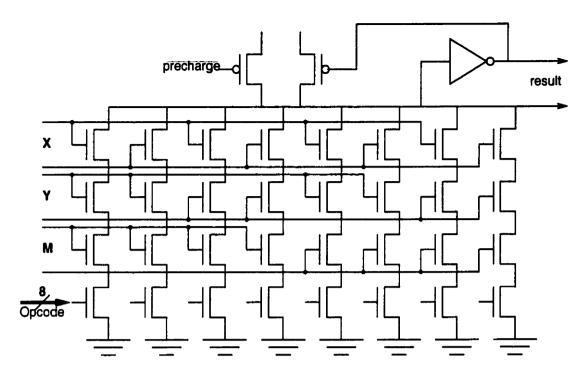

| 5.5  | (A) Classic dynamic logic, (B) Evaluate signal combined | 77 |

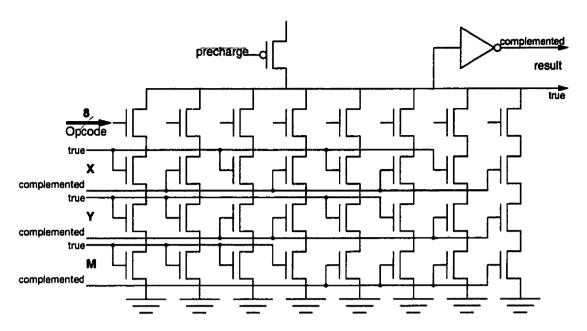

| 5.6  | Dynamic logic 8-to-1 multiplexor                        | 78 |

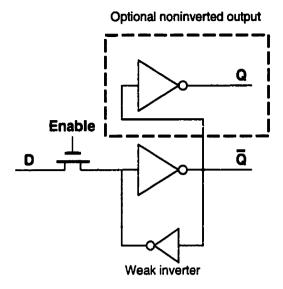

| 5.7  | PE register                                             | 79 |

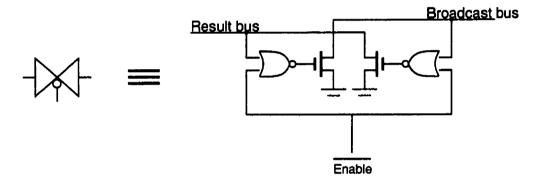

| 5.8  | Simultaneous bi-directional bus transceiver             | 79 |

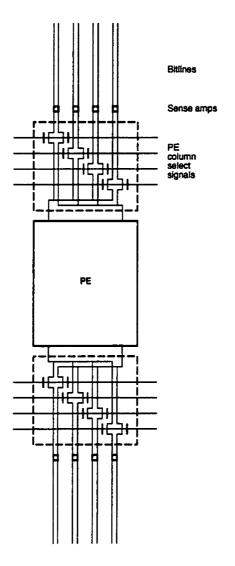

| 5.9  | PE column decode multiplexor                            | 85 |

| 5.10 | Dynamic logic 8-to-1 multiplexor                        | 86 |

| 5.11 | PE register with second input                           | 87 |

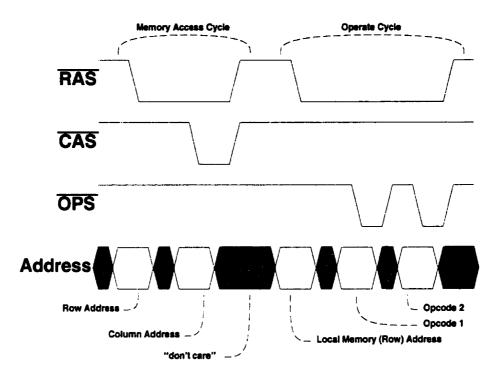

| 5.12 | Timing of a memory access followed by an operate cycle  | 90 |

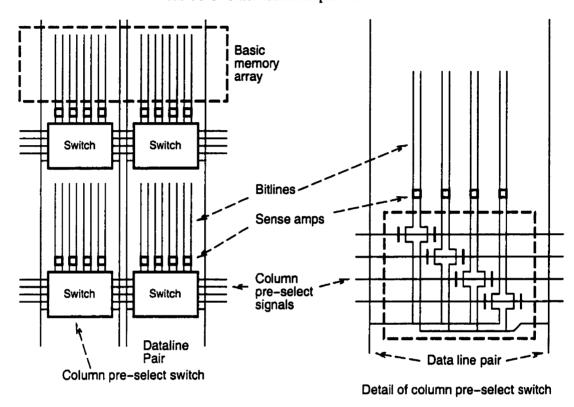

| 5.13 | Memory with bitline direction datalines                 | 92 |

## **List of Tables**

| 2.1 | Characteristics of massively parallel processors | 8  |

|-----|--------------------------------------------------|----|

| 3.1 | ALU algorithm and complexity                     | 40 |

| 5.1 | C•RAM SIMD instruction bits                      | 91 |

| 5.2 | Other additional pins for C•RAM                  | 92 |

| 6.1 | Performance summary                              | 98 |

## Chapter 1

## Introduction

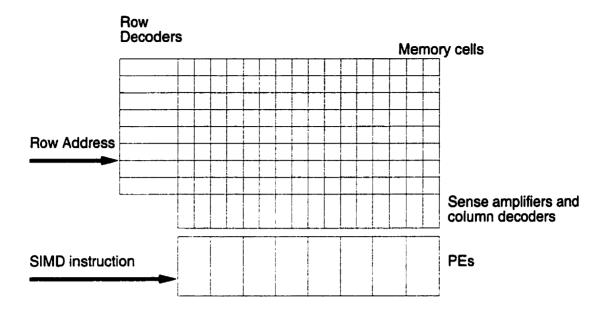

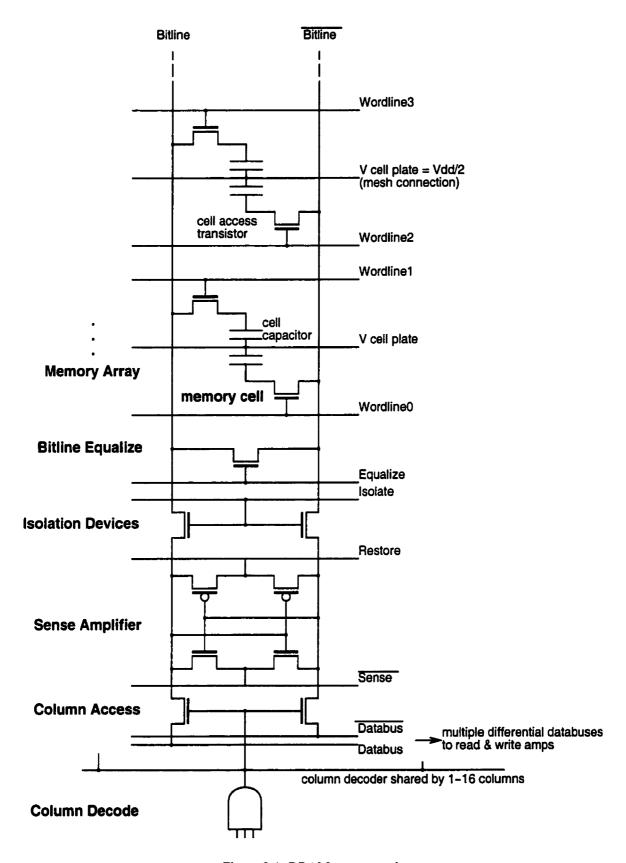

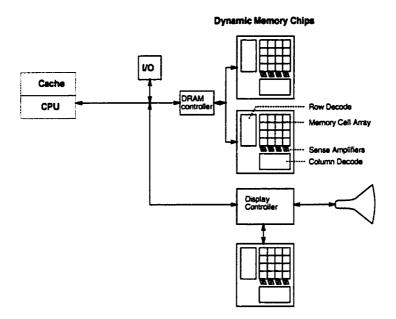

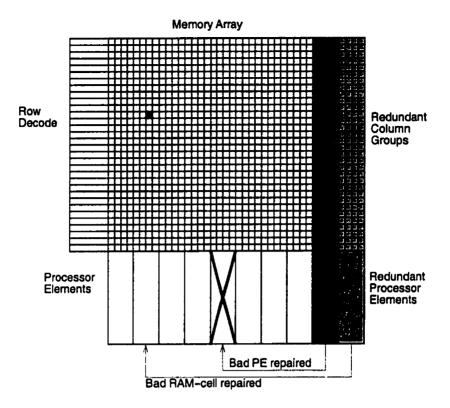

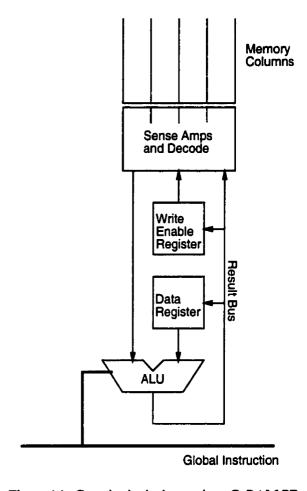

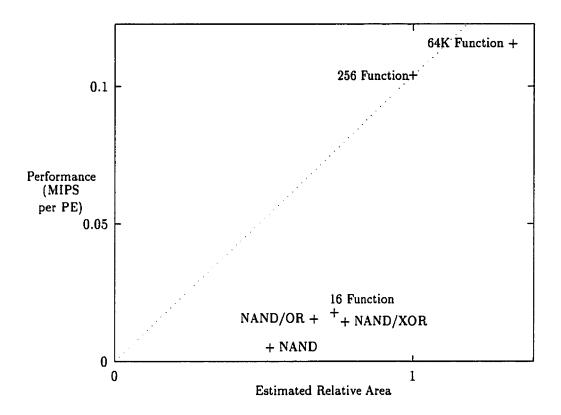

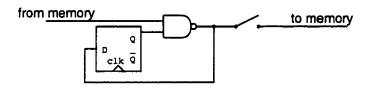

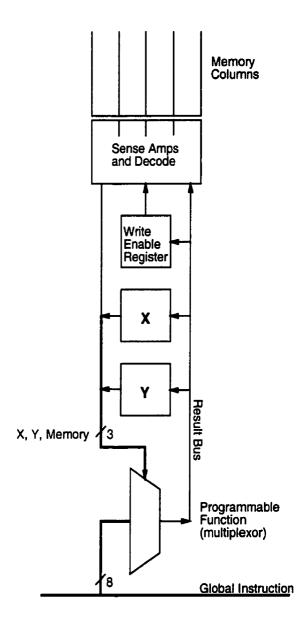

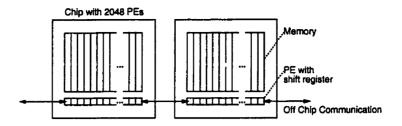

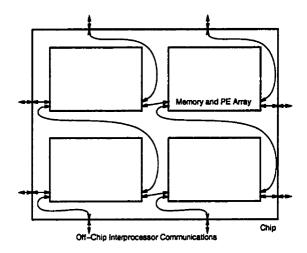

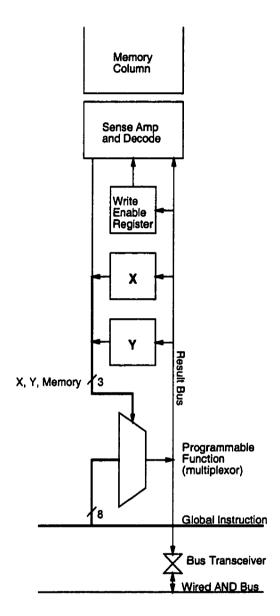

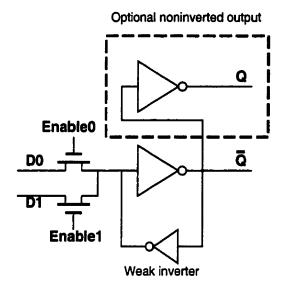

The key contribution of this dissertation is the proposal, design, and implementation of Computational RAM (C•RAM), an architecture that integrates memory and Single Instruction stream Multiple Data stream (SIMD) parallel processing onto a single chip to allow processors access to greater memory bandwidth. A C•RAM chip is a conventional memory chip, with the addition of processing elements. The processing elements are typically narrow-pitch 1-bit processors that have the same width as a small number (1-4) of memory columns. Figure 1.1 depicts a typical memory cell array augmented by processing elements, as would be found in a C•RAM chip. With the exception of the Processing Elements (PEs) at the bottom, the array corresponds to a conventional basic memory layout.

with this architecture, each CoRAM chip will contain many PEs. For example, in section 5.1 an 8 Kb SRAM chip with 64 PEs, and in section 5.2 a 4 Mb DRAM chip design with 2 K PEs will be described. A typical 64 Mb DRAM chip could contain as many as 32 K PEs. Each PE is kept simple, typically implemented with less than 100 transistors, as opposed to the 10 million transistors used to implement current high-end microprocessors. Nevertheless, we will show in chapter 6 that CoRAM can outperform workstations by more than a factor of 1000 for a large body of applications. All PEs execute the same instruction in the same cycle, making this a SIMD (Single Instruction stream, Multiple Data stream) architecture. An off-chip controller, in place of the DRAM controller, coordinates memory accesses and issues SIMD instructions to all PEs. The PEs each have "local" access to the physically adjacent portion of the memory array, namely the columns "above" them. Due to the fact that the memory wordlines run across a memory array shared by multiple PEs, all PEs must, within a single memory cycle, make memory accesses to the same address within their local

Figure 1.1: Memory cell array incorporating PEs

partition of memory; that is, C•RAM uses uniform memory addressing. A low-cost communication network allows for inter-PE communication.

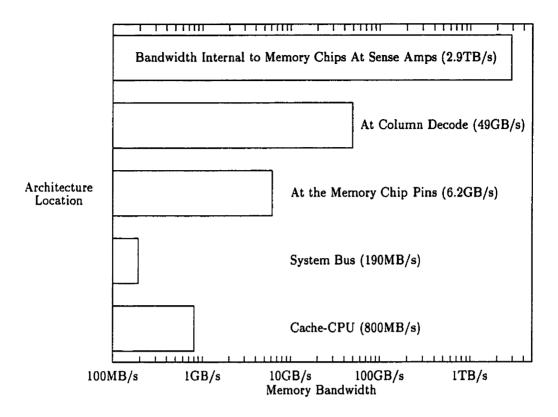

The CoRAM architecture is primarily motivated by two considerations: bandwidth and the performance/cost ratio. The first consideration is that an enormous amount of memory bandwidth exists within a memory chip and only a small portion of that is accessible from off-chip through the pins. The ratio of internal to external bandwidth is 470:1 for the 16 Mb DRAM described in section 3.1. Furthermore, we compare the memory bandwidth internal to the chips in a 32 MB memory sub-system with the bandwidth at the microprocessor (assuming optimistically a 100% cache hit rate) and show that the ratio is 3600:1. For applications with poor memory temporal locality and thus poor cache performance, the bandwidth in the memory can be 15,000 times greater than that available to the CPU. Memory bandwidth is an important limiting factor in the performance of current computer architectures [1]. Integrating processors into the memory chips by adding simple PEs to the memory columns allows much of the internal bandwidth to be exploited by the PEs directly.

The second consideration that motivates CoRAM is that, by integrating processors and memory, it is possible to provide a huge amount of processing power at minimal cost. We will show that PEs can be added to DRAM with only an 18% increase in area. The marginal cost increase for CoRAM relative to the cost of the entire system is small. For this small incremental price, CoRAM could be used to replace the system or graphics DRAM in a workstation and be used either as traditional

memory, or, for suitable applications, as a powerful SIMD parallel processor. For some scalable applications, the CoRAM performance scales linearly or nearly linearly with the number of CoRAM chips in a system.

We are particularly interested in DRAM (as opposed to SRAM) as a platform for CoRAM. DRAM is the most commonly used memory found in today's computers and video frame buffers, because of its high density and low cost. A commercial version of CoRAM based on low-cost DRAM could replace commodity memory in a variety of applications, thus adding array processing capability to the hardware. In order to do so economically, we examine massively parallel architectures where the PE adds a minimal incremental cost to the memory, while maintaining maximum compatibility with the commodity memory in function, density, and packaging.

When CoRAM is used as main memory or frame buffer memory for a conventional processor, the SIMD array and the host communicate by using shared memory without the latency of sending messages through an interprocessor communications network. CoRAM can be read and written at speeds similar to conventional memories. Further, the host can steal memory cycles from the CoRAM PEs (e.g. for filling a cache line) without altering the state of the PEs.

While SIMD computer architectures have been studied for three decades, there are several reasons why massively parallel SIMD machines have not become commonplace. The first reason relates to economics. Most SIMD machines have been designed for low quantity production and very high-end applications, so they are quite expensive.

The second reason why massively parallel SIMD machines have not become common place is that the memory and processors have not been typically implemented in the same chip. Hence, the maximum number of processors per chip is limited by the number of pins in an IC package. This separation of memory and processor is usually a result of design for small volume production. Using commodity memory chips for a particular SIMD design reduces design time, eliminates the need for memory designers on the project, and permits the use of an ASIC (application specific integrated circuit) manufacturing processes for the processor portion. ASIC processes have lower one-time costs per chip, but are not optimized for the manufacture of memory. When the processors have a large number of pins, the IC packaging cannot be as dense as memory packaging, resulting in computers with large physical volumes.

Thirdly, the host-to-SIMD interface often poses a bottleneck when results have to be shipped between the sequential host processor and SIMD array (often housed in different cabinets). Low bandwidths between host and SIMD array are common in these previous systems, and high latencies

(milliseconds) to set up the transfer — even for transfers of a single word — are not uncommon.

Fourthly, SIMD machines are conceptually more difficult to program than conventional von Neumann machines because the application (and data) must be partitioned among the processing elements by the application programmer (or a clever compiler).

We attempt to address all four of these issues in this dissertation. In contrast to most of the previous efforts, with CoRAM we aim to (i) leverage high volume DRAM manufacturing to keep marginal costs low, (ii) integrate PEs and memory for the bandwidth and packaging advantages, and (iii) provide a standard memory interface so communication between host and SIMD array can have low latency. While we do not provide a clever parallelizing compiler, we have found that the parallel applications are not much longer and are sometimes slightly shorter than the corresponding sequential versions. Also, the low latency shared-memory interface between host and CoRAM permits a gradual conversion of non-parallel application code to code that explicitly makes use of CoRAM's parallelism, starting with the most computationally-intensive portions.

In our opinion, because of the inherent restriction of SIMD architectures that each PE must perform the same operation in the same cycle, SIMD machines must have a significantly better performance/price ratio than MIMD (Multiple Instruction stream, Multiple Data stream) machines in order to compete. As we will show, a common pitfall in SIMD design is to continually add features that adversely affect performance/price and even net performance — reminiscent of the art of processor design prior to the adoption of RISC (Reduced Instruction Set Computer) philosophies. Once a SIMD architecture is encumbered by too many features, MIMD becomes more attractive. In contrast, we accept the fact that many applications will not be suited to run well on CoRAM even though CoRAM can run applications from a wide range of fields well. Hence, we do not pursue features that would assist only limited numbers of applications or would encumber the PEs.

In spending resources only on features that will enhance overall performance, our philosophy mimics that of early RISC designers. Two deviations from the RISC philosophy, however, are evident. First, we assume an abundance of parallelism in our applications, so that we can trade PE complexity for additional PEs. Second, our application set is not as well defined at the start, so our architectural tuning does not have a performance measure which is as objective as a SPEC benchmark set. The fastest computers (including parallel computers) probably won't be used exclusively for the same applications mix as the previous generation of machines. As Briggs noted [2], faster computers will make more computationally intensive applications viable.

"If you give people a machine with plenty-o-parallelism, someone's going to hack their

code to take advantage of it (and all the other hardware resources)."

Throughout this dissertation, we make the assumption that high-density DRAM-based CoRAM would be manufactured in high volume so that the cost per CoRAM chip might approach the cost of a similar sized DRAM chip. Getting from a design to high volume DRAM manufacture, or even a prototype is a difficult task in the business sense. Manufacturing one batch of DRAM wafers can displace nearly one million dollars of salable product. There are further costs for mask creation (50-300 thousand dollars) and for introducing a different design into the production stream. Thus the non-recurring (i.e. one-time or "up-front") costs for building processors into DRAM are high and there is no broker service (such as CMC or MOSIS) which helps to share the up-front costs by merging designs into "multi-project" chips. Although the initial costs are high, the performance/cost ratio of CoRAM can also be very high if manufactured in a DRAM process.

In the interest of minimizing up-front costs for a new massively-parallel processor, it is tempting to buy standard memory chips rather than integrating PEs into memory. However, with processors and memory on separate chips, the chip pin count will limit the number of processors that can be integrated on a chip. With limited processing power per chip, the further temptation exists to use standard microprocessors instead of designing custom chips. We resist these temptations by looking to the long-term picture and discounting the up-front costs.

The scope of CoRAM's applicability should not be limited to high-end computer needs. We hope that CoRAM will be used in applications where memory is currently employed and the addition of massively parallel processing would be of some use. This should include graphic and video frame buffers and desk-top computers. We believe that CoRAM would also be highly suitable for use in embedded systems for applications ranging from radar signal processing to high definition television.

#### 1.1 Dissertation Organization

An overview of past work in the fields of SIMD architectures and dynamic memory is given in chapter 2. In chapters 3 and 4 the design trade-offs and architecture of CoRAM are developed. To

<sup>&</sup>lt;sup>1</sup>NEC [3] produces 240 16 Mb dies on an 8-inch wafer. DRAM wafers are processed in large batches of, for example, 100 wafers. Functional 16 Mb DRAM chips sell for \$55US to \$60US (July 1995). The opportunity cost of making a batch of prototype chips in a production DRAM foundry instead of readily marketable DRAMs is therefore approximately ( $\frac{$55}{chip} \times yield \times \frac{240 \ dies}{wafer} \times \frac{100 \ wafers}{batch}$ ) = yield times 1.3 million US dollars. Of course memory prices fluctuate and yields improve as a process matures.

show that our architecture is viable, we designed and tested a prototype chip and designed a DRAM based PE, both of which are described in chapter 5. Examples of applications that are able to exploit Coran are given in chapter 6.

## Chapter 2

### **Prior Art**

In this chapter, we briefly describe some SIMD multiprocessor architectures and memory technology, since the design of CoRAM involves both. A large number of SIMD architectures have been proposed over the years. Here, we focus on massively parallel SIMD architectures that either have been manufactured in quantity or are particularly interesting.

For DRAM, on the other hand, a detailed description of typical circuits and architectures is provided. We focus on those aspects of DRAM that might affect the integration of PEs.

#### 2.1 Massively Parallel SIMD Processors

Flynn defined the SISD, SIMD, and MIMD classes of computers in 1966 [4]. SISD (Single Instruction stream, Single Data stream) is the classic uniprocessor. Multiple copies of these uniprocessors, each with its own instruction fetch and decode units, and datapath, can be tightly coupled together to build a MIMD (Multiple Instruction stream, Multiple Data stream) computer. If, however, multiple processor datapaths are driven by a single instruction decode circuit, then the computer is classified as SIMD. SIMD computers have the obvious advantage of economizing on instruction decode circuitry and feature intrinsically synchronized operation. Chapter 3 describes other advantages of SIMD architectures as applied to computing in memory.

The SIMD systems we describe in this section are listed in table 2.1. The table provides:

- year of introduction

- whether the PEs and memory are on the same chip

- if the PEs and memory are integrated

| Machine           | year | on-chip main | mem.   | mem. | local | PEs / | PE     | max  | data-  | autonomous | autonomous |

|-------------------|------|--------------|--------|------|-------|-------|--------|------|--------|------------|------------|

|                   | ľ    | mem.         | redun- | b/PE | mem.  | chip  | redun- | PEs  | path   | memory     | network    |

|                   |      |              | dancy  |      |       |       | dancy  |      | 1      | addressing |            |

| STARAN            | 1972 |              |        | 256  |       | 8     |        | 1K   | 1      |            |            |

| ICL-DAP           | 1976 |              |        | 4096 | 1     | 16    |        | lK   | 1      |            |            |

| VASTOR            | 1978 |              |        |      | 1     | 1     |        |      | 1      |            |            |

| MPP               | 1981 |              |        |      | 1     | 8     |        | 16K  | 1      |            |            |

| GAPP              | 1984 | 1            |        | 128  | 1     | 72    |        |      | 1      |            |            |

| CM-1              | 1985 |              |        | 4096 |       | 16    |        | 64K  | 1      | note l     | 1          |

| Pixel Planes 4    | 1987 | 1            |        | 72   | 1     | 64    |        | 256K | 1      |            |            |

| AIS               | 1988 |              |        | 32K  | 1     | 8     |        | 1K   | 1      |            |            |

| BLITZEN           | 1989 | 1            |        | 1024 | 1     | 128   |        | 16K  | 1      | 1          |            |

| Pixel Planes 5    | 1989 |              |        |      |       |       |        |      |        |            |            |

| MasPar MP-1       | 1989 |              |        |      | 1     | 32    |        | 16K  | 4      | 1          | 1          |

| C•RAM             | 1989 | 1            |        | 128  | 1     | 64    |        |      | 1      | Ī          |            |

| DAP 610C          | 1990 |              |        | 256K | 1     | 64    |        | 4K   | 1 & 8  |            |            |

| VIP               | 1990 | 1            |        | 256  | 1     | 256   |        | 256  | i      |            |            |

| TI-SVP            | 1990 | 1            |        | 320  | 1     | 1024  |        |      | ı      |            |            |

| CM-2              | 1990 |              |        | 1M   |       | 16    |        | 64K  | 1 & 64 | note 1     | 1          |

| MasPar MP-2       | 1993 |              |        |      | 1     | 32    |        | 16K  | 32     | 1          | 1          |

| SRC-PIM           | 1994 | 1            | note 2 | 2048 | 1     | 64    |        | 256K | 1      |            |            |

| NEC-IMAP          | 1994 | 1            | note 2 | 32K  | 1     | 64    |        |      | 8      | 1          | 1          |

| EXECUBE           | 1994 | 1            | 1      | 512K | 1     | 8     |        |      | 16     | 1          | 1          |

| C•RAM             | 1995 | 1            |        | 480  | 1     | 512   |        | 4096 | 1+     |            |            |

| NEC-PIPRAM        | 1996 | 1            | note 2 | 128K | 1     | 128   | 1      |      | 8      |            |            |

| SONY-linear array | 1996 | 1            |        | 256  | 1     | 4320  |        |      | ı      |            |            |

| C•RAM-DRAM        |      | 1            | 1      | 2048 | 1     | 2048  | 1      | 1M   | l      |            |            |

Table 2.1: Characteristics of massively parallel processors

note 1: autonomous memory addressing implemented in software note 2: memory redundancy implemented with spare blocks

- whether that integrated memory is protected against manufacturing defects by redundancy

- the amount of memory per PE

- the number of PEs per chip

- the number of PEs in a fully configured system

- the width of the PE datapath

- whether or not memory addresses are autonomously controlled by each PE

- whether or not interprocessor communications network destinations are autonomously controlled by each PE

We use the term autonomous memory addressing to describe SIMD machines that allow the PEs to calculate their own memory address for accessing their private memories. The opposite is uniform memory addressing where all PEs access the same address within their local memories. Similarly, interprocessor communication network routing is classified as autonomous network routing if PEs

can independently specify the target PEs and *uniform network routing* if all messages are routed in the same pattern.

It is interesting to note that none of these systems has been particularly economically successful to date. It is difficult to identify the reasons for this failure, but we believe that the reasons given in the introduction played an important role: i.e., (i) most SIMD machines were not designed for quantity; (ii) many lack or have poor SIMD processor - memory integration; (iii) these machines typically have a poor host - PE data interface; and (iv) without automatic parallelizing compilers, SIMD architectures present a more difficult programming model<sup>1</sup>. We suspect (and cite examples) that these limitations are due to the fact that the goal of minimizing volume manufacturing costs was traded-off for minimizing one-time design costs.

An example of minimizing design effort is the use of standard memory chips. If, instead, memory and PEs had been integrated, then pin limitations would have been avoided, thereby permitting more PEs per chip; yet this was seldom pursued at the time when we started our work, due in part to the higher up-front costs. Of those designs that do combine PEs and memory, most do not fully exploit the internal memory bandwidth, nor do most use the most dense memory available.

Stone was perhaps first to propose the integration of processors and memory in the memory of a computer in 1970 [6]. At a time when ferromagnetic core memory dominated main memory systems, he proposed integrating processors into the semiconductor cache memory. In the two decades that followed, the understanding of how to integrate memory and processors, as well as the will to do so, has been weak. CoRAM was the first chip with processors integrated into memory such that the memory was externally accessible and could be used as computer main memory [7, 8].

Where processors and memory have been integrated, redundancy (to permit the repair of manufacturing defects) has not been widely used, limiting their yield or transistor count, thus increasing the price of parts or limiting levels of integration, respectively. This is another reason why massively parallel processors currently occupy a high price niche.

In the following, we examine for each of these systems: the class of applications targeted, the features of the PEs, the style of the memory, and the interprocessor communications network. As well, we elaborate on other unique or interesting features. The machines are presented in order of date of introduction of the machine, product family, or chip.

<sup>&</sup>lt;sup>1</sup> Although automatic techniques for detecting, categorizing, and exploiting parallelism in programs are well known [5], I believe that in the majority of SIMD application programs, the programmer has either explicitly declared the parallelism or has written the program so as to make the parallelism more apparent to the compiler.

#### **STARAN**

STARAN was the earliest production SIMD machine [9-15]. It was built by Goodyear Aerospace under contract from NASA Goddard Space Flight Centre. It was used for applications such as satellite image processing and radar signal processing for AWACS (Airborne Warning And Control System). The processing elements are bit serial, meaning that the datapaths (ALU, registers, etc.) are 1 bit wide and that operations on larger data items (e.g. integers) are synthesized from a sequence of 1-bit operations. Each PE can perform two arbitrary boolean functions of 2 inputs (the two inputs being a data register and the output of the interprocessor communications network) simultaneously in one cycle. Each PE contains a mask register and 2 data registers. The mask register is used to selectively halt some PEs when executing conditional code, a common feature in SIMD machines. STARAN shares a common pool of memory among the PEs, which is an uncommon feature among SIMD machines. Most SIMD machines have memory permanently dedicated to each PE (i.e., they implement *private distributed memory*). The *flip* permutation network always supplies operands to the ALUs. When the PEs perform operations on local data, the "identity permutation" is used.

Being an expensive machine, only five STARAN systems were produced (2 with 512 PEs, 3 with 1024 PEs). A variant of STARAN was used into this decade in AWACS (airborne military radar, a high budget application). The design of the PEs, memory, and interconnect make high levels of integration difficult. Only 8 PEs are integrated on a die. Since memory and PEs are in different chips, the chips would become pin-limited before large numbers of PEs could be integrated.

#### DAP

The ICL DAP (Distributed Array Processor) was first designed to be a multi-purpose active memory module for the ICL 2900 mainframe [16]. The architecture was intended to be general purpose (as far as SIMD can be) and has been used for signal processing and text indexing, as well as for classified military applications. The first implementation had 1024 PEs built out of medium scale integration TTL components. A CMOS version with 16 PEs per chip has since been developed. Each one-bit processor contains a full adder and 3 registers. Standard memory chips are used for the 4 Kb of memory per PE. Each PE communicates with its 4 neighbours on a 2-dimensional grid. A 4-to-1 multiplexor in each PE selects the network output of one of the adjacent PEs as that PE's network input.

Active Memory Technologies Ltd. further developed the DAP 500 as a SIMD "back-end

processor" to complement a VAX minicomputer or SUN workstation host [17, 18]. The DAP 500 contains a grid of  $32 \times 32$  PEs with 64 PEs integrated into one chip. Thirty-two bus lines in each of the row and column directions are provided explicitly for IO.

To improve arithmetic performance, the DAP 510C (32 × 32 PEs) and DAP 610C (64 × 64 PEs) have an 8-bit math co-processor associated with each PE, but located on a separate chip. Each math co-processor has an 8-bit adder and 8-bit registers, but no multiplier. The separation of the PE and co-processor into different chips allowed the AMT DAP designers to re-use the existing PE chip, but in doing so, they restricted the 8-bit co-processor's memory path to the 1-bit path provided for the original PE.

#### **VASTOR**

VASTOR (Vector Associative Store - TORonto) was designed at the University of Toronto for applications involving searches and other associative operations [19-22]. The TTL implementation was built around the Motorola MC14500B industrial control unit, which had a one-bit-wide datapath, an accumulator, a seven-instruction ALU, and write enable logic. VASTOR has since been implemented both with TTL MSI components and custom silicon [23, 24]. Custom ICs containing a single PE were built, but were never functional due to manufacturing defects. High level language programming was done in APL [25].

Interprocessor communication is provided by a linear nearest-neighbour communication network (a 1-dimensional shift register) and two combine networks. The shift register is also used for IO. A combine network takes multiple inputs and produces a single result, such as, for example, a summation tree built of adders. The output of the flag register in each PE is connected to the two combine networks. The OR combine network can be used to signal the controller that one or more matches have been found. A novel " $\geq 2$  responding" combine network reports if more than one PE has its flag set, and can be used to determine if the result of a search has been pared down to a single item. The global-OR and " $\geq 2$  responding" combine networks are implemented with linear chains of logic that have O(n) depth and delay.

#### **MPP**

The Massively Parallel Processor (MPP) [26, 27] built by Goodyear Aerospace for NASA Goddard Space Flight Center contains several  $128 \times 128$  processor planes. The MPP was designed

to process Landsat satellite images so it makes heavy use of its 2-dimensional grid connectivity. Each PE contains a one-bit full adder. These bit-serial processors are packaged 8 to a chip. Memory is off-chip from the PEs. The MPP was used for more than a decade before it was de-commissioned.

#### **GAPP**

NCR Corporation, using an architecture licenced from Martin Marietta Electronic Systems, produced a chip with a  $6 \times 12$  array of bit-serial processors and local memory, which they call the Geometric Arithmetic Parallel Processor (GAPP) [28, 29]. GAPP was designed for image processing and has been used in military applications. The PEs operate on instructions with 5 fields that control the full adder, 3 data registers and a communications register. Each PE can communicate with its four nearest neighbours on a 2-dimensional grid and with a private 128-bit on-chip memory. Interprocessor communication and ALU operations can proceed concurrently.

Due to their complexity, the 72 PEs take up slightly more than half the chip. The memory arrays in GAPP do not support redundancy, unlike most commercial RAMs. While integrating the PEs and memory saves IC pins and communication overhead, GAPP does not include a direct mechanism for a host processor to access the memory in the GAPP chips. Instead, data to be sent to the host must be shifted through PEs to the edge of the GAPP chip. If the chips are connected in an array as the manufacturer intended, the data must be shifted to the edge of the array of processors.

#### **Connection Machine**

The Connection Machine (CM) was designed by Thinking Machines Corp. for use in connectionist (synthetic neural network) research [30]. Most CM cycles, however, have been used for scientific computation. A fully configured CM-1 has 64 K 1-bit processors with 4 Kb of memory per PE. The CM-1 native instructions specify 3 memory addresses, a register, and two ALU operations. A dual ALU performs two arbitrary 3-input boolean functions of a register and two memory locations, placing the two results in a register and a third memory location. Three-operand ALU instructions predominate in RISC microprocessor architectures, where a triple-ported register file provides the necessary operand throughput, but we question the use of a three-operand instruction for the CM-1 where each operand requires a separate cycle for a memory access. Commodity DRAM is used as main memory. Sixteen PEs plus an autonomous hypercube network router are placed on a chip. The peak integer performance of a 64 K PE CM-1 is one billion 32-bit additions per second.

The CM-1 C\* compiler generates code that runs on the host processor and issues PARIS (PARallel Instruction Set) macro instructions (e.g. ADD\_16bit) to the CM-1 sequencer. This microcoded sequencer in turn translates the macro instructions and issues native SIMD instructions to the PEs. Branches and other scalar operations coded in the high level language do not get sent to the sequencer but are executed on the host.

The next generation machine, the CM-2, adds a 64-bit floating-point chip to every group of 16 PEs [27]. Also, within groups of 32 PEs, the PEs can access each other's local memories. The large 1-Mb-per-PE memory system is built with commodity DRAM chips. Its larger-than-average size was chosen to permit multi-tasking. The hypercube communications network can be used for autonomous message routing for send and get operations, as a uniformly routed network for patterned communications, or as a combine network.

While Thinking Machines Corporation has enjoyed the most publicity and highest sales of any massively parallel SIMD machine manufacturer to date, the limitations of their designs caused them to switch from manufacturing SIMD systems to MIMD systems in 1991. Without memory integrated into the PE chips, the number of PEs on a chip is limited to 16 PEs in the CM-2. According to Thinking Machines, the designers of the CM-5 chose to build a MIMD machine using commercially available microprocessor chips (SPARC) with one 32-bit wide processor per chip instead of custom chips with 16 1-bit wide processors per chip for reasons of cost, performance, and availability.

#### **Pixel-Planes**

The Pixel-Planes machine [31-35], as the name suggests, was designed for computer graphics applications. In particular, it is capable of rendering all pixels in an object in parallel. The Pixel-Planes-4 machine integrates 64 bit-serial PEs, each with a small 72-bit memory, on a chip together with a pipelined tree-structured bit-serial linear expression evaluator. Expressions of the form F(x,y) = Ax + By + C, (where x and y are the PE co-ordinates, and A, B, C are scalar variables) are efficiently evaluated in parallel, exploiting the similarities in the binary addresses of neighbouring PEs. Such linear expressions are used, for instance, to shade a pixel or determine if it lies inside a polygon.

The next generation Pixel-Planes-5 integrates 128 PEs, each with 208 bits of memory, and a quadratic expression evaluator into a single chip. The Pixel-Planes-5 was developed as a MIMD-SIMD hybrid to address the problem that graphic objects are often small, making it inefficient to involve the entire SIMD array in rendering an object which only occupies a few pixels. The MIMD

Figure 2.1: X-Net interprocessor communication network. A bi-directional communications port on each corner of each PE is wired to 3 neighbours.

subsystem, built with DSP chips, pre-processes the graphic objects (including co-ordinate transforms and clipping) and sends them to the appropriate SIMD chip. The SIMD subsystem divides up image space among the chips so that different chips can be rendering different objects.

By building a massively parallel machine for a specific application, the designers of Pixel-Planes-5 were able to create a reasonably well balanced system and the fastest rendering machine of its time. The authors comment that for many operations, data transfer between the host and Pixel-Planes dominates execution time. Each existing version of Pixel-Planes has been a one-off design, built at significant expense.

#### C•RAM

In November 1989, the first C•RAM chip designed at the University of Toronto was sent for IC fabrication [7]. These designs had narrow PEs, the pitch of an SRAM column, integrated into the memory array. A memory interface allowed direct off-chip memory access. The architecture and chip are described in more detail in the following chapters. This work has been referenced by some of the subsequent designers [36, 37, 38, 39].

#### **BLITZEN**

BLITZEN [40, 41, 42] is a successor to the MPP. Designed at the Microelectronics Center of

North Carolina, it was partially funded by NASA Goddard Space Flight Center. A BLITZEN PE contains a 1-bit full adder; a 30-bit shift-register/accumulator; and registers for masks, conditional operations, carry, and communications. A system contains 16 K PEs, 128 per chip. Each PE has 1 Kb of on-chip memory that can be addressed uniformly by the SIMD controller, autonomously using the contents of the shift register, or a combination of the two.

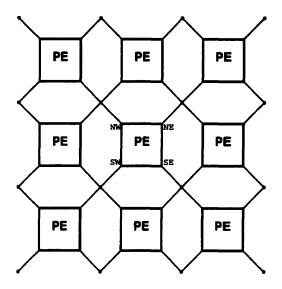

The X-Net interprocessor communication network, shown in figure 2.1, is a 2-dimensional grid plus diagonals so that every PE is connected to 8 neighbours (North, NE, E, SE, S, SW, W, NW). The bi-directional port on, for example, the North East corner of one PE is wired to the ports on the NW, SW, and SE corners of its E, NE, and N neighbours respectively. A 2-dimensional X-Net node can communicate with its 8 neighbours (including 4 diagonal neighbours) while using the same number of "pins" as a grid (which lacks communication with diagonally adjacent nodes). All PEs uniformly transmit to one corner and listen on another. If only one network input can be read at a time, then 8-neighbour connectivity has no advantage over 4-neighbour connectivity when the values from all 8 neighbors are required.

An OR-tree connecting all PEs (not shown) is also provided for combine operations. Moreover, IO is accomplished with a 4-bit bus for every 16 PEs.

While autonomous addressing is a useful feature for some applications, it has a cost in that the row-decode circuitry occupies nearly half the area of BLITZEN. This high area cost is due to the fact that the row-decode circuitry is replicated for the 4 columns of memory associated with every PE. In contrast, DRAM designs tend to use one row decoder for 2048 or more columns. Fewer row decoders driving longer wordlines could have been used in BLITZEN, had only uniform addressing been implemented. Because of the autonomous addressing and the low density ASIC memory, only 128 Kb of RAM and 128 PEs fit on the large  $11.0 \times 11.7$  mm die in a  $1\mu$ m process. The dies are packaged in 176 pin pin-grid-array chips, a physically large package. While the design contains more memory (128 Kb) than previous SIMD chips, its density is still 8 to 32 times lower than that used in similar generation IC processes designed for SRAM and DRAM respectively. Redundancy was not used to protect chips against defective memory cells or PEs. Consequently, according to project participants, yields were quite low.

#### MasPar

MasPar Corp. designed the MP-1 as a moderately priced SIMD computer for general scientific computing with a high performance/price ratio [43, 44, 45, 46]. The MP-1 uses a DEC workstation

as a host. Chips containing 32 4-bit processors are assembled into machines with 1 K to 16 K processors. The ALU contains an adder, multiplier, and support for logical operations. MasPar integrates a significant amount of static register memory into the PE die but uses off chip commodity DRAM for PE main memory. PEs can autonomously address their local memory, but with a slower access rate than when uniformly addressed. The memory bandwidth of the 16 K processor machine is 12 Gbytes/s, about one tenth of the register bandwidth of 117 GB/s, suggesting that memory bandwidth may pose a bottleneck, especially considering the fact that this design and others listed in this chapter do not have cache memories. Communication is supported by a 2-dimensional 8-neighbour X-Net as described for BLITZEN (figure 2.1), and a lower bandwidth circuit-switched global router which implements autonomous routing.

The next generation MasPar MP-2 chip has 32 PEs as did the MP-1, but the processor datapath has been increased from 4 to 32 bits [47]. Each PE contains approximately 14000 transistors, not including registers, or 450 transistors per bit of processor width. Despite the 8-fold increase in processor width, multiplies are only 4 times as fast as on the MP-1. A fully configured system would have 16 K PEs on 512 custom processor chips plus 3072 commodity DRAM chips. The total system memory bandwidth is 23 GB/s.

#### **VIP**

The Video Image Processor (VIP) was designed at Linköping University to process a video raster line at the horizontal refresh rate [48, 49, 50]. VIP chips are thus more likely to be combined in a pipeline (each performing different image processing operations) than in an array. A chip contains 256 PEs, each with 256 bits of memory and a 1-bit adder. A relatively high density is achieved with a compact ALU and a 3-transistor-memory-cell DRAM array. The 3-transistor cell is denser than the SRAM used in prior SIMD-plus-memory designs. A 1-transistor memory cell in an ASIC or DRAM processes would be denser still, but would have required more design effort. Video IO is handled by separate input and output shift registers that run through the PEs.

#### **SVP**

The Serial Video Processor (SVP) was designed at Texas Instruments for real-time signal processing on a video stream [51, 52]. The SVP chip contains 1024 bit-serial PEs, each containing a full adder and connected to 320 bits of memory. The PEs are organized in a row and are connected to

two memory banks so that two independent 1-bit operands can be accessed every cycle. Video-rate IO is handled by dual ported memory with a 40-bit wide path for input and a 24-bit wide path for output. Interprocessor communication is performed through a 1-bit wide left-right communications network that connects adjacent PEs, as well as next-to-adjacent PEs.

The prototype receives SIMD instructions from off-chip, but the designers intended to put instruction memory and decode circuitry on a production version of the chip so it could be used as a stand-alone video filter.

While the SVP used DRAM memory cells, which are smaller than SRAM memory cells, the large 1.5 million transistor count suggests that a large, 3-transistor dynamic memory cell was used. The consequence is a large 14.4 mm × 11.0 mm die. Since the chip has 107 signal pins plus an unspecified number of power pins, it is packaged in a large 179 pin PGA. This package is 15.7 cm<sup>2</sup> or 10 times the actual die area. If minimizing printed circuit board area and system cost are desirable then SIMD chips would have to be designed with fewer pins<sup>2</sup>.

#### **IMAP**

The IMAP chip (Integrated-Memory Array Processor) was built in a 0.55  $\mu$ m BiCMOS process at NEC for the purpose of low-level image processing [53, 54]. Each chip contains 64 8-bit PEs and 2+Mb of SRAM. Each PE contains an 8-bit adder, but multiplication is performed by table lookup in the PE's memory. The 2 Mb of SRAM (not including redundant banks) is arranged as a 4 K  $\times$  8 bit array per PE and can be addressed uniformly or the low order bits (column address) can be addressed autonomously. The IMAP uses a 4-transistor SRAM cell which is more expensive than DRAM, but also faster. Since the IMAP SRAM is twice as fast as the PE, the full memory bandwidth cannot exploited by the PEs. Interprocessor communication can be performed using the 8-bit bi-directional shift paths between left-right adjacent PEs or using a 1-bit wired-OR bus. IO transfers are done through a 4-bit memory bus or one of two 8-bit unidirectional shift registers. The memory access bus allows low-latency<sup>3</sup> memory accesses by a host processor.

The IMAP designers recognized the need for memory redundancy to improve chip yield. Their particular implementation of redundancy is, however, more expensive than redundant memory rows or columns (as described later in section 2.2.4). Eight pairs of PEs can be connected to 8 blocks

<sup>&</sup>lt;sup>2</sup> At this time, minimizing system cost precludes using more expensive, high pin count chip-on-board techniques.

<sup>&</sup>lt;sup>3</sup>We consider memory accesses via the external memory access bus to have low latency because the bus allows external memory operations with access times similar to conventional memories and the data takes a direct path, rather than traversing multiple hops in a communications network.

of memory plus 2 spare blocks. For a 25% overhead in memory area plus bus switches, only 2 manufacturing defects (in different blocks) can be repaired per 16 PEs. Each PE has approximately 7000 transistors (875 transistors per bit of datapath) and occupies an area of 419  $\mu$ m  $\times$  2628  $\mu$ m.

A follow-on design by NEC, the PIPRAM, integrates 128 8-bit PEs of a similar design into 16 Mb of DRAM memory.

#### **EXECUBE**

EXECUBE [55, 56] was designed at IBM Federal Systems (now Loral Federal Systems-Owego) for embedded high performance processing including radar tracking and pattern matching. A chip contains 8 16-bit PEs and 4.5 Mb of DRAM memory. The 8 PEs can operate in a MIMD mode where the PEs fetch their own instructions, or a SIMD mode where the PEs receive a broadcast instruction from off-chip. Each PE is connected to two 32 K×9 bit DRAM arrays, with the ninth bit being parity. Since each DRAM array, with its own support logic, is complete and independent, autonomous memory addressing as well as row and column memory redundancy are easily supported. Each PE has four point-to-point links for interprocessor communication. The 8 PEs are cube-connected on-chip, but only 8 links are available for off-chip communication (less than the 24 links required for a full 3-dimensional mesh).

EXECUBE is based on high-density low-cost 1-transistor commodity DRAM built in a 4 Mb DRAM process. The DRAM arrays occupy 63% of the 14.7 mm squared die. The processors are implemented in "sea of gates" semi-custom logic. The EXECUBE's large die, large number of signal pins, and moderate power consumption require a large 208 pin IC package.

The SIMD/MIMD modes and autonomous memory addresses gives the chip excellent flexibility. In the MIMD mode, the programmer is presented with multiple conventional RISC microprocessors with message-passing communication between them. By building *onto* rather than *into* a DRAM array, EXECUBE's designers avoid working with low voltage signals, thus reducing design time, and increasing the certainty of the chip being functional. However, the implementation uses predefined memory macro-cells (the DRAM arrays) which has a cost in terms of power and delivered bandwidth. For example, after the column decoding, the data from each macro is accessed through an 8-bit data bus<sup>4</sup>, even though 128 sense amplifiers are simultaneously active internally. Also, the chip has a 2.7 W power consumption, in part because all memory arrays on the chip (2 arrays per

<sup>&</sup>lt;sup>4</sup>The 1 bit of parity per 8 bits of data is not included in the memory and datapath sizes described.

processor) are active during a memory access. The internal memory bandwidth, with its 128-bit wide datapath per array, goes largely underutilized, providing only page-mode "caching" of a memory row.

#### **Terasys**

The Terasys system is a SIMD processor in memory built by the Center for Computing Sciences (formerly the Supercomputing Research Center) and funded by the NSA (US National Security Administration) [57, 58, 36]. The prototype 32 K PE Terasys system attaches to a Sparc-2 and can be accessed as memory. Each of 512 chips contain 64 bit-serial PEs with 2 Kb of SRAM per PE.

In anticipation of building large systems and running long duration applications, error detection and correction is provided for correcting single-bit errors and detecting two-bit errors. The PEs and memory system allow masked writes. In this implementation of masked writes, the PEs first read the memory to obtain the old values, and write back the old or new values depending on the PEs' flag register. Memory redundancy, but not PE redundancy, is provided to improve yield. The 128 Kb of SRAM memory per chip was several generations behind the highest SRAM densities available at the time.

Interprocessor communication in the Terasys is supported by a global OR network, a partitioned OR network, and a parallel prefix network. The partitioned OR network can be partitioned into groups with sizes which are powers of two greater than or equal to 64 (the size of a chip). The parallel prefix network can be set to different levels allowing PEs separated by different distances to communicate. At level 0, the parallel prefix network provides communication to the left and right neighbouring PEs. At level l, processor  $i2^{l}$  can receive data from the processor  $2^{l}$  processors to the right of it through the parallel prefix network.

The designers of Terasys make effective use of the internal memory bandwidth. Their high performance goals, including the use of the Terasys design as memory for a vector supercomputer, makes the cost of SRAM acceptable.

Cray Computer built and tested a prototype 256 K PE "octant" of Processors In Memory (PIM) chips for the Cray-3, to be called the Cray-3/SSS (Super Scalable System).

#### **Linear Array DSP**

The Sony Linear Array DSP [59] has 4320 PEs, each with 256 bits of ASIC DRAM memory. Each ALU contains a 1-bit full adder and a Booth decoder for multiplies. As this chip was designed to speed up video format conversion, it has a 64-bit input channel and a 32-bit output channel. The die is packaged in a bulky 256 pin PGA. As with other designs built with ASIC DRAM, the memory cells are smaller than SRAM cells but larger than standard DRAM cells.

#### **Summary**

Many of these massively parallel SIMD machines, especially the earlier ones, do not attempt to integrate memory and processors (see table 2.1). Fortunately, however, the designers of more recent chips and systems have seen the importance of this integration. Of those which do integrate memory and processors, all but two (EXECUBE and PIPRAM) use less dense varieties of memory than the 1-transistor DRAM cell. Only Terasys, IMAP, and their successors are usable as memory. Insufficient attention is paid to improving yield through the use of redundancy. Where redundancy is used, it is most often not implemented with the efficiency of that seen in commodity memories. Most of these designs have large numbers of pins and are mounted in IC packages which occupy many times the area and volume of the original die.

In contrast to the systems described above, CoRAM integrates processors and memory, uses dense memory designs with redundancy to improve yield, and has a low pin count so that it can be packaged in a TSOP package like memory. These features are described in more detail in chapters 3. 4. and 5.

#### 2.2 Memories

CoRAM integrates processors into the memory. This section gives a brief introduction to DRAM circuits, with emphasis on those circuit elements that will interact with the PEs that are added to memory.

Memory is a driving force in integrated circuit technology — it leads in number of devices per die and device dimensions. Due to its prominent position, the available literature is enormous. See [60-127] for some of the more relevant articles. The book *Semiconductor Memories* by Betty Prince [116] is a fairly comprehensive reference. In this section, a tutorial on DRAM circuits and

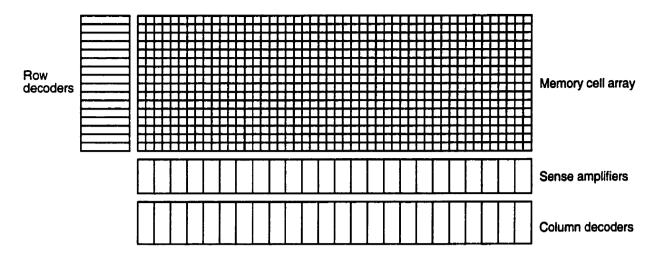

Figure 2.2: Generic DRAM cell array

operation is provided, followed by descriptions of DRAM chip interfaces, characteristics of DRAM IC processes, memory redundancy, and "smart memories".

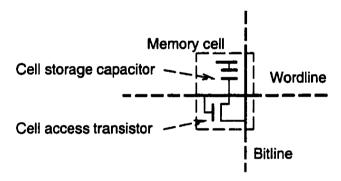

Figure 2.3: DRAM memory cell

Briefly, commercial dynamic memory is organized in 2-dimensional arrays of 1-bit memory cells (shown in figure 2.2). A memory chip contains multiple copies of these memory arrays. Row decoders are located at one side of the array, and sense amplifiers (sense amps) and column decoders are placed along the bottom. In 16 Mb and later generation DRAMs the column decoders and sense amps are often shared by multiple arrays in order to save area.

Figure 2.3 shows the components of a 1-transistor DRAM cell. Each cell is connected to a wordline and a bitline. Wordlines, which run in the row direction (also referred to as the X direction in the literature), select a row of cells. Bitlines run in the column direction (Y direction) and conduct the contents of selected cells to the sense amplifiers at the bottom of the array. Each bit is stored as a charge on a capacitor. A MOS access transistor, under the control of a wordline, selectively connects the capacitor to the bitline.

In order to reduce the energy used in a memory cycle, not all of the sense amps or associated memory arrays are active during any given cycle. The most significant bits of the row address determine which memory arrays and sense amps will be used in a cycle. DRAM specifications will quote the required number of refresh cycles in order to restore every memory cell in the chip. Since a sense amp can refresh exactly one memory cell, the number of active sense amps is memory capacity retresh cycles.

While parameters within memory architectures keep changing, some typical ratios are provided. Wordlines can cross 4096 or more bitlines; column decoders can select 2 to 16 sense amps; the number of refresh cycles can range from 1 K to 16 K, and all are growing over time. Through multiple DRAM generations, however, a sense amp is typically connected to a pair of (active) bitlines, each with 128 memory cells.

#### 2.2.1 DRAM Circuits

In this section, DRAM circuits as used in the high density CoRAM are first described. DRAM architectures vary widely, but many of the underlying circuits bear a strong resemblance to each other. Since the DRAM "platform" on which the high density CoRAM PE design is based is proprietary, we use the DRAM design by Gillingham et al. (described in [94]) as a reference (which is another MOSAID Technologies design incorporating some of the same design philosophies) and will be referred to as the reference DRAM architecture. Figure 2.4 is a schematic of one column of the memory array, with only four of the memory cells shown. A folded-bitline architecture is used, meaning a differential sense amplifier is connected to a folded bitline pair comprised of a true and a complemented bitline, which run parallel to each other and are matched in size and capacitance. Power (typically 3.3V or 5V, and decreasing with technological advancements) and ground are given the names  $V_{DD}$  and  $V_{SS}$  respectively.

The precharge, sensing, and memory access operations are now explained in detail, with explanations of what voltages are used. Before a row access, the memory is in the precharged state with bitlines precharged to  $\frac{V_{DD}}{2}$ , isolation transistors turned on with the *isolate* signal at  $V_{DD}$ , and sense amps and wordlines turned off.