# A Methodology for Analog Circuit Design and Knowledge Transfer.

by

Jean-Marc G. Patenaude, BASc, P. Eng.

This thesis is submitted to

the Faculty of Graduate Studies and Research

in partial fulfilment of

the requirements for the degree of

Master of Engineering

Department of Electronics

Carleton University

Ottawa, Ontario, Canada

April 18, 1996

© Copyright, 1996

Jean-Marc G. Patenaude

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Out file Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his, her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant la Bibliothèque nationale ·du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse la disposition personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-13848-8

Name Sean - Marc. Pate Man de.

Dissertation Abstracts International is arranged by broad, general subject categories. Please select the one subject which most nearly describes the content of your dissertation. Enter the corresponding four-digit code in the spaces provided.

Electronics and Electrical

0544 SUBJECT CODE

#### **Subject Categories**

#### THE HUMANITIES AND SOCIAL SCIENCES

| COMMUNICATIONS AND THE                                                                                  |       |

|---------------------------------------------------------------------------------------------------------|-------|

|                                                                                                         |       |

| Architecture                                                                                            |       |

| Art History                                                                                             | 03//  |

| Cinatro                                                                                                 | 0900  |

| A                                                                                                       | A270  |

| Eng Arts                                                                                                | 0347  |

|                                                                                                         | 0307  |

| intermitation Science                                                                                   | 0/23  |

| Journalism                                                                                              | 0371  |

| Library Science                                                                                         | 0399  |

| Mose Communications                                                                                     | 0708  |

| AAin                                                                                                    | 0413  |

|                                                                                                         | 🔀 🔀   |

| Speech Communication                                                                                    | 0459  |

| Fine Arts Information Science Jeurnalism Library Science Mass Communications Music Speech Communication | 0465  |

|                                                                                                         |       |

| SHACATION                                                                                               |       |

| Consul                                                                                                  | 0616  |

| GE                                                                                                      | 05!3  |

| Administration                                                                                          | 0514  |

| Adult and Continuing                                                                                    | 0516  |

| General Administration Adult and Continuing Agricultural                                                | 0517  |

| A2                                                                                                      | 0273  |

| Art<br>Bilingual and Multicultural                                                                      | 02/3  |

| BININGUES ONG MUSICURUTOS                                                                               | UZOZ  |

| Business                                                                                                | 0688  |

| Community College                                                                                       | 0275  |

| Business Community College Curriculum and Instruction Early Childhood                                   | 0727  |

| End. Children                                                                                           | 0618  |

| garry Childriggs                                                                                        | .0310 |

|                                                                                                         | UJZZ  |

| Finance                                                                                                 | .0277 |

| Finance Guidance and Counseling Health                                                                  | 0519  |

| Handh                                                                                                   | CAACI |

| Higher                                                                                                  | 0745  |

|                                                                                                         | 0/43  |

| History of                                                                                              | 0520  |

| History of                                                                                              | 0278  |

| Industrial                                                                                              | 0521  |

| I amount and Liberature                                                                                 | 0270  |

| Industrial                                                                                              | 02/7  |

| Manufacts                                                                                               | UZOU  |

| Music                                                                                                   | 0522  |

| Music<br>Philosophy of                                                                                  | 0998  |

| Physical                                                                                                | 0523  |

| 11173FAJI                                                                                               | 4323  |

| ·                           |       |

|-----------------------------|-------|

| Psychology                  | 0525  |

| Reading                     | 0535  |

| Religious                   | 0527  |

| Sciences                    | 0714  |

| Secondary                   |       |

| Social Sciences             | 0534  |

| Sociology of                | 0340  |

| Special                     | 0620  |

| echnology                   | 0710  |

| Tests and Measurements      | .0288 |

| Vacational                  | 0747  |

|                             |       |

| LANGUAGE, LITERATURE AND    |       |

| LINGUISTICS                 |       |

| Language                    |       |

| General                     | 0679  |

| Ancient                     |       |

| Linguistics                 |       |

| Modern                      | 0271  |

| General                     | 0401  |

| Classical                   | 0294  |

| Comparative                 | 0295  |

| Medieval                    | 0297  |

| Modern                      | 0298  |

| African                     |       |

| American                    | 0391  |

| Asian<br>Conadian (English) | 0303  |

| Conadian (French)           | 0355  |

| English                     |       |

| Germanic                    |       |

| Latin American              | 0312  |

| Middle Eastern              | 0315  |

| Romance                     | 0313  |

| Slavic and East European    | 0314  |

| THEOLOGY Philosophy                            | 0422         |

|------------------------------------------------|--------------|

| Ratigion General Biblical Studies Clargy       | 0318         |

| Clergy History of                              | 0321         |

| PTHIOSODITY OF                                 | U3Z4         |

| Theology                                       | 0469         |

| SOCIAL SCIENCES American Studies               | 0323         |

|                                                |              |

| Archaeology                                    | 0324         |

| Physical                                       | 0327         |

| Business Administration General                | 0310         |

| General Accounting Banking Monagement Adaption | 0277         |

| Management                                     | 045          |

| Canadian Studies                               | 038          |

| Economics General                              | 0601         |

| Agricultural                                   | 050          |

| Commerce-Business                              | 050:<br>0508 |

| Finance                                        | 0509         |

| Theory                                         | 051          |

| Folklore                                       | 0358         |

| Geography                                      | 035          |

| History<br>General                             | 0578         |

| Ancient                                                                         | A670   |

|---------------------------------------------------------------------------------|--------|

|                                                                                 | 03/ 7  |

| Medieval                                                                        | 0581   |

| Modern                                                                          | 0482   |

|                                                                                 |        |

| Black                                                                           | 0328   |

| African                                                                         | 0331   |

| African                                                                         | .0001  |

| Asia, Australia and Uceanic                                                     | 3 UJJZ |

| Connelica                                                                       | ntt4   |

| European Latin American Middle Eastern United States                            | 2225   |

| <b>Europeon</b>                                                                 | 0333   |

| Latin American                                                                  | . 0334 |

| AA!-JB                                                                          | 0223   |

| Widow Contain                                                                   | .0333  |

| United States                                                                   | 0337   |

| History of Science                                                              | 0505   |

| THISTORY OF SCHEMOS                                                             | . 0363 |

| Law                                                                             | 0398   |

| LawPolitical Science                                                            |        |

| General                                                                         |        |

| General                                                                         | 4013   |

| laterariannal Law and                                                           |        |

| Out-time                                                                        | 0414   |

| _ Kelonons                                                                      | .voio  |

| Relations                                                                       | 0617   |

| Recreation                                                                      | 0014   |

| **************************************                                          | 🕶 :=   |

| Social Work                                                                     | 0452   |

| Coriology                                                                       |        |

| Control                                                                         | 0494   |

| General,, , , ,                                                                 | 0020   |

| Sociology General Criminology and Penalogy Demagraphy Ethnic and Rocial Studies | 0627   |

| Damasana ka                                                                     | 0020   |

| Demography /                                                                    | . 0730 |

| Ethnic and Racial Studies                                                       | 0631   |

| Individual and Family                                                           |        |

| INDIVIDUO CICI FORMIY                                                           |        |

| Studies                                                                         | . 0028 |

| Individual and Family Studies                                                   |        |

| D. A. A.                                                                        | 0/20   |

| Relations<br>Public and Social Welfare                                          | 0629   |

| Public and Social Wellow                                                        | 0630   |

| Social Structure and                                                            |        |

| SOCIOI SITUCIONE ONO                                                            |        |

| Development                                                                     | . 0700 |

| Development                                                                     | 0344   |

| _ ITHEOTY ON O MEMOUS                                                           | . 0344 |

| Transportation                                                                  | 0709   |

| I Irban and Pennagal Planning                                                   | nada   |

| Transportation Urban and Regional Planning                                      | 4777   |

| Women's Studies                                                                 | . U453 |

|                                                                                 |        |

|                                                                                 |        |

# THE SCIENCES AND ENGINEERING

| MOTOEKYT ZCIENCEZ                   |              |

|-------------------------------------|--------------|

| Agriculture<br>General              | 0473         |

| Agronomy                            | 0285         |

| Nutrition                           | 0475         |

| Food Science and                    |              |

| Technology Forestry and Wildlife    | 0359         |

| Plant Culture                       |              |

| Plant Pathology<br>Plant Physiology | 0480         |

| Range Management                    | 0777         |

| Riology                             |              |

| General                             | 0306<br>0287 |

| SIOSTORISTICS                       | 0300         |

| Gel                                 | 0379         |

| Ecology<br>Enternology              | . 0329       |

| Genetics<br>Limnology               | 0369         |

| Microbiology                        | 0410         |

| Moleculor                           | 0317         |

| Oceanography<br>Physiology          | 0416         |

| Radiation                           | 0821         |

| Veterinary Science                  | 0778         |

| Biophysics<br>General               | 0784         |

| Medical                             | 0760         |

| EARTH SCIENCES                      |              |

| Biogeochemistry                     | 0425         |

|                                     |              |

| Geodesy Geology Geophysics Hydrology Mineralogy Paleobotony Paleoscology Paleonology Paleonology Polynology Physical Geography Physical Oceanography | 0372<br>0373<br>0388<br>0411<br>0345<br>0426<br>0418 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                                                                                                      |                                                      |

| HEALTH AND ENVIRONMENTA                                                                                                                              | l                                                    |

| SCIENCES                                                                                                                                             | 07/6                                                 |

| Environmental Sciences                                                                                                                               | U/08                                                 |

| General                                                                                                                                              |                                                      |

| Audiology                                                                                                                                            | 0300                                                 |

| Chemothérapy<br>Dentistry                                                                                                                            | 0547                                                 |

| Education                                                                                                                                            | กรรก                                                 |

| Hospitol Management Human Development Immunology Medicine and Surgery Mental Health                                                                  | . 0769                                               |

| Human Development                                                                                                                                    | 0/36                                                 |

| Medicine and Surgery                                                                                                                                 | .0564                                                |

| Mental Health                                                                                                                                        | 0347                                                 |

| Nuclina                                                                                                                                              | U307                                                 |

| Obstatrics and Gynecology                                                                                                                            | .0380                                                |

| Nutrition Obstetrics and Gynecology Occupation at Health and                                                                                         |                                                      |

| Inergoy                                                                                                                                              | U354                                                 |

| Ophthalmology<br>Pathology                                                                                                                           | 0571                                                 |

| Phormocology                                                                                                                                         | 0419                                                 |

| Phormacy<br>Physical Therapy                                                                                                                         | 0572                                                 |

| Physical Therapy<br>Public Health                                                                                                                    | 0382                                                 |

| Radiology                                                                                                                                            |                                                      |

| Recreation                                                                                                                                           | 0575                                                 |

| Speech Pathology                                                  | .0460<br>.0383<br>0386 |

|-------------------------------------------------------------------|------------------------|

| PHYSICAL SCIENCES                                                 |                        |

| Pure Sciences                                                     |                        |

| Chamistry                                                         |                        |

| Caráni                                                            | 0485                   |

| Agricultural                                                      | 0749<br>0486           |

| Analytical                                                        | 0487                   |

| Inorganic                                                         | 0488                   |

| Nivelage                                                          | 0738                   |

| Organic Pharmacautical Physical Polymer                           | . 0490                 |

| Physical                                                          | 0494                   |

| Polymer                                                           | .0495                  |

| recommendation                                                    | ~ ~ ~                  |

| Mathematics                                                       | 0405                   |

| Physics General                                                   | 0605                   |

| Acoustics                                                         | 0986                   |

| Astronomy and                                                     |                        |

| Astrophysics                                                      | 0606                   |

| Alomic                                                            | 0748                   |

| Atomic<br>Electronics and Electricity<br>Elementary Particles and | 0607                   |

| Elementary Particles and                                          | 0704                   |

| High Energy                                                       | 0/98                   |

| Fluid and Plasma<br>Malecular                                     | 0609                   |

| Nuclear                                                           | 0610                   |

| Optics                                                            | 0752                   |

| Radiation                                                         |                        |

| Statistics                                                        |                        |

|                                                                   |                        |

| Applied Sciences Applied Mechanics                                | 0346                   |

| Computer Science                                                  | 0984                   |

| Footoering                                                                                                                                              |                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Engineering General Aerospace Agricultural Automotive Biomedical Chemical                                                                               | . 0537                 |

| Aerospace                                                                                                                                               | 0538                   |

| Agricultural                                                                                                                                            | 0539                   |

| Riomedical                                                                                                                                              | 0541                   |

| Biomedical<br>Chemical<br>Civil<br>Electronics and Ele                                                                                                  | 0542                   |

| Civil                                                                                                                                                   | 0543                   |

| Electronics and Ele                                                                                                                                     | ctrical . 0544         |

| Heat and Thermad                                                                                                                                        | 9110111C3 U346<br>0545 |

| Industrial                                                                                                                                              | 0546                   |

| Marine                                                                                                                                                  | 0547                   |

| Materials Science                                                                                                                                       | 0794                   |

| Hydroulic<br>Industrial<br>Marine<br>Materials Science<br>Mechanical<br>Metallurgy<br>Mining                                                            | 0743                   |

| Mining                                                                                                                                                  | 0551                   |

| Nuclear                                                                                                                                                 | 0552                   |

| Packaging                                                                                                                                               | 0549                   |

| Socitor and Muni                                                                                                                                        | rind 0554              |

| Metallurgy Mining Nuclear Packaging Petroleum Sanitary and Muni System Science Geotechnology Operations Research Plastics Technology Testile Technology | 0790                   |

| Geotechnology                                                                                                                                           | 0428                   |

| Operations Research                                                                                                                                     | 0796                   |

| Textile Technology                                                                                                                                      | . 0994                 |

|                                                                                                                                                         | 🕶                      |

| PSYCHOLOGY                                                                                                                                              |                        |

| General                                                                                                                                                 | 0621                   |

| Clinical                                                                                                                                                | 0622                   |

| Developmental                                                                                                                                           | 0620                   |

| Experimental                                                                                                                                            | 0623                   |

| Industrial                                                                                                                                              |                        |

| General Behavioral Clinical Developmental Experimental Industrial Personality Physiological Psychobiology Psychobiology Social                          |                        |

| Psychobiology                                                                                                                                           | 0349                   |

| Psychometrics                                                                                                                                           |                        |

| Social                                                                                                                                                  | 0451                   |

The undersigned recommend to the Faculty of Graduate Studies and Research the acceptance of the thesis:

"A Methodology for Analog Circuit Design and Knowledge Transfer."

submitted by Jean-Marc G. Patenaude, P. Eng. in partial fulfillment of the requirements for the degree of Master of Engineering.

Professor Martin unelgrove

Thesis Supervisor

Professor J.S. Wight

Chairman,

Department of Electronics

#### **Abstract**

This thesis describes an attempt to develop an improved methodology for designing analog circuits using the traditional SPICE simulator coupled with Maple<sup>®</sup>, a mathematical programming language with an efficient user interface. The traditional SPICE-based approach to design circuits is examined and its drawbacks are exposed. A better solution is proposed where the circuit design knowledge is developed using symbolic analysis routines programmed in Maple<sup>®</sup>, while it is captured using the executable Maple<sup>®</sup> worksheet interface, thus providing a vehicle for efficient knowledge transfer and reuse by fellow engineers. A C language program provides a link between the Maple<sup>®</sup> engine and Eldo<sup>®</sup>, a SPICE-like circuit simulator. An operational amplifier is designed using the Maple-Eldo prototype tool in the case study section. It is concluded that the tool is useful in increasing the designer's productivity and understanding of the circuit's behaviour, while providing a means to capture and reuse frequency domain circuit design knowledge through the Maple<sup>®</sup> worksheets<sup>1</sup>.

<sup>1.</sup> For simplicity, the registered trademark symbol ® has been omitted in all subsequent references to Eldo and Maple in this thesis.

# Acknowledgements

I would like to express my gratitude to my thesis supervisor, Dr. M. Snelgrove, for his guidance and support during the course of this M. Eng. program.

I would also like to thank my former employer, Bell-Northern Research and Northern Telecom Ltd. - Semiconductor Components Group, in Ottawa, for providing access to their technology, computing resources, and CAD software tools. In particular, I would like to thank my manager, Mr. G. Hupé, for his help and cooperation during the early stages of this thesis. Without this cooperation from my employer and co-workers, none of this research work would have been possible.

In addition, I would like to thank the following individuals:

- Mr. G. Quesnel, for being a mentor and for providing the 'seed' to many ideas in this thesis.

- The late Dr. N. Battersby, for providing inspiration and for being a friend.

- Mr. J. Carette, for his help and guidance in implementing 'good programming practices' in the Maple programming language.

- Ms. D. Hagglund, for providing technical support on Maple related questions.

Finally, I would also like to thank my current employer, LSI Logic Corporation of Canada, for providing access to their computing resources, and for allowing the time off work to complete this thesis.

# TABLE OF CONTENTS

| 1.0 | Intro | ntroduction                                |                                                              |    |  |

|-----|-------|--------------------------------------------|--------------------------------------------------------------|----|--|

|     | 1.1   | Imports                                    | ance of productivity, design quality and predictability      | 2  |  |

|     | 1.2   | Analog                                     | Analog design automation                                     |    |  |

|     |       | 1.2.1                                      | Motivation                                                   | 3  |  |

|     |       | 1.2.2                                      | Analog standard cells                                        | 4  |  |

|     | 1.3   | The pro                                    | posed tool                                                   | 6  |  |

|     |       | 1.3.1                                      | Analog circuit design and reuse using the proposed tool      | 6  |  |

|     | 1.4   | Overvi                                     | ew of the dissertation                                       | 9  |  |

| 2.0 | Over  | view of                                    | Existing Circuit Design Approaches                           | 11 |  |

|     | 2.1   | The tra                                    | ditional SPICE-based approach                                | 11 |  |

|     |       | 2.1.1                                      | The general circuit design flow                              | 12 |  |

|     |       | 2.1.2                                      | Multiple design issues lead to graph complexity              | 14 |  |

|     |       | 2.1.3                                      | Extensive usage of SPICE                                     | 16 |  |

|     |       | 2.1.4                                      | Design knowledge reuse and SPICE                             | 17 |  |

|     | 2.2   | Analog                                     | g circuit design automation                                  | 18 |  |

|     |       | 2.2.1                                      | Analog circuit design knowledge                              | 19 |  |

|     | 2.3   | Overview of the literature                 |                                                              | 22 |  |

|     | 2.4   | Overvi                                     | iew of the literature relating to symbolic analysis          | 27 |  |

| 3.0 | The   | Propose                                    | d Method                                                     | 29 |  |

|     | 3.1   | Goals of the analog design automation tool |                                                              |    |  |

|     | 3.2   | onceptual analog design automation tool    | 31                                                           |    |  |

|     |       | 3.2.1                                      | Generally accepted design practices and methods              | 31 |  |

|     |       | 3.2.2                                      | Important design activities                                  | 32 |  |

|     |       | 3.2.3                                      | Features of the analog design automation tool                | 3  |  |

|     |       | 3.2.4                                      | The power of symbolic and hybrid circuit analysis            | 30 |  |

|     |       | 325                                        | Efficient design space exploration in the transformed domain | 39 |  |

|     | 3.3  | The Ma    | aple-Eldo prototype                                       | 47  |

|-----|------|-----------|-----------------------------------------------------------|-----|

|     |      | 3.3.1     | Maple V and its features for hybrid symbolic analysis     | 47  |

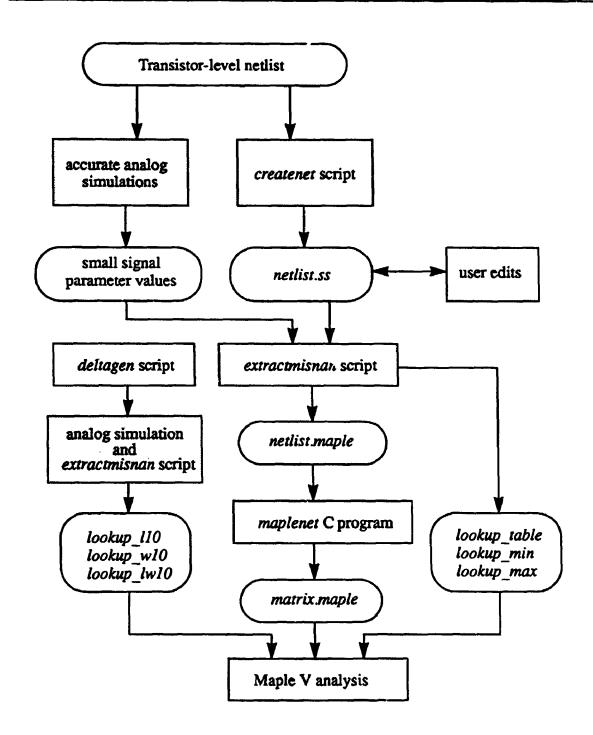

|     |      | 3.3.2     | The design flow using the Maple-Eldo prototype            | 48  |

|     |      | 3.3.3     | Hybrid symbolic analysis in Maple                         | 56  |

|     |      | 3.3.4     | Small signal analysis in Maple                            | 57  |

|     |      | 3.3.5     | Effects of large signal parameters                        | 61  |

|     |      | 3.3.6     | PVIT variations analysis                                  | 65  |

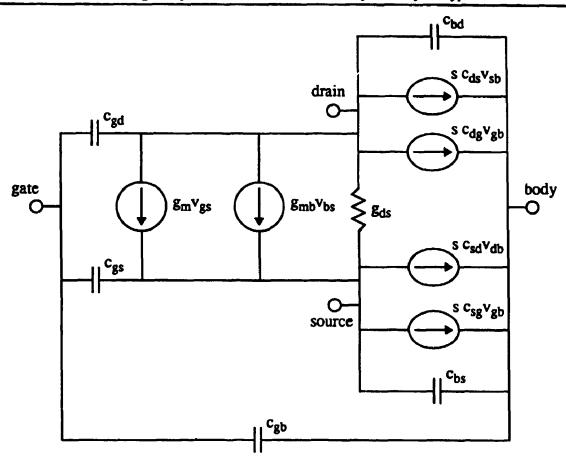

|     |      | 3.3.7     | Small signal modelling issues                             | 68  |

|     |      | 3.3.8     | Knowledge capture using the Maple-Eldo prototype          | 68  |

|     | 3.4  | Using     | the Maple-Eldo prototype                                  | 71  |

|     |      | 3.4.1     | The UNIX scripts and the Maplenet C program               | 71  |

|     |      | 3.4.2     | The Maple smallsignal package                             | 76  |

|     |      | 3.4.3     | The mnasolve routine                                      | 76  |

|     |      | 3.4.4     | The analysis routines                                     | 79  |

|     |      | 3.4.5     | The support routines                                      | 86  |

|     | 3.5  | Autom     | nated verification and design centering using simulations | 87  |

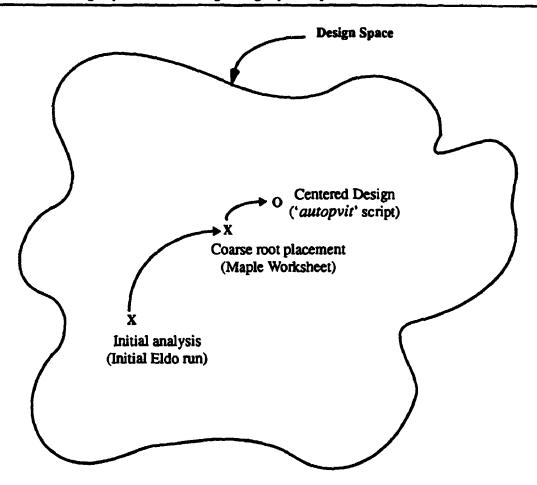

|     |      | 3.5.1     | Design centering and circuit characterization             | 87  |

| 4.0 | Case | Study -   | Amplifier Design                                          | 91  |

|     | 4.1  | Basic t   | two stage operational transconductance amplifier          | 91  |

|     |      | 4.1.1     | Functional Description of the amplifier                   | 92  |

|     |      | 4.1.2     | Initial design effort                                     | 94  |

|     | 4.2  | Design    | of the amplifier using the Maple-Eldo tool                | 100 |

|     |      | 4.2.1     | Maple worksheet for initial analysis                      | 100 |

|     |      | 4.2.2     | Root placement optimization and design centering          | 114 |

|     |      | 4.2.3     | Conclusions                                               | 115 |

| 5.0 | Eval | uations a | and Conclusions                                           | 117 |

|     | 5.1  | Summa     | ary and discussions                                       | 117 |

|     | 5.2  | Recom     | nmendations for future work                               | 119 |

| 6.0 | REF  | ERENC     | ES                                                        | 123 |

|     |      |           |                                                           |     |

| APPENDIX A | Examples of Important Files                | 126 |

|------------|--------------------------------------------|-----|

| A.1        | Transistor-level netlist: 'netlist'        | 126 |

| A.2        | User-modified 'netlist.ss'                 | 126 |

| APPENDIX B | Maple worksheet                            | 130 |

| APPENDIX C | Selected code from the smallsignal package | 150 |

| APPENDIX D | Autopvit system                            | 156 |

# **LIST OF FIGURES**

| Figure 1  | Traversing the design flow graph                                          | 14  |

|-----------|---------------------------------------------------------------------------|-----|

| Figure 2  | Hierarchy of Design Knowledge                                             | 21  |

| Figure 3  | The iterative design flow using a simulator as a verification tool        | 40  |

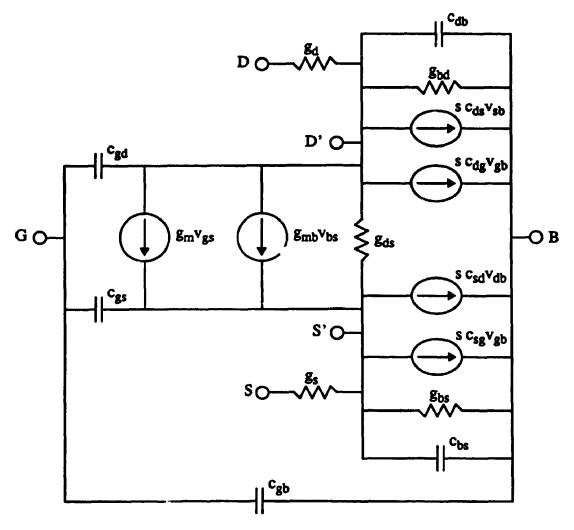

| Figure 4  | The generalized small signal model of the MOS transistor                  | 42  |

| Figure 5  | The iterative design flow with flexible design space exploration          | 45  |

| Figure 6  | First phase of the design flow using the Maple-Eldo prototype             | 49  |

| Figure 7  | Format of the 'lookup_table' file                                         | 52  |

| Figure 8  | The MOS small signal equivalent model used in the Maple-Eldo prototype    | 67  |

| Figure 9  | Circuit design/optimization through design space exploration              | 69  |

| Figure 10 | Format of the 'netlist.ss' file for a MOS transistor instantiation        | 73  |

| Figure 11 | Invoking the 'mnasolve' routine within the Maple worksheet                | 77  |

| Figure 12 | Example of the output produced by the 'reduce_order' routine              | 80  |

| Figure 13 | Example of the output produced by the 'print_sensitivities' routine       | 81  |

| Figure 14 | Output produced by the 'deltagen' routine                                 | 82  |

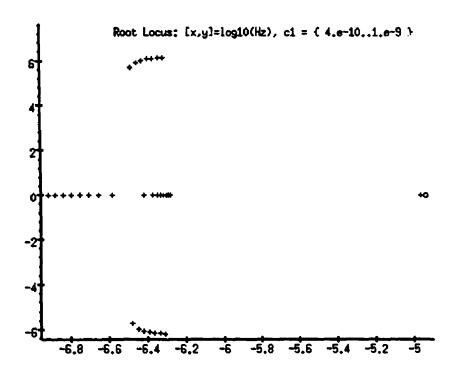

| Figure 15 | Example of the 'rootlocus' plot using the 'inseq' option                  | 85  |

| Figure 16 | Example of the output generated by 'expression_sensitivities'             | 86  |

| Figure 17 | Example of the autopvit.out report file                                   | 90  |

| Figure 18 | Example of a simulation corner case as presented in the 'pvitcases' file  | 90  |

| Figure 19 | Schematic of the two-stage operational amplifier                          | 93  |

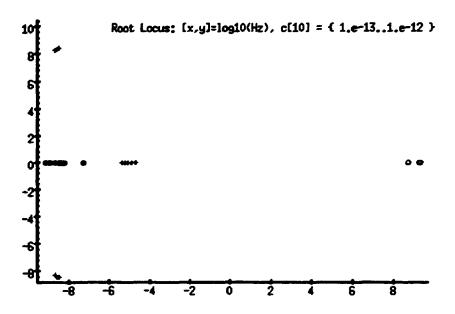

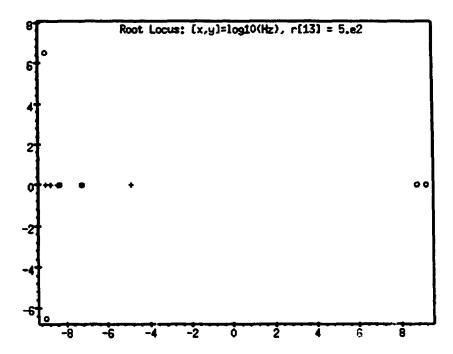

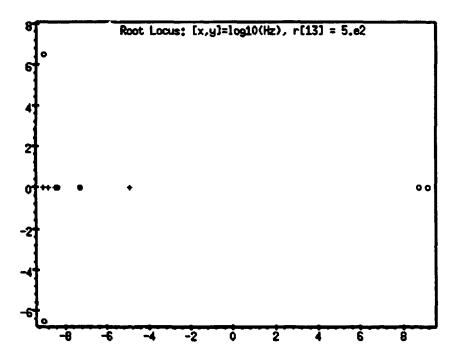

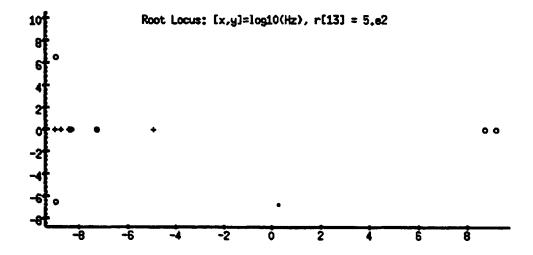

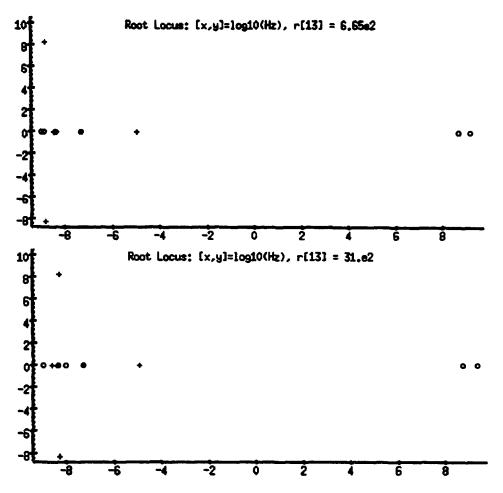

| Figure 20 | Pole splitting effect when c[10] is increased                             | 99  |

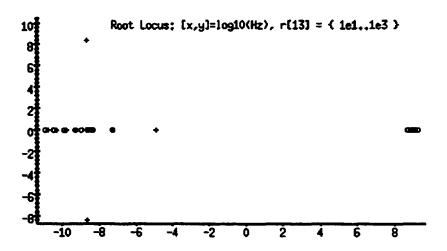

| Figure 21 | Miller zero moving to a lower frequency as r[13] is increased             | 99  |

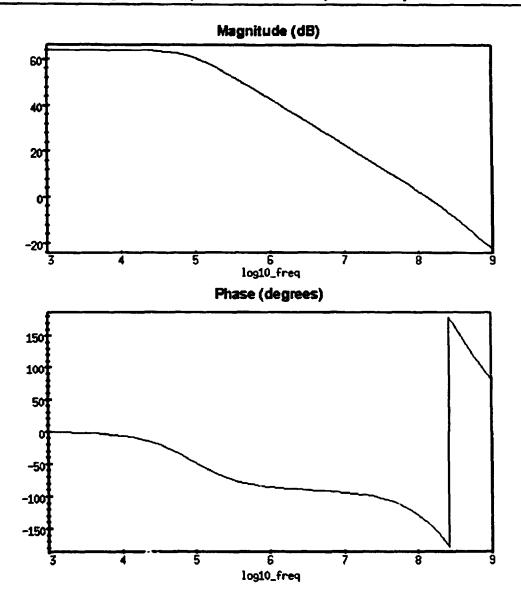

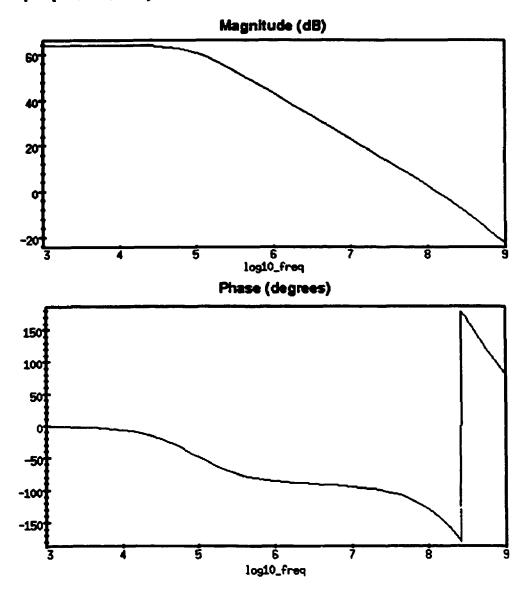

| Figure 22 | Phase and magnitude Bode plots for the initial analysis of the amplifier  | 102 |

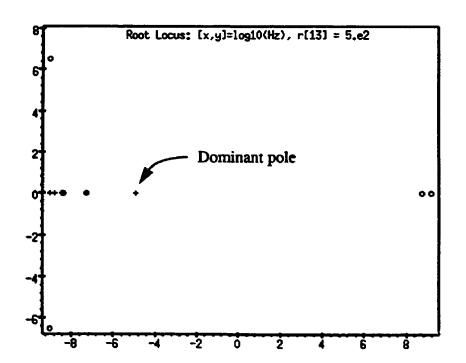

| Figure 23 | Root placement of the amplifier with initial values as shown in Figure 19 | 103 |

| Figure 24 | Root locations                                                            | 104 |

| Figure 25 | Root and DC gain Sensitivities                                            | 104 |

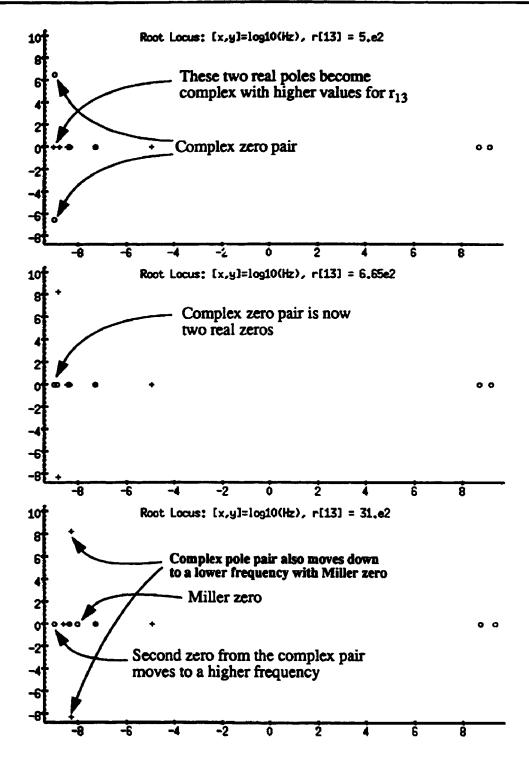

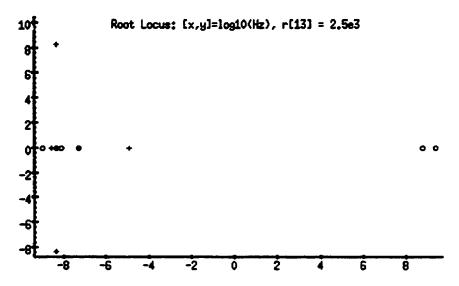

| Figure 26 | Root loci for values of r13 = (500, 665, 3120) Ohms                       | 107 |

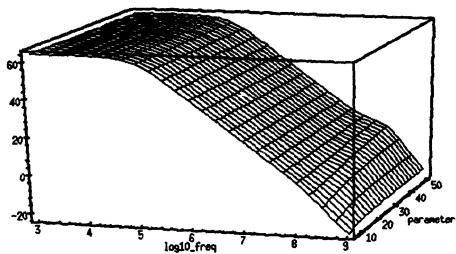

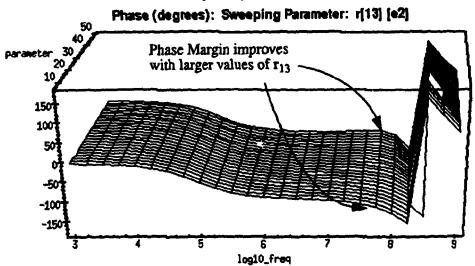

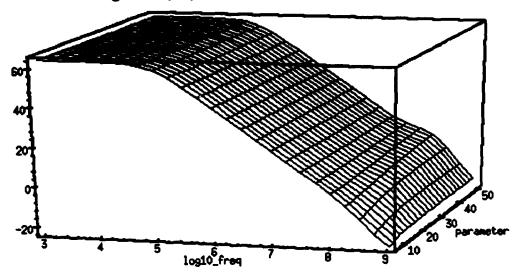

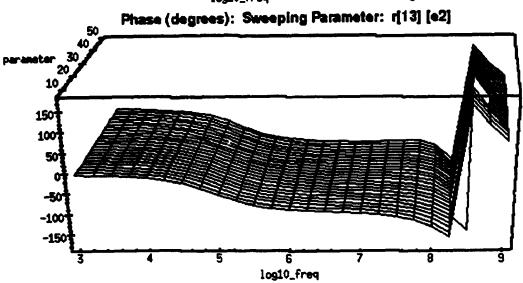

| Figure 27 | Parametric Bode plots. Parameter r[13] = {5005000}                        |     |

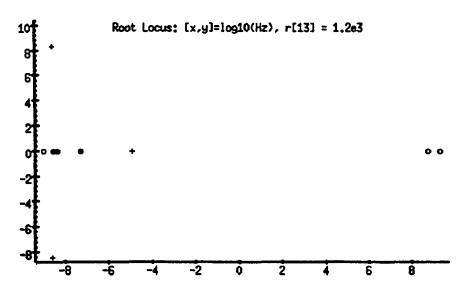

| Figure 28 | Root and DC gain locations and parametric sensitivities for r13 = 1200    |     |

| Figure 29 | Sensitivities to the length and width when r13 = 1200                     |     |

| Figure 30 | Sensitivities to the size (correlated length and width) when r13 = 1200   | 112 |

#### 1.0 Introduction

Although integrated analog circuit design has existed since the invention of the integrated circuit in the early 1970's, today's engineers still design such circuits with the same 'adhoc' approach they used back then. It is clear of course, that many specialized tools have come into existence over the past 20 years to help in the design of specific types of analog circuits. However, when it comes to plain analog circuit design, such as amplifiers, regulators, comparators, and the like, designers tend to rely mostly on their preferred commercial version of SPICE, the analog circuit simulator originally developed at the University of California at Berkeley in the 1960's. An important shortcoming of this approach is that designers find it difficult to explore the design space efficiently because SPICE does not provide any interpretation of the simulated results, nor does it provides any sense of history between a collection of simulation results. The design knowledge is typically developed manually by the designer while being loosely captured in his engineering notebook. This can impair the engineer's productivity and can result in increased costs and slower timeto-market for the corporation. This thesis is an attempt to improve this situation using a more systematic approach to design analog circuits in the frequency domain than the currently used 'ad-hoc' method using SPICE alone. The methodology integrates a SPICElike simulator with a mathematical analysis tool and a worksheet user interface, thus making self-documentation possible during design and engineering trade off analysis. The implementation is a proof-of-concept tool constructed by writing code to combine the worksheet and analysis functions of one piece of commercial software (Maple) with the accurate MOS gransistor models (Northern Telecom's MISNAN) and the numerical circuit simulation capabilities of another (Eldo). It is demonstrated for frequency domain analysis only, for a typical industrial design problem. A full commercial implementation would integrate the function in a single tool with improved numerical and symbolic analysis algorithms.

# 1.1 Importance of productivity, design quality and predictability

Increasing competition in today's semiconductor marketplace is forcing corporations to find better ways to improve designer's productivity, circuit design quality, and predictability in their product development cycles. The relevance of each of these aspects cannot be overstated [1]. A more productive designer can turn out a product using less resources and design lead time, which translate into higher corporate profits through the early acquisition of a larger market share. A better quality product can lead to higher performance than its competitor's offerings. In terms of correctness, a better quality product can translate into substantial savings in costs required to fix design errors, and in loss of time and reputation caused by the mistakes. Further, more predictable design lead time and product performance can lead to more accurate product, project and schedule planning, and can provide substantial leverage for timely product introduction into the marketplace and for enhancement of the corporate image. Finally, predictability can also help reduce the technical risks inherent in a technical design project, since early and accurate product performance assessments can provide the information necessary to properly evaluate the product's requirements, and its technical feasibility.

# 1.2 Analog design automation

#### 1.2.1 Motivation

With the ASIC revolution of the mid-1980's, the previously held view in the industry where most relevant analog functions would be replaced by some digital equivalent has changed [2]. It is true indeed, that much of the traditional analog functionality has since been implemented in the digital domain, but at the same time, a higher on-chip complexity and integration level, combined with the need for higher performance, often implied that chips must be mixed-signal in their nature. With the current drive for even higher levels of integration, and with more consumer applications requiring complex analog human interfaces, it is reasonable to expect that this trend will at the very least sustain itself, if not make mixed-signal ASICs a much sought-after commodity in the near future.

This widely held view of the late 1970's and early 1980's pushed the digital circuit design community to efficiently address its need for design automation. Design methodologies which included row-based layout from standard cell libraries [3], semi-custom place and route [4], and logic synthesis with technology mapping [5] have been developed, and provided a relatively clear and reliable path for the designer to map functional ideas into a working silicon solution. At the same time, however, the success of the digital circuit design world made it more obvious that the analog circuit design community had a serious lack of comparable semi-custom and full-custom design tools.

Hence, the growing presence of analog functions on mixed-signal integrated circuits, combined with the ever increasing market pressure to decrease the design time for new mixedsignal ASICs, are currently forcing industry and academy to address and resolve a range of challenging problems in the analog design automation world. The goal is to try to improve the designer's productivity, while ensuring a high standard for design quality and circuit performance. The improved predictability can play a key role in the corporation as it can help designers, their management, and other key corporate functions such as product line management and marketing, in their effort to better plan their resource utilization and to assess more accurately a timely introduction of the product into the marketplace.

#### 1.2.2 Analog standard cells

Since digital standard cells have proven to be robust and universally useful in the digital circuit design world, one would be led to believe that similar results could be obtained with analog standard cell libraries. Although analog standard cells can be proven to be useful, reused cells often require further customized sections, due to certain performance specifications particular to a given mixed-signal ASIC project. In general, a mixed-signal ASIC can be expected to find 70%-90% of its analog cells in a good library [2]. However, the additional design effort required to develop the much-needed custom analog cells can have an enormous impact on a project with short time-to-market constraints, especially when the custom analog circuits are pushing the limits of the process technology in terms of performance. Moreover, developing a good analog standard cell library can be very time consuming, given the relatively large pool of different types of analog circuits required in mixed-signal ASIC design projects. The amount of effort underlying the full development of an analog standard cell library is further compounded by the accelerated evolution of process technologies, and by the business need of corporations to provide sec-

ond and third sourcing of their silicon products into silicon facilities with slightly different process parameters.

The challenges posed by analog standard cell libraries are therefore much greater than their digital counterparts. The production volumes, or usage, of analog standard cells are generally much less than the usage of a digital standard cell library, given that most of today's ASICs are completely digital. Further, the effort required to develop a useful analog cell library is greater than for a digital cell library, given that each analog cell tends to have more complexity than a basic digital gate. It is also likely that a good analog cell library will have a larger number of cells than a comparable digital cell library, thus compounding the effort required for its development. Finally, the need for customized sections of analog cells on a per project basis reduces even further the payback expected from the full development of a complete analog standard cell library.

The above arguments provide a basis for contemplating a different approach than a full standard cell library for increasing analog circuit design productivity while minimizing costs. Although there is always a need for some kind of analog cell library, for such basic cells as generic operational amplifiers, comparators, and the like, there is still a need for productivity improvement in the way analog circuit designers develop custom analog cells. The goal of analog circuit design automation is to address this issue by providing a tool box and by suggesting a method which will make the analog circuit designer more productive, and less prone to design errors, or to uncovered but yet important design issues.

## 1.3 The proposed tool

At present analog circuit design involves a great deal of duplication of effort, with designers almost repeating one another's work (or earlier efforts of their own) on particular types of circuits. This problem has proven difficult to solve because of the diversity of issues pertaining to analog circuit design.

An analog designer typically alternates between hand symbolic analysis, which makes for a thorough understanding of simplified circuit models, and numeric simulations, which is used to verify that the simplifications required during hand analysis are warranted. She also keeps a written record of design decisions, so as to be able to review the overall progress as the knowledge is developed. The tool proposed integrates these three key elements - workbook, analysis and simulations - in a single tool.

This strategy is desirable to the designer because it provides for a proven and familiar design methodology. It is preferable to the existing method, even for a single design, because automating and integrating symbolic analysis allows the use of higher order models and faster analysis cycles, and rapid exploitation of such 'textbook' tools as root locus plots, for example. It is even better when designs must be revisited at a later date because of the inclusion of the workbook aspect in the tool, which provides a vehicle for knowledge capture and transfer.

# 1.3.1 Analog circuit design and reuse using the proposed tool

Many useful tools exist in the marketplace to help the designer achieve a specific goal very efficiently. Signal processing analysis tools such as Matlab® or Comdisco®, for example,

allow the designer to analyze and understand the theory behind filters and data converters. At the level of circuit design, however, the SPICE circuit simulator is probably the most commonly used circuit verification tool used by the analog circuit design community. Since simulation fills such a fundamental need in circuit design verification, most analog design tool vendors provide their own version of the SPICE simulator, integrated within their own framework for waveform display, design capture, and physical layout capture and verification.

One common problem with simulators is that they display the resulting response of a circuit without providing much information about how the circuit operates, or why it behaves in a particular manner under certain conditions. As a consequence, simulators alone provide little insight on how to improve the performance of a given circuit. Designers thus rely on observation, hand analyses, experience, and the like in order to better understand the operation of the circuit. It is only after a good grasp of the fundamentals of the circuit that a designer can try to modify and optimize the circuit for a particular set of specifications. The effort and time required to obtain this 'design knowledge' is often very substantial, and thus costly to the corporation in terms of funding and missed opportunities due to a longer time-to-market. Hence, productivity and quality become a mutual trade off in the business, because the view is often one where engineers are forced to be less thorough in their analyses in order to stay on track with an aggressive schedule. A side result of this is often an impaired predictability, where designs often fail in the latter stage of the design cycle due to unforeseen problems.

One way to address the problem of circuit knowledge development and reuse is by means of integrating accurate SPICE simulations with the concept of symbolic analysis and the idea of an executable worksheet user interface. The term symbolic analysis implies that the circuit under investigation is described in terms of algebraic equations. The results of the SPICE simulations are needed in order to analyze the circuit under realistic operating conditions. Thus, all the information describing the electrical behavior of the circuit should be contained within this set of accurate algebraic equations, and the table of accurate symbolic parameter values provided by the SPICE simulations. From a circuit design knowledge point of view, the issue is to extract the relevant design information from these equations, and to present it to the designer in a way that allows her to fully understand the important design considerations and trade-offs. Moreover, these equations can be analyzed and pasted into some form of computerized document, or 'worksheet'. This executable worksheet interface can be used to keep track of the design information as it is developed, so that it can be easily transferred to another engineer at a later time, thus addressing the need for knowledge transfer and reuse. One limitation to this approach is that the resulting equations must be simple enough to be manageable and understandable by the designer. Another limitation is that only closed-form analytic equations can be made easily manageable and, in general, such closed-form analytic equations do not exist for all type of analog circuit analyses. In particular, time-domain circuit analyses generally involve implicit equations which can only be solved through iterative methods. On the other hand, when a circuit is linearized at a given operating point, a set of closed-form equations always results. Symbolic analysis then applies particularly well to this special case, and can therefore be used to perform small signal DC and frequency analysis of electronic circuits. A

DC operating point simulation can be performed with SPICE to obtain an accurate table of symbolic parameter values for numeric substitutions, as may be required by graphics or simplification of the resulting symbolic expression.

#### 1.4 Overview of the dissertation

The value of the prototype tool is demonstrated by using it for a typical industrial design problem: The design of a two-stage MOS operational amplifier, optimized for fast settling. This is a problem addressed in general terms by many textbooks and tutorial papers [24][27][28][29]. Textbook models are simplified, however, so they provide little more than a starting point, especially for high performance designs, which occurs frequently in the industry. In such circuits, the important design knowledge involves multiple trade-offs between second-order effects which are unfortunately rarely discussed in the literature. The case study demonstrates how the proposed tool can be used to accurately and efficiently explore an amplifier's frequency domain performance, and its applicable design space. In particular, it is shown how a designer can easily and quickly understand the trade-offs between important second order effects affecting the amplifier's stability. A Maple worksheet capturing this design effort has been developed and is discussed in the case study section of this thesis. Furthermore, a set of UNIX scripts have been written to characterize and tabulate the frequency domain performance of the amplifier over relevant simulation corners. This script was written in a format that is generic enough to characterize the circuit over any relevant corner as dictated by the application. This programmability is an important aspect, as amplifiers require different sets of simulation corners than voltage regulators, for example.

The limitations of existing popular tools such as SPICE are examined in details in chapter 2, with the goal of developing an improved method. In chapter 3, symbolic analysis using the Maple V software package is introduced since it provides an efficient tool to develop the routines necessary to perform the required mathematical analysis addressing the special case of small signal analysis and design. Symbolic analysis is used in this context as a circuit design tool, helping the designer to gain insight into the circuit studied, while the Maple V interface provides a platform to capture, reuse and transfer the circuit design knowledge developed through the executable worksheet interface. The recommended methodology is then implemented in a prototype which integrates the Maple V package with Eldo, a SPICE-like circuit simulator. The case study is presented in chapter 4, whereas the value of the tool is evaluated in chapter 5. Conclusions and recommendations for future work are also exposed in this chapter.

# 2.0 Overview of Existing Circuit Design Approaches

The art of analog and mixed-signal ASIC design is generally not considered to be a trivial task. Since each circuit design project has its own set of design issues, there is, generally speaking, no single optimal and complete design solution yielding the absolute best circuit performance and robustness. As a consequence, designers tend to approach each particular design problem in their very own ways, which makes it very difficult for anyone to draw general conclusions aiming at providing a definition of the exact best design methodology.

In a practical sense, methodologies depend upon a designer's experience, the circuit topology considered, the set of design specifications, and the environmental operating conditions. Hence, a detailed discussion about any given state of the art design approach is deemed futile, as no general conclusions could be drawn from such details.

Instead, it shall be considered appropriate to consider the more general design flow, skipping the project-specific details, in order to help define relatively accurately the thoughts and design practices experienced by the designer during the design process. Although an imperfect generalization, this approach should provide enough information for proper guidance towards the development of a useful analog circuit design and reuse methodology.

# 2.1 The traditional SPICE-based approach

One of the first step typically performed by an analog circuit designer is to define the analog functions of the mixed-signal integrated circuit as seen from the system's perspective. This phase alone can require substantial efforts from the designer's part, as the underlying product requirements are better understood. Although this is clearly an area where an im-

provement in efficiency is important and possible, this thesis will not try to address that phase of the design challenge.

#### 2.1.1 The general circuit design flow

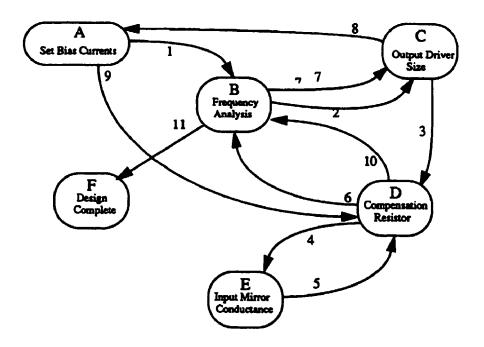

The SPICE simulator is normally used extensively at the circuit block level. In general, designers tend to iterate several times as they weave through the numerous design possibilities. They may choose to make specific design decisions based on certain assumptions, which they may later try to validate. Care is taken in making assumptions which are realistic and result in a reasonable 'hand solution'. The designer may also choose to limit the number of degrees of freedom in his design because some validations need to be performed by manual and possibly tedious analytic methods. The design process can therefore be seen as traversing a complex and fluid design decision graph, where numerous iterations can occur around each node. Figure 1 on page 14 provides an abstract illustration of such a design decision graph, and its traversal by the circuit designer.

Consider each node in the graph to represent a design activity, whether a design decision, an analysis, or an assumption. Each directed line in the graph represents the time sequence upon which each node is invoked. Thus, the designer may start by making an assumption at node A. For the purpose of this discussion consider the design of an amplifier. The assumption at node A corresponds to fixing the input and output stage bias currents, possibly based upon the minimum slew rate the designer needs while assuming a 1 pF compensation capacitor between the first and second stage. As the designer progresses through her design, she will move to node B (step 1), which corresponds to performing a frequency analysis of her amplifier, and then to node C (step 2), which corresponds to resizing the

second stage output driver transistor. She will then move on to consider other issues, such as the value of the compensation resistor and the output conductance of the input stage current mirrors, which corresponds respectively to nodes D and E (step 3 and 4). She may then decide to go back to node D (step 5) before she chooses to perform another frequency analysis at node B (step 6). This may lead her to reconsider the size of the output drivers at node C (step 7), or even to come back to her original bias current assumptions at node A (step 8). She might have discovered that the 1pF compensation capacitor is too small for what she is trying to achieve, and thus, by increasing the compensation capacitor, she might be forced to also increase the bias current in order to maintain a proper slew rate. Eventually, at node F (step 11), she will reach a point where she feels that the design is reasonably optimal for her application. The point of this graph is that it provides a simplified representation of the activities of the designer as a function of time. Since the designer always re-evaluates the complete design at any step in the design graph (at any node), it is therefore clear that predicting how the designer inter-relates each of these activities is both futile and useless, because it depends on too many factors. Depending upon the set of specifications, the technology, the circuit topology, and many other factors, the preferred design procedure pursued by a particular designer will vary substantially between each case.

It is important to recognize that the designer needs and wants the ability to traverse the design space with maximum flexibility. This is a fundamental requirement of the analog circuit design process. As each designer has his own way of approaching a design problem, and as each circuit structure has its own set of relevant design issues, it is reasonable to assume that the design flow graph for any particular design problem will very rarely be iden-

tical, if ever. It follows that flexibility constitutes a fundamental feature required by any successful and useful analog circuit design and reuse method. Stated differently, the user needs the ability to specify his own design decision graph as he explores and understand the circuit's design space. A hard-coded expert would therefore defeat this purpose. This is a very important aspect of design which is traditionally served well via the engineer's workbook.

Figure 1 Traversing the design flow graph

# 2.1.2 Multiple design issues lead to graph complexity

It is now evident that the design flow graph of a typical circuit is normally very complex and difficult to predict as the designer needs to re-evaluate the entire circuit after each design consideration. To make matters worse, many design issues are addressed several times within the graph, as part of multiple iterative loops. It is important to realize why this is the case. The short answer to this question is that there are a large set of unknowns to consider simultaneously during the design of the circuit. For example, there are, in a typical circuit, relationships trading off all of the following design issues, as well as many other considerations:

- power consumption

- bias currents

- operating voltages

- loop stability

- process variations of all active and passive devices

- operating conditions such as environmental noise coupling

- noise coupling/rejection from nearby circuits

- mismatch effects over process variations

- · environmental conditions such as temperature

- block size, and other cost-related issues

- manufacturing and parametric yield issues

- non-ideal (non-linear) effects of linear devices (resistors, capacitors)

- parasitic capacitances of large resistors

- non-ideal and parasitic effects of active devices

- production testing issues

- digital noise coupling through the substrate

- etc, etc, etc...

In general, most of these effects, including their absolute and relative variations, must be considered simultaneously during the design process in order to build the required robustness into the circuit block. Since it is impossible to address all issues at once, designers tend to start with a set of assumptions, usually taken from experience, and make their best

effort to understand the circuit. The local iterative loops are thus required as the designer often needs to re-validate or modify a previous design as imption. Through such iterative looping at various levels, the designer eventually reaches a consensus point where she believes that the circuit has the required robustness, and is well optimized for the targeted application. In summary, there is therefore no point in trying to find a simple enough model to automate the design process. The circuit design activities clearly need to be designer driven. A useful method therefore needs to encapsulate this flexibility.

#### 2.1.3 Extensive usage of SPICE

Since there are so many design issues to consider simultaneously, designers tend to make certain assumptions, followed by the verification of these assumptions through simulations using SPICE. By constantly alternating between circuit modifications and simulations, the designer tests his assumptions, and eventually moves closer to the region where the design will be considered as complete and optimal. At this juncture, one must realize the intent of the SPICE simulator. Since it only simulates the behaviour of a circuit under the conditions specified by the designer, it provides a means for verification, and as such, it is not a design tool, in the sense that a design tool ought to tell the designer how and why a circuit behaves in a particular manner. But because such true circuit design tools do not exist in the marketplace, designers end up using SPICE more extensively than they ought to. In particular, designers often use SPICE to collect a series of plots and graphs, where the circuit has been exercised under slightly different conditions. By studying these observations, the designer tries to understand what is happening within the circuit. By coupling these observations with theories and empirically observed phenomena, the designer tries

true, is often not obtained without extensive efforts since many simulations are required, and the links between theory and SPICE observations are not always obvious. In fact, it is often very difficult to correlate the observations to the theory, because the links are very complex and may involve many parameters. The major problem in this case is not so much the time required to accumulate the plots through multiple simulations, but rather the fact that SPICE does not provide any direct insight in how or why the circuit works. Again, one must realize that this was not the intent of SPICE, as it was originally intended to be used as a design verification tool by providing simulation results.

#### 2.1.4 Design knowledge reuse and SPICE

Since SPICE was never intended to be a true circuit design tool, in the sense of telling the designer why or how the circuit works, it follows that it is not the best vehicle to capture and later reuse the resulting design knowledge. Most of the design knowledge is in the designer's mind, and SPICE simply generates plots at each simulation run, for analysis by the designer. Moreover, SPICE does not provide any sense of history, whereas design knowledge in the designer's mind evolves with time. From a design knowledge development, capture and reuse point of view, SPICE is very much incomplete. A framework which focuses on developing and capturing the design knowledge as it is learned by the designer would be more appropriate. This framework, which could be in the form of an executable document or a worksheet, could be read, understood and executed by another designer, thus providing a means upon which the design knowledge is stored, reused and transferred to another designer. Clearly, SPICE does not provide any such facility. Howev-

er, since design verification forms an integral part of the design cycle, it remains imperative to hook up SPICE into such a framework in order to have a tool that is complete in the sense that it can help the designer during both the design and circuit verification phases.

#### 2.2 Analog circuit design automation

The analog circuit design and reuse challenge is really a subset of the larger analog circuit design automation problem. Since all aspects of analog design automation are inter-related, it is important to understand what are the basic elements upon which analog circuit design automation is based. In general, it can be divided into three lines of design effort: Synthesis, analysis and verification. Synthesis comprises the effort required to create circuit topologies and to size their devices, as well as the development of a set of system specification and its practical implementation. Synthesis efforts include both layout synthesis and circuit synthesis. Analysis, on the other hand, is normally done using analytic equations or empirical rules in order to predict the behavior of the circuit or the layout. Finally, verification is typically done via simulations, thus providing information to the designer regarding the functionality and robustness of the circuit. These three important tasks are normally tightly intermingled during the design flow, with iterations at all levels. As the designer learns more about the circuit topology using the feedback provided by analytical and verification tools, he can then feed this more accurate information back into the synthesis task. A good design tool should therefore provide the openness and the flexibility to let the designer interact at all levels within the design flow, and therefore influence the direction of the analysis, synthesis, and verification efforts.

#### 2.2.1 Analog circuit design knowledge

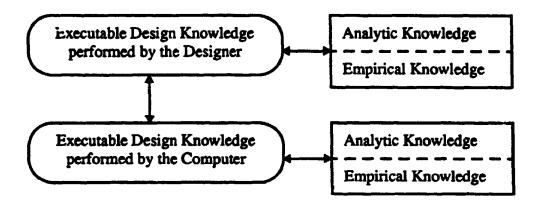

Before trying to address the issue of analog design automation more completely, the nature of analog circuit design knowledge needs to be defined. In essence, this can roughly be divided into three different categories:

- 1. Analytic design knowledge

- 2. Empirical design knowledge

- 3. Executable design knowledge

The analytic design knowledge usually takes the form of design equations modelling various aspects of a circuit's behavior. For instance, the small signal model of an active device can be regarded as analytic design knowledge. Similarly, large signal design equations, distortion or noise equations, as well as the approaches or procedures followed by the designer to analyze simulation results can all be considered as analytic design knowledge. In general, analytic design knowledge is anything that can be thought of as helping the designer directly analyze a certain physical behavior of the analog circuit.

Empirical design knowledge effectively complements the analytic design knowledge pool of information. It includes any observations or rules-of-thumb that a designer may be using to help in the analysis of a circuit. For example, a designer may start a design by fixing the channel length of certain MOS current sources to a given value, because from her experience, such a channel length has been proven to be adequate in her application. Similarly, a design procedure could be entirely empirical, where a designer starts by tackling a particular aspect of the circuit, because that allows her to freeze many parameters and start analyzing the circuit analytically or empirically at some operating point. In general, em-

pirical design knowledge can be seen as any form of design knowledge which is mostly based on experience or observations, and for which no complete physical analytic understanding has been sought, achieved, or deemed necessary.