# Characterization and Digital Correction of Multi-Stage Analog-to-Digital Converters

by

### **Dragos Cartina**

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Masters of Engineering

Ottawa-Carleton Institute for Electrical Engineering

Department of Electronics

Faculty of Engineering

Carleton University

Ottawa, Canada

© Dragos Cartina, 1997

# The undersigned recommend to the Faculty of Graduate Studies and Research acceptance of the thesis

"Characterization and Digital Correction of Multi-Stage

Analog-to-Digital Converters"

submitted by Dragos Cartina (B.Eng.) in partial fulfillment of the requirements for the degree of Master of Engineering

Chairman, Department of Electronics Professor Jim Wight

> Thesis Supervisor Professor Martin Snelgrove

> > Carleton University

> > December 10, 1997

# **Abstract**

Multi-stage analog-to-digital converters are the dominant choice in applications that require both high speed and high accuracy, such as video and wideband radio.

Existing characterization methods only provide information about the performance of the ADCs at the system level, and therefore offer little insight into the causes of nonlinearity. In this thesis we propose a method geared specifically toward multi-stage architectures that can characterize the internal blocks and estimate the differential nonlinearity (DNL) and the integral nonlinearity (INL) of the A/D and D/A subconverters, and the gain of the inter-stage amplifiers. This method has been applied to a two-stage ADC and a pipeline ADC.

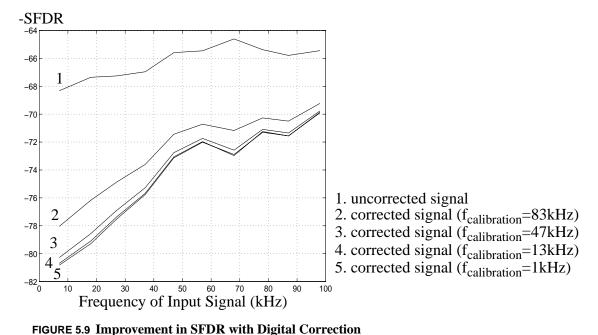

An adaptive on-line digital correction algorithm derived from the characterization method is also presented. A pipeline ADC was designed to test this algorithm, and digital correction resulted in an improvement of the Spurious-Free Dynamic Range by 6dB over three quarters of the bandwidth.

# Acknowledgments

The two years I spent working on my M.Eng. thesis have been a great experience and changed my life in many (positive) ways.

All this has been possible thanks to Martin Snelgrove who supported and guided me all along, and provided me with excellent ideas and solutions. I am heavily indebted to him.

Many thanks to Phil Lauzon for designing my test boards, to Alana Wirta for helping me with the paperwork, and to the other people in the lab for the many times they answered my questions and gave me good advice.

I am very grateful to Timo Rahkonen and Antti Mantyniemi from the University of Oulu for helping me design my first chip. Also thanks to Analog Devices for providing us with several of their chips.

Finally, I would like to express my gratitude to my parents and sister for their love, support, and understanding.

# Table of Contents

| Abstract       |                                                | iii        |

|----------------|------------------------------------------------|------------|

| Acknowledgme   | ents                                           | $\dots iv$ |

| Glossary of Te | rms                                            | ix         |

| CHAPTER 1      | Introduction                                   | 1          |

|                | Motivation                                     |            |

| CHAPTER 2      | Two-Stage A/D Converter Architecture           | 5          |

|                | Introduction                                   | 5          |

|                | Range Overlap and Digital Correction           |            |

|                | Sources of Nonlinearity in a Two-Stage ADC     |            |

|                | Residue Modeling                               | 11         |

|                | Residue Bounds                                 | 14         |

|                | A/D Subconverter Architecture                  | 17         |

|                | Summary                                        | 22         |

| CHAPTER 3      | Characterization of Two-Stage A/D Converters . | 24         |

|                | Definition of ADC Specifications               | 24         |

|                | Prior Art of ADC Characterization              |            |

|                | Bidimensional Code Density Tables              | 29         |

|                | Columns of the Bidimensional Histogram         | 33         |

|                | Fine A/D Subconverter Characterization         | 35         |

|                | Histogram Smoothing                            | 42         |

|                | Bound Estimation                               | 45         |

|                | Component Characterization                     |            |

|                | Discussion of Characterization Method          | 51         |

|                | Summary                                        | 56         |

|                |                                                |            |

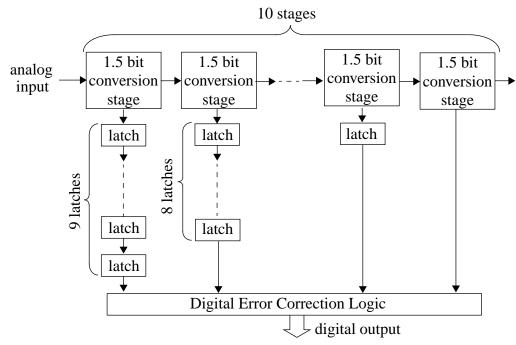

| CHAPTER 4  | Pipeline ADC Architecture57                                                                 |

|------------|---------------------------------------------------------------------------------------------|

|            | Introduction                                                                                |

|            | 1.5-Bit Conversion Stage                                                                    |

|            | Residue Modeling for Partition 1/1364                                                       |

|            | Residue Modeling for Partition 2/12                                                         |

|            | Summary                                                                                     |

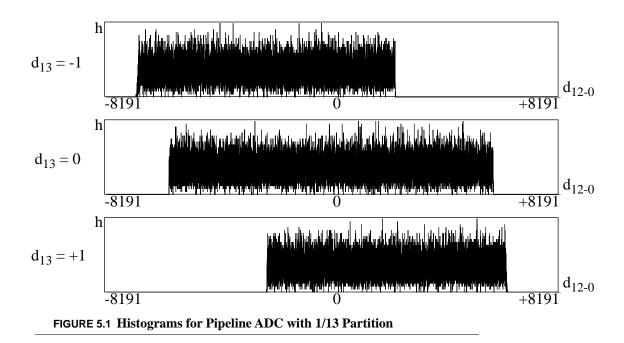

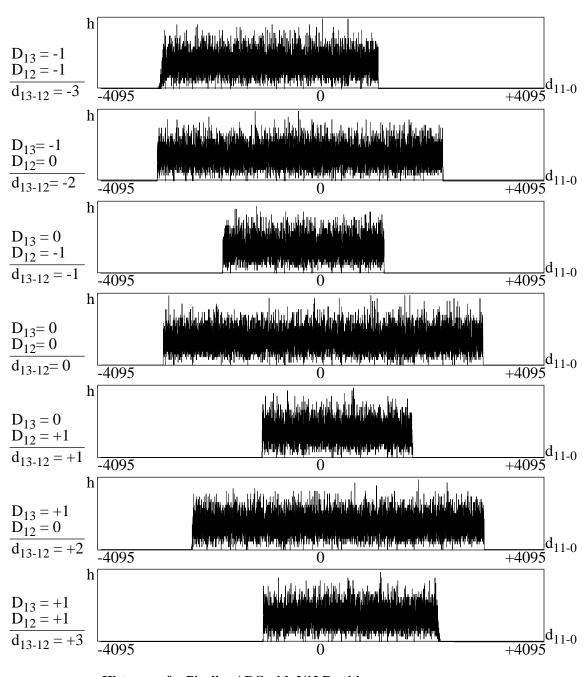

| CHAPTER 5  | Characterizatio <b>n</b> n <b>D</b> igitaCorrectionffipelin <b>&amp;/IC</b> onverters<br>73 |

|            | Histograms for Pipeline ADC                                                                 |

|            | Bound Estimation76                                                                          |

|            | Component Characterization81                                                                |

|            | Discussion of Characterization Method84                                                     |

|            | Prior Art of Digital Correction87                                                           |

|            | Adaptive Digital Correction89                                                               |

|            | Discussion of Correction Method95                                                           |

|            | Summary97                                                                                   |

| CHAPTER 6  | Contributions and Future Work98                                                             |

|            | Contributions of Research                                                                   |

| References | 107                                                                                         |

# List of Figures

| FIGURE 2.2  | Residue as the Difference Between Input and Quantized Input, Amplified by A2 | 7  |

|-------------|------------------------------------------------------------------------------|----|

| FIGURE 2.3  | Residue for Ideal and Nonideal Case                                          |    |

| FIGURE 2.4  | Simplified Block Diagram of the AD9042                                       |    |

| FIGURE 2.5  | Effect of Nonidealities on Residue                                           |    |

| FIGURE 2.6  | Effect of Nonidealities on ADC Characteristic                                |    |

| FIGURE 2.7  | Lower and Upper Bounds of the Residue                                        | 15 |

| FIGURE 2.8  | Coarse ADC Architecture                                                      |    |

| FIGURE 2.9  | Effect of Mismatches                                                         | 21 |

| FIGURE 2.10 | Typical Flash Architecture                                                   | 23 |

| FIGURE 3.2  | Set-Up for the FFT, Sine-Fitting, and Code Density Tests                     | 27 |

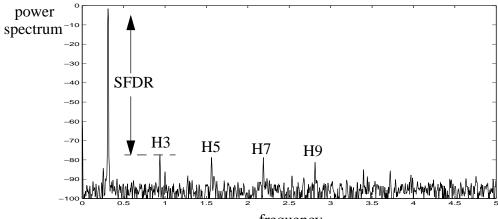

| FIGURE 3.3  | Power Spectrum of ADC Output for a Sinusoidal Input                          | 27 |

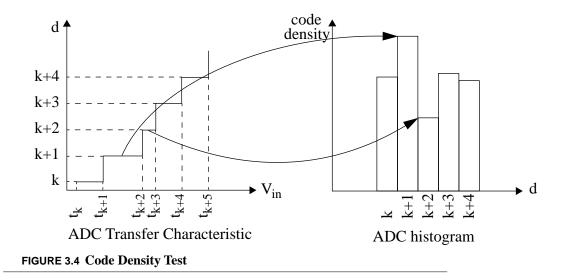

| FIGURE 3.4  | Code Density Test                                                            | 28 |

| FIGURE 3.5  | Bidimensional Histogram                                                      | 30 |

| FIGURE 3.6  | Residue Plot                                                                 | 31 |

| FIGURE 3.7  | Code density for $d_1 = 3$ and $d_2$ from 0 to 127                           | 31 |

| FIGURE 3.8  | Relationship between Uni- and Bidimensional Histograms                       | 32 |

| FIGURE 3.9  | Relationship between Residue Sections and Histogram Columns                  | 33 |

| FIGURE 3.10 | Histogram Columns in Real and Ideal ADC                                      | 34 |

| FIGURE 3.11 | Overlapped Columns of Bidimensional Histogram (Uniform pdf)                  | 37 |

| FIGURE 3.12 | Overlapped Columns of Bidimensional Histogram (Nonuniform pdf 37             | f) |

| FIGURE 3.13 | Symmetries and Asymmetries in the Reference Histogram                        | 38 |

| FIGURE 3.14 | Full-Scale Reference Histogram                                               | 39 |

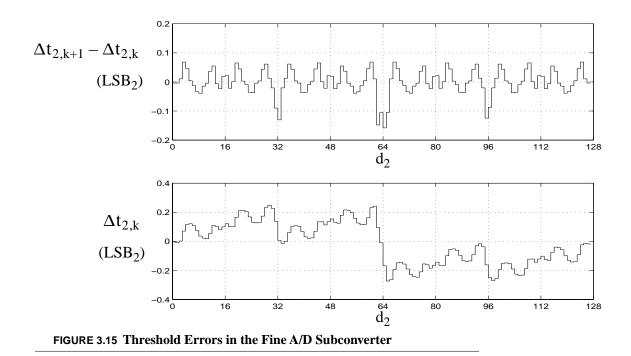

| FIGURE 3.15 | Threshold Errors in the Fine A/D Subconverter                                | 41 |

| FIGURE 3.16 | Relationship between pdf and Histogram for Ideal ADC                         | 42 |

| FIGURE 3.17 | Relationship between pdf and Histogram for ADC with Threshold Error 43       | ſS |

| FIGURE 3.18 | Relationship between pdf and Smoothed Histogram for Real ADC                 | 44 |

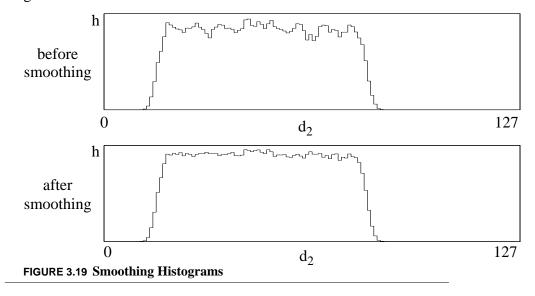

| FIGURE 3.19 | Smoothing Histograms                                                         | 45 |

| FIGURE 3.20 | Histogram Bound without and with Noise                                       | 46 |

| FIGURE 3.21 | Bound Estimates                                                              | 47 |

| FIGURE 3.22 | Threshold Errors in the Coarse A/D Subconverter                              | 49 |

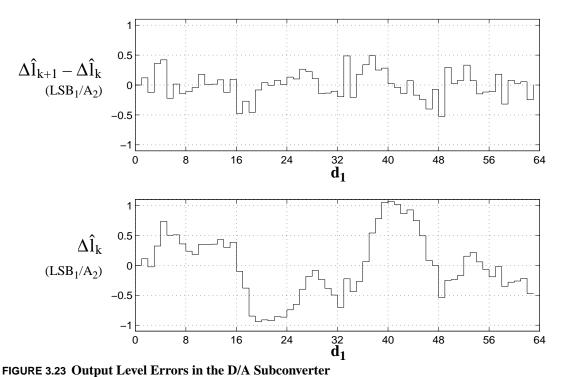

| FIGURE 3.23 | Output Level Errors in the D/A Subconverter             | 51 |

|-------------|---------------------------------------------------------|----|

| FIGURE 3.24 | Histogram Columns for Positive and Negative Slope Input | 54 |

| FIGURE 3.25 | Bidimensional Histogram of Faulty ADC                   | 55 |

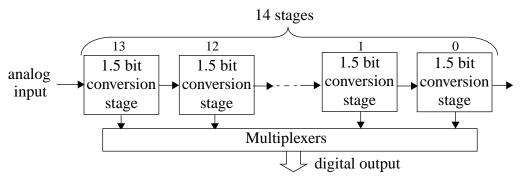

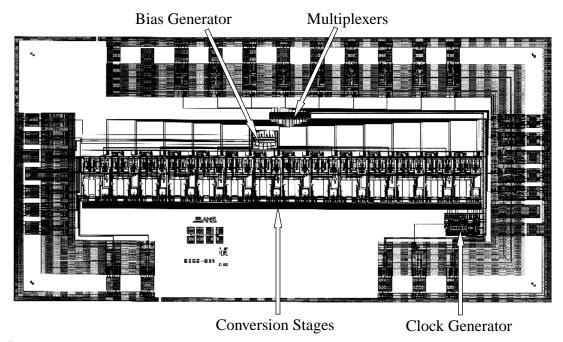

| FIGURE 4.2  | 14-Stage Pipeline ADC with Access to Internal Bits      | 60 |

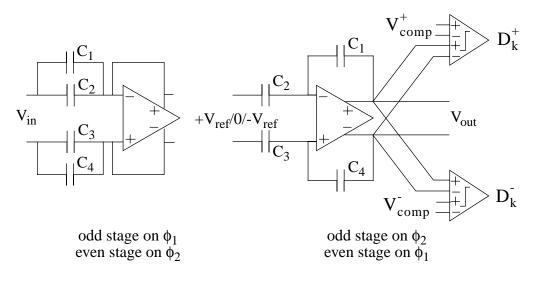

| FIGURE 4.3  | Two-Phase Operation of 1.5-Bit Conversion Stage         | 62 |

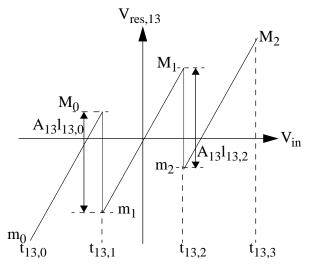

| FIGURE 4.4  | Transfer Characteristic of First Stage                  | 67 |

| FIGURE 4.5  | Transfer Characteristic of First Two Stages             | 71 |

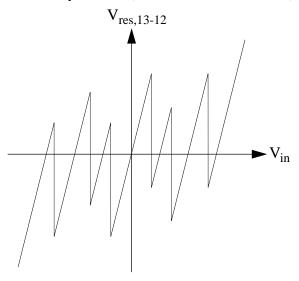

| FIGURE 5.2  | Histogram for Pipeline ADC with 2/12 Partition          | 75 |

| FIGURE 5.3  | Nonuniform and Locally Uniform Histograms               | 77 |

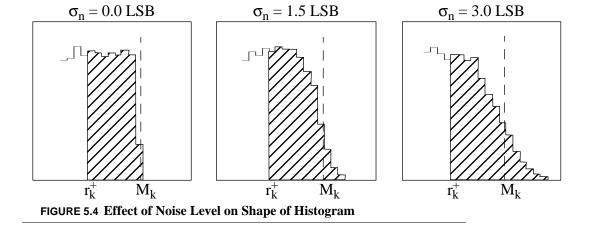

| FIGURE 5.4  | Effect of Noise Level on Shape of Histogram             | 77 |

| FIGURE 5.5  | Regions Used in Estimation                              | 79 |

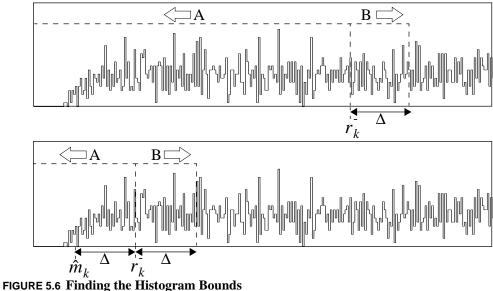

| FIGURE 5.6  | Finding the Histogram Bounds                            | 89 |

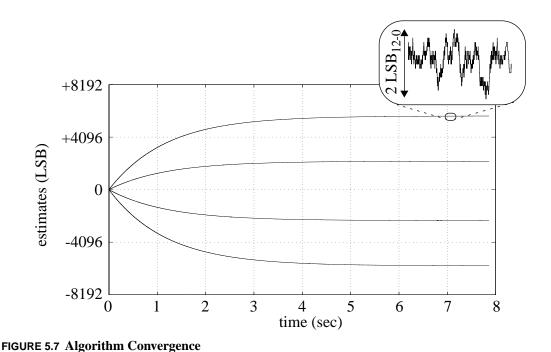

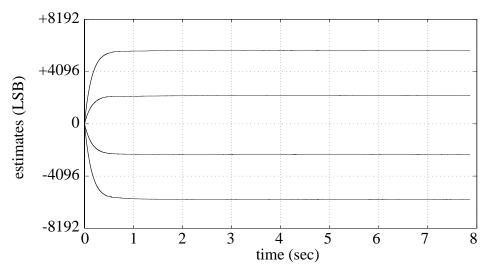

| FIGURE 5.7  | Algorithm Convergence                                   | 91 |

| FIGURE 5.8  | Algorithm Convergence with Two Steps                    | 92 |

| FIGURE 5.9  | Improvement in SFDR with Digital Correction             | 94 |

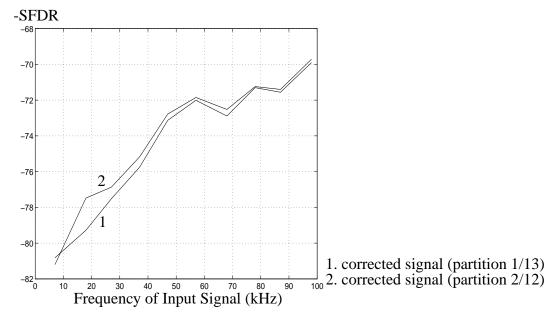

| FIGURE 5.10 | Digital Correction for Partitions 1/13 and 2/12         | 95 |

# Glossary of Terms

| $A, A_k \dots \dots$                 | . actual stage/inter-stage gain                                                |

|--------------------------------------|--------------------------------------------------------------------------------|

| $\hat{A}, \hat{A}_k \dots \dots$     | . estimated stage/inter-stage gain                                             |

| $\tilde{A}, \tilde{A}_k \dots \dots$ | . ideal stage/inter-stage gain                                                 |

| A/D                                  | . Analog-to-Digital                                                            |

| ADC                                  | . Analog-to-Digital Converter/Subconverter                                     |

| <i>d</i>                             | . digital output of overall A/D converter                                      |

| $\Delta\dots\dots\dots\dots\dots$    | . length of reference region for bound estimation                              |

|                                      | . adjustment step for digital correction algorithm                             |

| $d_k, d_{k-j}$                       | digital output of A/D subconverter                                             |

| $D_k$                                | digital output of conversion stage of pipeline ADC                             |

| $D_k^+, D_k^- \dots \dots$           | . comparator outputs of conversion stage of pipeline ADC                       |

| $D_{k_i}$                            | digital output of substage (magamp) of two-stage ADC                           |

| D/A                                  | . Digital-to-Analog                                                            |

| DAC                                  | . Digital-to-Analog Converter                                                  |

| $\Delta l_k \dots \dots$             | . D/A subconverter error: $l_k - \tilde{l}_k$                                  |

| DNL                                  | . Differential Nonlinearity (def. page 24)                                     |

| $\Delta t_{1, k} \dots \dots$        | . coarse/first A/D subconverter threshold error: $t_{1, k} - \tilde{t}_{1, k}$ |

|                                      | . fine/second A/D subconverter threshold error: $t_{2, k} - \tilde{t}_{2, k}$  |

| DVM                                  | . digital voltmeter                                                            |

| <i>E</i> []                          | . expected value                                                               |

| ENOB                                 | . Effective Number of Bits (def. page 25)                                      |

| FFT                                  | . Fast Fourier Transform                                                       |

| FS                                   | . Full Scale                                                                   |

| h                                    | . bin height                                                                   |

| $\bar{h}$                            | . average bin height                                                           |

| $h_j \dots \dots$                    | . height of bin j of unidimensional histogram                                  |

| $h_{j,k}$ height of bin $(j,k)$ of bidimensional histogram                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\hat{H}_{j}$ height of bin $j$ of reference histogram                                                                                                          |

| $\frac{H_j}{\hat{h}_k^+}, \frac{\hat{h}_k^-}{\hat{h}_k^-}$ height of bin $j$ of reference histogram average bin height in the vicinity of the transition region |

| INL Integral Nonlinearity (def. page 25)                                                                                                                        |

| $l_k$ actual D/A subconverter output levels                                                                                                                     |

| $\hat{l}_k$ estimated D/A subconverter output levels                                                                                                            |

| $\tilde{l}_k$ ideal D/A subconverter output levels                                                                                                              |

| LMS Least Mean Square                                                                                                                                           |

| LSB Least Significant Bit                                                                                                                                       |

| $LSB_k \dots \dots$ voltage corresponding to LSB of A/D suconverter $k$                                                                                         |

| $m_k$ actual lower bound of section $k$ of residue                                                                                                              |

| $\hat{m}_k$ estimated lower bound of section $k$ of residue                                                                                                     |

| $M_k \dots \dots$ actual upper bound of section $k$ of residue                                                                                                  |

| $\hat{M}_k$ estimated upper bound of section $k$ of residue                                                                                                     |

| MSB Most Significant Bit                                                                                                                                        |

| 2-12-2                                                                                                                                                          |

| pdf probablity density function                                                                                                                                 |

| -                                                                                                                                                               |

| pdfprobablity density function                                                                                                                                  |

| pdfprobablity density function $R, R_1, R_2$ nominal signal range at the input of converter / subconverter                                                      |

| pdf                                                                                                                                                             |

| $\hat{t}_{1,k}$ estimated thresholds of coarse/first A/D subconverter                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\tilde{t}_{1,k}$ ideal thresholds of coarse/first A/D subconverter                                                                                                                            |

| $t_{2, k}$ actual thresholds of fine/second A/D subconverter                                                                                                                                   |

| $\hat{t}_{2,k}$ estimated thresholds of fine/second A/D subconverter                                                                                                                           |

| $\tilde{t}_{2,k}$ ideal thresholds of fine/second A/D subconverter                                                                                                                             |

| THTrack-and-Hold                                                                                                                                                                               |

| $\hat{V}_{in}$ reconstructed input voltage                                                                                                                                                     |

| $V_{comp}^+, V_{comp}^-, \dots$ actual comparator thresholds in conversion stage                                                                                                               |

| $\hat{V}^+_{comp},\hat{V}^{comp}\dots$ estimated comparator thresholds in conversion stage                                                                                                     |

| $V_{ref}, V_{ref}^+, V_{ref}^-, \dots$ actual reference voltages in conversion stage $\hat{V}_{ref}, \hat{V}_{ref}^+, \hat{V}_{ref}^-, \dots$ estimated reference voltages in conversion stage |

| $\hat{V}_{ref}, \hat{V}_{ref}^{+3}, \hat{V}_{ref}^{-3}$ estimated reference voltages in conversion stage                                                                                       |

| $V_{res, k} \dots residue of stage k$                                                                                                                                                          |

| $V_{res, k-j}^{res, k}$ residue of suconverter containing stages $k$ to $j$                                                                                                                    |

### CHAPTER 1

# Introduction

This thesis proposes a new method of characterization of multi-stage A/D converters, capable of estimating the errors introduced by each of the internal blocks. It also proposes an adaptive digital correction mechanism derived from the aforementioned method, which was verified to effectively reduce the harmonic distortion of a real converter.

#### 1.1 Motivation

Multi-stage analog-to-digital converters predominate in applications that require high speed and numbers of bits in excess of ten, such as video and wideband radio applications. Flash converters, though faster, are not common beyond eight bits because their complexity increases exponentially, while folding and interpolation architectures, though showing good performance, are rarely found in commercial parts for the time being.

The (numerous) techniques currently used to test and characterize this type of A/D converters are identical to those used for any other type of A/D converters: the beat frequency and envelope tests, the servo-loop code transition measurement, the Fast Fourier Transform (fft) test, the sine-fitting test, the code density test, and many others. A common shortcoming of these methods is that they only provide information about the performance

Motivation 2

of the ADC at the system level, such as the overall differential nonlinearity (DNL) and integral nonlinearity (INL).

We propose a method geared specifically toward multi-stage architectures that can characterize their internal blocks and estimate the DNL and INL of the A/D and D/A subconverters, and the gain of the interstage amplifiers. The characterization can even go one step further and identify the sources of problems at the component level, for instance by revealing  $V_{be}$ , resistor, capacitor, and current mismatches, low gain in amplifiers, or hysteresis. One might ask, who needs this kind of information? Probably not the users of the ADCs, since they only need to know whether the chip meets the requirements imposed by their applications. On the other hand, the design engineers might find this inside information very handy: after all, if they know which blocks degrade the performance of the ADC, they also know what to do in order to fix it. The component-level information could also be used to characterize a process, especially in terms of matching, with a better accuracy (more than ten bits) than it would otherwise be possible.

The method proposed here is to some extent related to the standard code density test, inasmuch as both use histograms. However, they do not use the same kind of histograms: the latter uses unidimensional histograms while the former uses bidimensional histograms. There is also a significant difference of complexity. In one of the variants of the new method, the code density test is but one of the steps of a long procedure involving system solving, polynomial root finding, and least-squares approximations. There are however simpler variants, applicable to particular architectures, some of them simple enough to be turned into on-line digital correction logic. The extra complexity certainly pays off by the wealth of insightful information it offers.

The method can be applied to any multi-stage analog-to-digital converter, from two-stage to pipeline architectures, and was actually tested on two different chips: a two-stage A/D converter, namely the AD9042 from Analog Devices [AD95], [Mur95], and a 14-stage

Thesis Outline 3

pipeline ADC which we redesigned and fabricated from a previous version [Man96a], [Man96b], designed by Timo Rahkonen, Antti Manyniemi, and Antti Ruha, from the Department of Electrical Engineering of the University of Oulu, Finland.

Since the application of the proposed method requires an in-depth knowledge of the converters, a large part of this thesis is devoted to their analysis. Mathematical models are provided for both two-stage and pipeline ADCs, allowing for many possible nonidealities.

#### 1.2 Thesis Outline

The thesis could have been organized in more than one way. We could have presented first the general theory behind the characterization method and then the applications, but this would have made the presentation rather dry, so that we decided to explain the theory along with the applications.

The thesis comprises five chapters, apart from this introduction.

Chapter 2 deals with the architecture of a typical two-stage ADC, namely the AD9042, focusing on possible sources of nonlinearity and developing a mathematical model to be used in the characterization process.

Chapter 3 introduces the bidimensional histogram, which is the basis of the new method of characterization. After a short overview of current testing and characterization methods, the new method of characterization is presented step by step in its most elaborate form (to date). The advantages and limitations of the method are also discussed at length.

Chapter 4 describes the architecture of the pipeline ADC and provides a pseudo-two-stage model for it, in order to emphasize the similarities with the two-stage architecture presented before.

Thesis Outline 4

Chapter 5 introduces a simplified version (same idea, different implementation) of the new characterization method and an interesting spin-off of this method: an adaptive digital correction mechanism which, when tested on the output data stream of the pipeline ADC, improved the Spurious-Free Dynamic Range by 6dB over three quarters of the bandwidth.

Chapter 6 discusses the contributions of this thesis and possible future enhancements.

### **CHAPTER 2**

# Two-Stage A/D Converter Architecture

Classic characterization methods can be applied in the same way to any A/D converter, regardless of its architecture. On the contrary, the method that we propose, while offering much more internal information than classic methods, requires an exact knowledge of the converter architecture. Therefore, it seems only natural that we should devote a chapter to the description and mathematical modeling of the ADC to be characterized.

The converter discussed here is the AD9042 from Analog Devices [AD95], [Mur95]. Although its implementation may be different from those of other two-stage converters, the mathematical model can be applied with minor modifications to any of them.

#### 2.1 Introduction

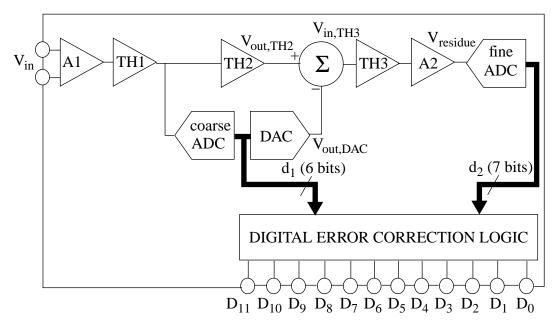

The AD9042 is a high-speed 12-bit A/D converter fabricated in a fast complementary bipolar technology. Its block diagram is presented in Figure 2.1.

The analog signal is applied at the input of the ADC, amplified by A1, sampled and held by TH1, and then quantized by the coarse ADC. The DAC turns the 6-bit digital output of this first conversion ( $d_1$ ), into an analog signal to be subtracted from the output of TH2, which is simply a delayed version of the output of TH1. In the subsequent clock cycle, the difference is held by TH3, amplified by A2, and quantized by the 7-bit fine ADC.

Introduction 6

FIGURE 2.1 Two-Stage ADC Architecture (AD9042)

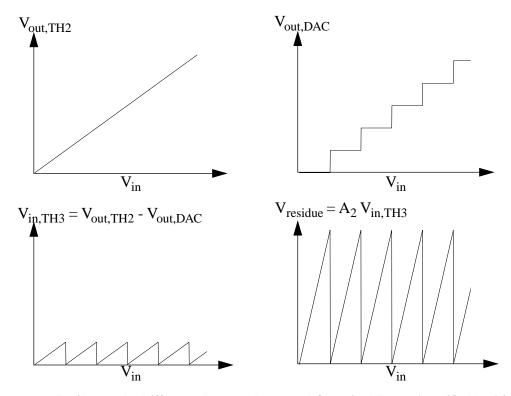

The operation of the two-stage ADC is illustrated in Figure 2.2. Assuming ideal components, the transfer characteristic of the branch containing the coarse ADC and the DAC will be a perfect staircase, and the residue will have a sawtooth shape, with identical "teeth".

The outputs of the two A/D subconverters are combined in the digital error correction block by overlapping the MSB of  $d_2$  ( $D_{2_6}$ ) and the LSB of  $d_1$  ( $D_{1_0}$ ), so that the overall digital output is calculated as

or simply

FIGURE 2.2 Residue as the Difference Between Input and Quantized Input, Amplified by A2

$$d = 2^6 \cdot d_1 + d_2 \tag{EQ 2.2}$$

Without the one-bit overlap the input-output characteristic might have deadbands because of component nonidealities. This technique is called range overlap and is explained in the following.

# 2.2 Range Overlap and Digital Correction

The input range of an A/D subconverter is defined by the number of bits and the voltage corresponding to one bit (i.e. the ideal value of the difference between two consecutive thresholds), as follows:

$$R_{in} = 2^N LSB (EQ 2.3)$$

Let  $R_{in2}$  be the input range of the fine ADC,  $R_1$  the nominal signal range at the input of the coarse ADC, and  $R_2$  the nominal signal range at the input of the fine ADC. From the block diagram in Figure 2.1, it is apparent that

$$R_2 = \frac{A_2}{2^6} \cdot R_1 \tag{EQ 2.4}$$

When designing a two-stage ADC, we could choose the gain  $A_2^{-1}$  so that the signal at the input of the fine subconverter covers its whole input range. In other words, the nominal signal range would be equal to the input range ( $R_2$  equal to  $R_{in2}$ ). Then,

$$A_2 = 2^6 \cdot \frac{R_{in2}}{R_1}$$

(EQ 2.5)

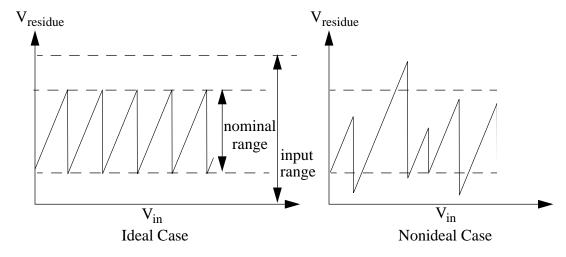

In reality, the coarse ADC will suffer from errors, and the residue will have an irregular form, as depicted in Figure 2.3 (right). Other components, such as the DAC, the summer, the track-and-hold circuits, and the amplifier A2, will also suffer from nonidealities, but the errors in the coarse ADC are by far the largest input-referred errors.

As a result of these errors, if  $A_2$  from (EQ 2.5) is used, parts of the residue will exceed the input range of the fine ADC and will be clipped: any voltage above the input range will be quantized as  $2^7$ -1, and any voltage below the input range will be quantized as 0. Consequently, the overall input-output characteristic will have deadbands. The solution used in the AD9042 to avoid clipping and deadbands is to make the gain  $A_2$  half of what it could be in the ideal case:

<sup>1.</sup> the notation A2 is used for the amplifier as such and  $A_2$  for its gain

FIGURE 2.3 Residue for Ideal and Nonideal Case

$$A_2 = \frac{1}{2} \cdot 2^6 \cdot \frac{R_{in2}}{R_1}$$

(EQ 2.6)

Thus, for each value of  $d_1$ , only about half of the range of the fine ADC is actually used. This redundancy is normally meant to enable the overall converter to tolerate coarse ADC errors (see Section 2.4 for a mathematical analysis and proof). In this thesis we will make further use of this redundancy to characterize each of the components of the ADC (Chapter 3).

Note that the reduction of  $\frac{1}{2}$  in the analog domain must be accompanied by a similar reduction in the digital domain, otherwise the overall input-output characteristic would not be linear. This means that the coefficient of  $d_1$  in (EQ 2.2) is  $2^6$  and not  $2^7$ , although the fine subconverter has 7 bits.

# 2.3 Sources of Nonlinearity in a Two-Stage ADC

The purpose of this thesis is to provide a method capable of characterizing and if possible fixing the nonidealities that affect (negatively) the performance of the ADC. These nonidealities are briefly surveyed here and will be analyzed in more detail in subsequent chapters.

A complete block diagram of the AD9042 has been presented in Figure 2.1. We will verify (see Section 2.4) that the blocks relevant for linearity are the D/A subconverter, the amplifier A2, and the fine A/D subconverter.

We will also prove (also in Section 2.4) that for this particular architecture the errors in the coarse A/D subconverter do not affect the overall ADC linearity. As to the other blocks, in a well-designed ADC the track-and-hold circuits (TH1, TH2, TH3), the amplifier (A1) and the summer ( $\Sigma$ ) can be assumed not to cause any significant increase in nonlinearity. Note that in terms of nonlinearity, a gain error in A1 is irrelevant, while a gain error in A2 can be a serious problem.

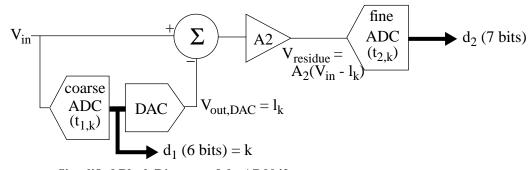

Figure 2.4 presents a simplified block diagram, including all the blocks capable of causing significant nonlinearity. Some of the other blocks are not shown. All the calculations will be based on this diagram and the notation will be explained at the beginning of the next section.

FIGURE 2.4 Simplified Block Diagram of the AD9042

Residue Modeling 11

## 2.4 Residue Modeling

Most of the calculations required by the characterization process revolve around the residue. Therefore it is necessary to provide a formal mathematical model for it.

Let  $V_{in}$  be the analog input signal,  $t_{1,k}$ , k=0...64, the thresholds of the coarse A/D subconverter,  $t_{2,k}$ , k=1...127 the thresholds of the fine A/D subconverter,  $l_k$ , k=0...63, the output levels of the DAC, and  $LSB_1$  and  $LSB_2$  the voltages corresponding to one bit of the coarse and the fine subconverter respectively. The actual thresholds are from  $t_{1,1}$  to  $t_{1,63}$  and from  $t_{2,1}$  to  $t_{2,127}$ . We also introduced  $t_{1,0}$  = 0,  $t_{1,64}$  = 64  $LSB_1$ ,  $t_{2,0}$  = 0, and  $t_{2,128}$  = 128  $LSB_2$  to simplify the equations and we assumed the input to be between  $t_{1,0}$  and  $t_{1,64}$ , otherwise the signal is clipped.

This choice of values for  $t_{1,0}$ ,  $t_{1,64}$ ,  $t_{2,0}$ , and  $t_{2,128}$  implies that we are ignoring the overall offsets and gains of the subconverters. In practice these parameters are of less interest than nonlinearity, and therefore they are not covered in this thesis. The characterization method that we propose (Chapter 3) could be modified to take them into account, but some extremely accurate signal generators and measurement equipment would be required.

Ideal values will be marked with a tilde sign (e.g.  $\tilde{t}_{I,k}$ ) to distinguish them from real values (e.g.  $t_{I,k}$ ), and the difference between them will be marked with  $\Delta$  (e.g.  $\Delta t_{I,k} = t_{I,k} - \tilde{t}_{I,k}$ ). Estimated values will have a circumflex accent (e.g.  $\hat{t}_{I,k}$ ).

The output of the coarse A/D subconverter may be defined as

$$d_1(V_{in}) = k$$

,  $t_{1,k} < V_{in} \le t_{1,k+1}$   $k = 0...63$  (EQ 2.7)

This digital signal is fed to the D/A subconverter which turns it into an analog signal:

$$V_{out,DAC}(d_k) = l_k$$

,  $k = 0...63$  (EQ 2.8)

Residue Modeling 12

Replacing (EQ 2.8) in (EQ 2.7) we obtain:

$$V_{out,DAC}(V_{in}) = l_k$$

,  $t_{1.k} < V_{in} \le t_{1.k+1}$   $k = 0...63$  (EQ 2.9)

This signal is then subtracted from  $V_{in}$  and amplified by  $A_2$  so that the residue is

$$V_{residue}(V_{in}) = A_2(V_{in} - l_k)$$

,  $t_{I,k} < V_{in} \le t_{I,k+1}$   $k = 0...63$  (EQ 2.10)

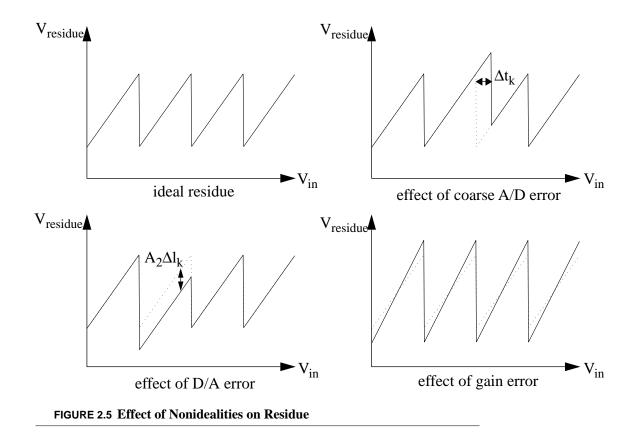

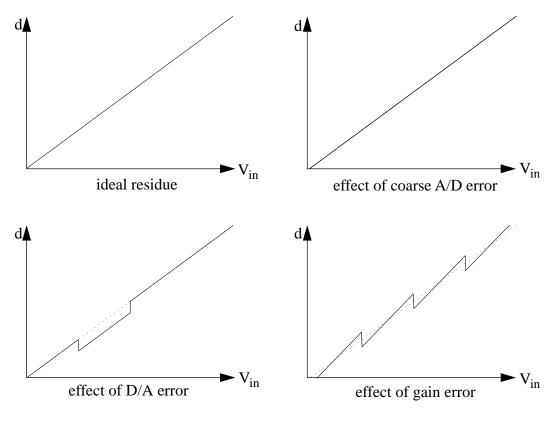

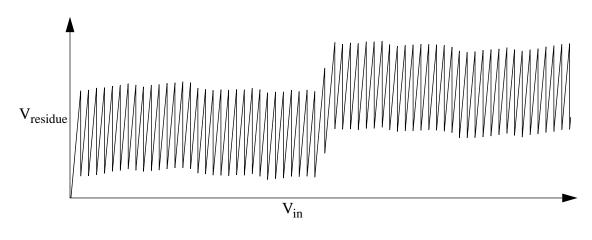

This equation enables us to visualize the effect on residue of coarse ADC errors ( $\Delta t_{1,k}$ ), DAC errors ( $\Delta l_k$ ), and gain errors, as shown in Figure 2.5. Note that only four sections of the residue are represented (out of 64).

It can be seen that each of these errors changes the residue in a distinct way: each coarse ADC error moves horizontally the transition between sections of residue corresponding to

Residue Modeling 13

consecutive  $d_1$  codes, each DAC error moves vertically the section of the corresponding  $d_1$  code, and a gain error will either lengthen or shorten <u>all</u> the sections of the residue.

Assuming an ideal fine A/D subconverter with infinite precision (i.e. assuming  $V_{residue} = A_2 \cdot (V_{in} - l_k) = d_2 \cdot LSB_2$ ), for a given digital output  $(d_1 \text{ and } d_2)$  the reconstructed input is equal to the sum of the contributions of the first stage  $(d_1 \cdot LSB_1)$  and second stage  $(\frac{d_2 \cdot LSB_2}{\tilde{A}_2})$ :

$$\begin{split} \hat{V}_{in} &= d_1 \cdot LSB_1 + \frac{d_2 \cdot LSB_2}{\tilde{A}_2} \\ &= \tilde{l}_k + \frac{A_2 \cdot (V_{in} - l_k)}{\tilde{A}_2} \\ &= \frac{A_2}{\tilde{A}_2} \cdot V_{in} + \left(\tilde{l}_k - l_k \cdot \frac{A_2}{\tilde{A}_2}\right) \end{split} \tag{EQ 2.11}$$

From (EQ 2.12) we can draw a number of conclusions:

- threshold errors in the coarse ADC ( $\Delta t_{I,k} = t_{I,k} \tilde{t}_{I,k}$ ) do not appear in the formula and therefore have no effect whatsoever on the linearity (assuming they do not push the residue out of the range of the fine ADC)

- DAC errors ( $\Delta l_k = l_k \tilde{l}_k$ ) cause nonlinearity in the overall ADC input-output characteristic

- a gain error in A2 causes both nonlinearity and gain error in the overall ADC input-out-put characteristic. However, in some cases, a small gain error (first term in (EQ 2.12)) is acceptable but discontinuities are not (second term). In order to eliminate the second term, we only need to know the  $(A_2l_k)$  products; we do not have to estimate  $A_2$  and  $l_k$ , k=0...63, separately.

Residue Bounds 14

How these errors affect the overall ADC characteristic is shown in Figure 2.6 (again, only part of the characteristic is shown).

FIGURE 2.6 Effect of Nonidealities on ADC Characteristic

Errors in the fine ADC must also be taken into account as they affect the overall linearity by making  $V_{residue}$  different from  $d_2$   $LSB_2$ .

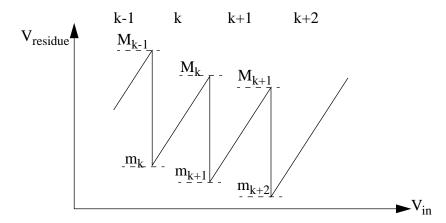

### 2.5 Residue Bounds

Of particular importance to the characterization process are the lower and upper bounds of each of the 64 sections of the residue (Figure 2.7), where a section is considered to be the

Residue Bounds 15

part of the residue corresponding to a single  $d_1$  code. We will denote these bounds by  $m_k$  and  $M_k$ , respectively, with k=0...63.

FIGURE 2.7 Lower and Upper Bounds of the Residue

We can calculate  $m_k$  and  $M_k$  from (EQ 2.10):

$$\begin{split} M_k &= A_2 \cdot (t_{1,\mathbf{k}+1} - l_k) \\ m_k &= A_2 \cdot (t_{1,\mathbf{k}} - l_k) \end{split} \tag{EQ 2.13}$$

Let us assume for the moment that all  $M_k$  and  $m_k$  are known (we will see later how they can be estimated). Then it is possible to form a system of equations using (EQ 2.13) for k = 0...63. This system has 128 unknown variables ( $A_2$ ,  $t_{1,k}$  (k=1...63), and  $l_k$  (k=0...63)) and 128 equations, and is in fact quite easy to solve. First we arrive at

$$M_k - m_k = A_2 \cdot (t_{1,k+1} - t_{1,k})$$

,  $k = 0...63$  (EQ 2.14)

which by summing for all k yields:

$$\sum_{k=0}^{63} (M_k - m_k) = A_2 \cdot (t_{1,64} - t_{1,0}) \tag{EQ 2.15}$$

Residue Bounds 16

Since  $t_{1,64}$  and  $t_{1,0}$  are known, we can calculate  $A_2$ :

$$\sum_{k=0}^{63} (M_k - m_k)$$

$$A_2 = \frac{k=0}{64 \cdot LSB_1}$$

(EQ 2.16)

Then the coarse A/D thresholds and the D/A output levels can be determined progressively from (EQ 2.13):

$$t_{1,k+1} = \frac{M_k - m_k}{A_2} + t_{1,k}$$

,  $k = 0...62$  (EQ 2.17)

$$l_{k+1} = \frac{M_k - m_{k+1}}{A_2} + l_k$$

,  $k = 0...62$  (EQ 2.18)

where  $l_0=0$  and  $t_{1,0}=0$ .

The following chapters will show that the bounds ( $M_k$  and  $m_k$ ) can be estimated, and (EQ 2.16), (EQ 2.17), and (EQ 2.18) will be used to calculate the desired parameters.

Alternatively, if all we need are the  $(A_2l_k)$  products, we can use

$$(A_2 l_{k+1}) = (A_2 l_k) + M_k - m_{k+1}, \qquad k = 0...62$$

(EQ 2.19)

Now if we go back to (EQ 2.2) we can see that the first term is

$$2^{6} \cdot d_{1} = \tilde{A_{2}} \cdot d_{1} = \tilde{A_{2}} \cdot \frac{\tilde{l_{k}}}{LSB_{1}}$$

(EQ 2.20)

A better formula for the digital output (EQ 2.2) can be found by replacing this term with the actual value,  $\frac{A_2 l_k}{LSB_1}$ :

$$d = \frac{(A_2 l_k)}{LSB_1} + d_2 (EQ 2.21)$$

since the reconstructed input  $\hat{V}_{in}$  in this case would be

$$\begin{split} \hat{V}_{in} &= \frac{(A_2 l_k)}{\tilde{A}_2} + \frac{d_2 \cdot LSB_2}{\tilde{A}_2} \\ &= \frac{(A_2 l_k)}{\tilde{A}_2} + \frac{A_2 \cdot (V_{in} - l_k)}{\tilde{A}_2} \end{split}$$

(EQ 2.22)

$$=\frac{A_2}{\tilde{A}_2}\cdot V_{in} \tag{EQ 2.23}$$

Please note the differences between (EQ 2.2) and (EQ 2.21), and between (EQ 2.12) and (EQ 2.23). Although in (EQ 2.23) we still have a gain error, the nonlinear term from (EQ 2.12) has disappeared.

It is apparent that although (EQ 2.16), (EQ 2.17), and (EQ 2.18) are more suitable for characterization, (EQ 2.19) may be a better option for correction, since it is easier to implement (it does not require division).

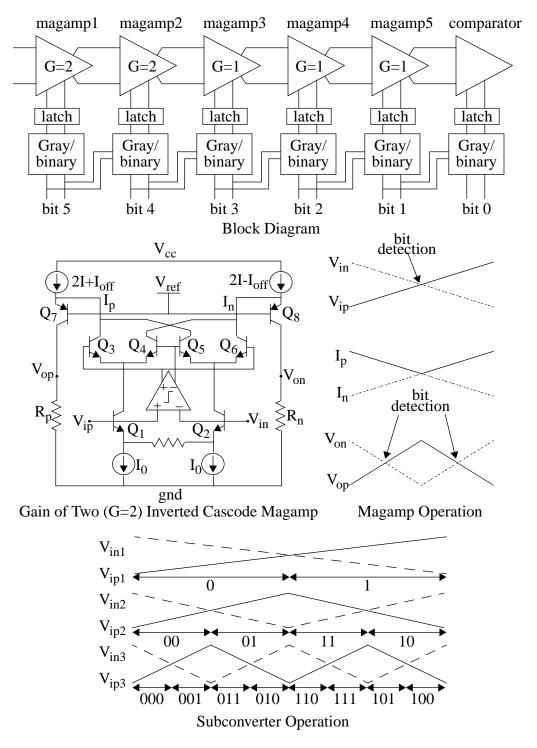

#### 2.6 A/D Subconverter Architecture

In Chapter 3 we will estimate the errors in the coarse and fine A/D subconverters. Some knowledge of the architecture of these components is a prerequisite to interpreting the estimated errors. Therefore, a brief description of the structure and operation of the subconverters of the AD9042 is included in this chapter. Since their architecture is quite unusual, the typical flash (subconverter) architecture is also presented.

The two coarse and fine subconverters of the AD9042 are similar, except for the number of bits, so that only the coarse ADC is explained here (Figure 2.8, top). This is based on a cascaded architecture with five magnitude amplifiers (magamp) and a comparator. The design of the first two magamps (those with gain of two, G=2) is shown in Figure 2.8, middle-left, and their operation is illustrated in Figure 2.8, middle-right. The other magamps (those with gain of one, G=1) have a different design, but their behavior is almost the same, and at any rate their effects, referred to the input of the subconverter, are smaller, so that they are not analyzed here.

The magamps are fully differential which means that as we (dc) sweep the positive input voltage  $V_{ip}$ , the negative input voltage  $V_{in}$  will be swept in the opposite direction (Figure 2.8, middle-right; note that the horizontal axis is always  $V_{ip}$ ). The current through  $Q_1$  will increase and the one through  $Q_2$  will decrease. At first  $V_{ip}$  is less than  $V_{in}$  so that the comparator keeps  $Q_4$  and  $Q_5$  on and  $Q_3$  and  $Q_6$  off, thus steering the collector currents of  $Q_1$  and  $Q_2$  through  $Q_4$  and  $Q_5$ , respectively, and subtracting them from the currents of the sources, 2I- $I_{off}$  and 2I+ $I_{off}$ , respectively. Since  $I_n$  increases, the current through  $R_n$  and the voltage across it,  $V_{on}$ , decrease. Similarly,  $I_p$  decreases, therefore the current through  $R_p$  and  $V_{op}$  increase.

When  $V_{ip}$  becomes greater than  $V_{in}$ , the comparator turns  $Q_4$  and  $Q_5$  off and  $Q_3$  and  $Q_6$  on, forcing the collector currents of  $Q_1$  and  $Q_2$  to go through  $Q_3$  and  $Q_6$ , respectively. These currents are subtracted from those of the sources. Since  $I_p$  now increases and  $I_n$  decreases, the currents through and the voltages across the resistors  $R_p$  and  $R_n$  will reverse their direction of change. The characteristic is shown in Figure 2.8, middle-right.

It is easy to see that with each magamp, the number of bit detection points doubles (Figure 2.8, bottom). Due to the shape of the transfer characteristic ( $V_{op}$  vs.  $V_{ip}$ ), with a positive slope at first and a negative slope afterward, the outputs are inherently in Gray code and

FIGURE 2.8 Coarse ADC Architecture

must be subsequently converted to binary. The latching is done after all the magamps have settled.

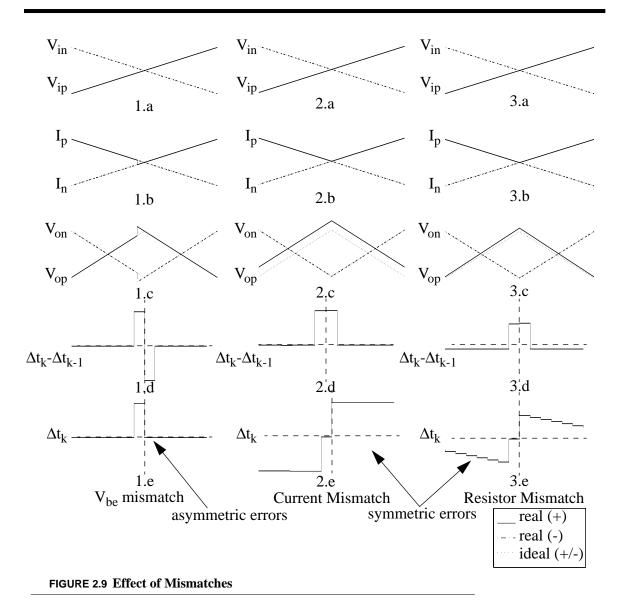

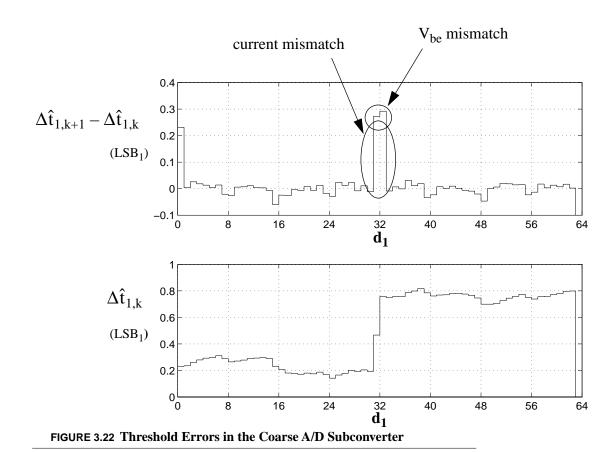

In practice many things can go wrong with this circuit. The worst offenders are, in all likelihood,  $V_{be}$ , resistor, and current mismatches. The effect of each of these mismatches occurring in the MSB stage (magamp 1) on the thresholds of the following stages can be seen in Figure 2.9. Both the threshold errors ( $\Delta t_k$ ) and the difference between consecutive threshold errors ( $\Delta t_k$ - $\Delta t_{k-1}$ ) have been plotted, and we will refer later to these plots to understand the estimated INL and DNL (defined on page 25 and page 24, respectively) of the subconverters. Since the  $\Delta t_k - \Delta t_{k-1}$  plots have been derived here from the  $\Delta t_k$  plots, the reader is urged to focus on the latter for the following explanation of the shape of these curves.

In the case of  $V_{be}$  mismatch either in  $Q_1$ - $Q_2$  or in the input transistors of the comparator, the currents through  $Q_1$  and  $Q_2$  are switched (Figure 2.9-1.b) not at the point where they are equal but at a different point, which causes discontinuities in the currents  $I_p$  and  $I_n$ . These discontinuities also appear in  $V_{op}$  and  $V_{on}$  in the central region (Figure 2.9-1.c) but leave the rest of the characteristic unaffected, and as a result, the thresholds of the following stages are not changed ( $\Delta t_k = 0$ ). The only threshold changed is that of magamp 1 (the one in the middle in Figure 2.9-1.e).

A current mismatch in  $2I + I_{off}$  for instance will not affect  $I_p$  (Figure 2.9-2.b), but will shift  $V_{op}$  (Figure 2.9-2.c) up or down. Let us assume that the curve is shifted up. Then the thresholds (of the following stages) on the left side will decrease (Figure 2.9-2.e, watch for instance the left bit-detection point which is one of the thresholds due to magamp 2, considered to be ideal), while the thresholds on the right side will increase (watch the right bit-detection point, which is the other threshold due to magamp 2).

A resistor mismatch in  $R_p$  for example will only affect  $V_{op}$  (Figure 2.9-3.c), and will cause the thresholds on the left side to decrease and those on the right side to increase. As opposed to the previous case, the change is not the same for all thresholds, because the change in  $V_{op}$  is not constant.

Summary 22

A common error in data converters is hysteresis. Although the AD9042 suffers from this problem, we believe it does not originate from the A/D subconverters, so it is not discussed here (see Section 3.9).

Other types of errors are also possible, but, in our opinion, all of them fall into two categories:

- errors that cause symmetrical changes in all the thresholds of the following stages

except those next to the bit transition, e.g. resistor and current mismatches, and

- errors that cause only an asymmetric change in the thresholds next to the bit transition, e.g.  $V_{he}$  mismatch.

Later we will derive plots of the threshold errors in both subconverters, and we will see that both categories of errors are readily distinguishable.

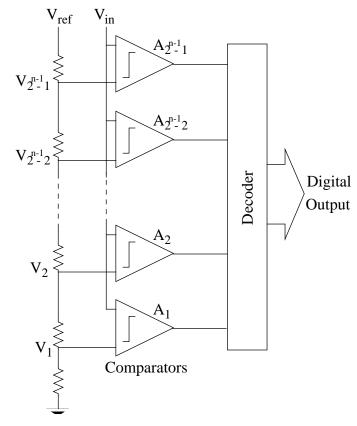

The cascaded architecture presented so far is far from being a common choice. Most two-stage ADCs use flash subconverters, like the circuit presented in Figure 2.10. For n bits, there are  $2^n - 1$  comparators which compare the input signal to a number of  $2^n - 1$  equally spaced reference voltages, in this case generated from a single reference by a voltage divider with  $2^n$  equal-size resistors. Suppose that the input is between the references  $V_j$  and  $V_{j+1}$ . The outputs of the comparators from  $A_1$  to  $A_j$  will be 1, and the outputs of the comparators from  $A_{j+1}$  to  $A_{2^n-1}$  will be 0. It is apparent that these outputs constitute a thermometer code, which can be converted to a binary representation by the decoder.

## 2.7 Summary

In this chapter we have seen the basic principles of the two-stage ADC architecture, including range overlap and digital correction. A model has been developed for this

Summary 23

**FIGURE 2.10 Typical Flash Architecture**

architecture, and the components relevant for linearity have been identified. Particular attention has been given to the residue and equations relating internal parameters to residue bounds have been found. The architecture of the A/D subconverters has also been explained briefly.

## **CHAPTER 3**

# Characterization of Two-Stage A/D Converters

Many testing and characterization methods are available for A/D converters. This chapter, after overviewing the existing methods, all of which are based on a black-box approach, presents a new method which actually diagnoses the chip by offering more information about what is happening inside the chip and how different blocks degrade the overall performance. The application of this method is described in detail, as are its advantages and limitations.

### 3.1 Definition of ADC Specifications

A number of performance metrics are used for the characterization of nonlinearity in multi-stage A/D converters. The ones that are used throughout this thesis are defined in the following [Raz95].

Differential Nonlinearity (DNL) The deviation of the actual voltage difference between two consecutive thresholds from its ideal value, LSB:

$$DNL_k = (t_{k+1} - t_k) - LSB$$

(EQ 3.1)

where  $t_k$  is the threshold that separates code k-1 from code k. Sometimes only the maximum value is indicated:

$$DNL = max(|DNL_k|)$$

(EQ 3.2)

Integral Nonlinearity (INL) The deviation of the actual value of a threshold from its ideal value:

$$INL_k = t_{k+1} - k \cdot LSB$$

$INL = max(|INL_k|)$  (EQ 3.3)

Signal-to-Noise Ratio (SNR) The ratio of the signal power to the noise power (excluding harmonics and dc) at the output of the ADC, usually for an input 1dB below full scale, expressed in dB:

$$SNR = 10 \cdot \log_{10} \left(\frac{P_s}{P_n}\right)$$

(EQ 3.4)

Signal-to-Noise-and-Distortion Ratio (SINAD) The ratio of the signal power to the power of all other spectral components (including harmonics but excluding dc)

Spurious-Free Dynamic Range (SFDR) The ratio of the power of the signal to the power of the peak spurious spectral component, in the worst case over the frequency range and the best case over the level range.

Effective Number of Bits (ENOB) Defined by the following equation:

$$ENOB = \frac{SINAD - 1.76}{6.02} \tag{EQ 3.5}$$

## 3.2 Prior Art of ADC Characterization

Almost any book on data converters has a chapter devoted to testing and characterization methods. These methods range from quick, qualitative tests (e.g. beat frequency and envelope tests) to thorough tests that require extensive mathematical processing on a computer (e.g. sine-fitting and fft tests). A few of the more precise tests are briefly presented here.

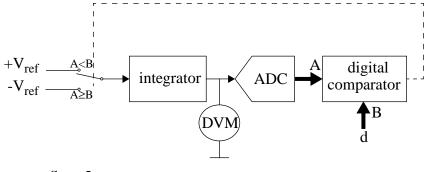

Servo-Loop Code Transition Measurement. A negative feedback loop like the one in Figure 3.1 allows us to measure the threshold between any two codes [Bla94], [Cap95], [Dem91], [Raz95], [She86]. Suppose that the output of the integrator is zero and we apply a code d at the input B of the digital comparator. Then, A<B, so that  $+V_{ref}$  will be coupled to the integrator and its output will increase until A≥B, when  $-V_{ref}$  will be coupled to the integrator and its output will decrease. The integrator output will then oscillate around the threshold which separates codes d-1 and d, and this threshold can be measured with a digital voltmeter (DVM). Once all the thresholds are known, DNL and INL plots can be derived. Since the noise is integrated out and the digital comparator introduces an infinite gain, the accuracy is very good even with a low-quality integrator. Furthermore, the method can be easily automated. On the negative side, the method is rather slow, and its performance is limited by the correctness of the model used. For instance it does not take into account hysteresis.

FIGURE 3.1 Servo Loop

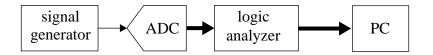

FIGURE 3.2 Set-Up for the FFT, Sine-Fitting, and Code Density Tests

A number of other tests (FFT, sinewave fitting, code density) can be performed using the circuit shown in Figure 3.2, which contains a signal generator, a logic analyzer, and a computer. The digital output of the ADC is sampled by the logic analyzer and transferred to a computer.

FFT Test. The discrete Fourier transform of the digital output signal for a sinusoidal input (see Figure 3.3) provides information on noise and harmonic distortion [Dem91], [Raz95]. The power of the signal, harmonics, and noise, SNR, SINAD, and SFDR can be determined from the spectrum. The method is very reliable and efficient, since it requires relatively few samples compared to the code density test (which is explained later in this chapter). The signal used for testing must be a very pure sinewave, and some LC filtering may be required to meet this condition.

frequency

FIGURE 3.3 Power Spectrum of ADC Output for a Sinusoidal Input

Sinewave Fitting. Another approach is to collect the samples of a sinewave, estimate its parameters (offset, amplitude, frequency, phase) using mathematical software, and calculate the noise and harmonic distortion by subtracting the estimated sinewave from the actual sinewave [Dem91], [Raz95].

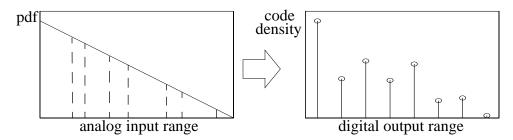

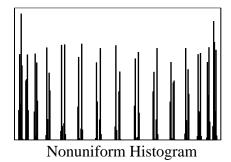

Code Density Test. Suppose we apply a triangular waveform at the input of the ADC under test and collect a large number of samples at the output. Assuming that the signal frequency is not commensurate to the clock frequency (i.e. not related to the clock frequency by a ratio of integers), the value of the signal can be considered to be a random variable with uniform pdf. The probability of occurrence of a code will then be indicative of its DNL. If the two thresholds that define the code are closer to each other than they should be (DNL<0), the probability will be lower than average, since a smaller interval is less likely to be hit. Conversely, if the thresholds are farther from each other (DNL>0), the probability will be higher.

By plotting the number of occurrences of each code (this number is referred to as code density) a so-called histogram is obtained (Figure 3.4, right). The number of samples should be large so as to make the experimental code density plot an accurate replica of the

theoretical code probability plot. DNL and INL can be calculated from these histograms using a procedure which will be described in Section 3.5 [Cap95], [Chi96], [Dem91], [Mor94], [Raz95], [Wag91].

In practice it is difficult to ensure that the triangular signal has the linearity required, so sinewaves are used instead. Although they do not have a constant pdf, they are well-defined (ultralinear signal generators are employed), and therefore their pdf can be calculated with high accuracy. The code density is then normalized with respect to the pdf, and the procedure is identical to the one used for triangular waveforms.

What all of the above tests have in common is that they only characterize the ADC at the system level, and therefore offer little or no information about the internal blocks of the converter. The explanation is that they do not use the knowledge about the architecture of the converter. In the following chapters we will show how this knowledge can be used to devise a new method, that can characterize each of the blocks relevant for the overall linearity.

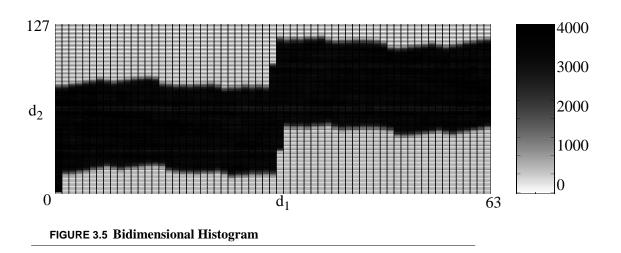

## 3.3 Bidimensional Code Density Tables

In Section 2.1 we showed that the digital output d of a two-stage A/D converter results from combining the outputs of two A/D subconverters,  $d_1$  and  $d_2$  (refer to Figure 2.4). The whole characterization process proposed here is based on the idea that we should build code density tables not as a function of the overall output d, but as a function of  $d_1$  and  $d_2$ .

A problem with this approach that comes to mind immediately is how to actually get  $d_1$  and  $d_2$ . The AD9042, like all commercial parts, only provides d at the output and it is not possible to calculate  $d_1$  and  $d_2$  from d, since some information is lost in the digital error correction process. Analog Devices provided us with two modified parts for testing, in

which an internal signal, the MSB of  $d_2$ , could be accessed via two of the normally unused pins. Once this signal is available,  $d_2$  can recovered from its MSB and the last six bits of d, and  $d_1$  from the first six bits of d less the MSB of  $d_2$ .

Unfortunately, one of the parts suffered from missing codes, so that it could not be used for testing. Therefore, all the plots and computations in this chapter refer to a single AD9042 part, and we will not make any attempt to generalize.

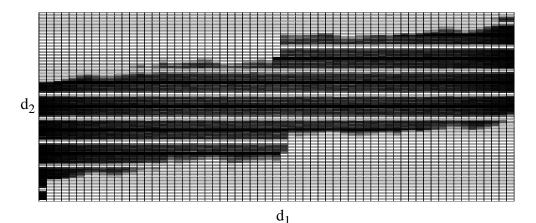

The new code density table will be a  $2^6$  by  $2^7$  matrix instead of a vector with  $2^{12}$  components as in a classic code density test. An example is shown in Figure 3.5, using a plane representation with the degree of darkness proportional to the frequency of  $(d_2, d_1)$  pairs. Dark areas indicate pairs that occur frequently, while light areas indicate pairs that occur rarely. We will call this representation a bidimensional histogram.

As we will show in Section 3.8, errors in the amplifier A2, the coarse A/D subconverter, and the D/A subconverter can be estimated from these bidimensional histograms. Based on these estimations we can reconstruct to a good approximation the residue, as in Figure 3.6. A quick comparison between Figure 3.5 and Figure 3.6 reveals the connection between the bidimensional histogram and the residue: the residue dictates the shape of the histogram and, as a result, the histogram contains information about the residue. It is this information that will enable us to characterize the components of the ADC.

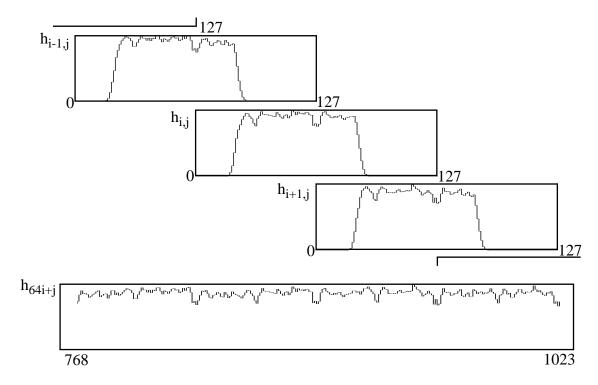

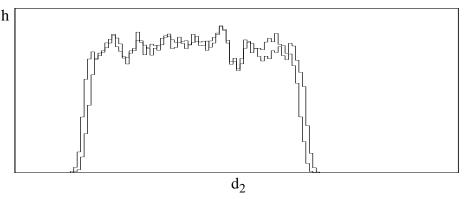

We are also interested in individual columns of the matrix, like the one plotted in Figure 3.7 using a stairstep representation. We mentioned before that the section of the residue corresponding to a given  $d_1$  code only occupies about half of the input range of the fine subconverter. The same happens to the columns of the bidimensional histogram: for a given value of  $d_1$ , only about half of the possible values of  $d_2$  occur. A more in-depth discussion of the shape of these histogram columns is provided in Section 3.4.

FIGURE 3.6 Residue Plot

The last issue that will be approached here is the relationship between unidimensional and bidimensional histograms, illustrated in Figure 3.8. The columns of the bidimensional histogram, offset in steps of  $64 \ LSB_2$  and added together result in the unidimensional histogram. On the other hand, it is not possible to reconstruct the bidimensional histogram from the unidimensional histogram.

The relationship can be expressed as:

FIGURE 3.8 Relationship between Uni- and Bidimensional Histograms

FIGURE 3.7 Code density for  $d_1 = 3$  and  $d_2$  from 0 to 127

$$h_j = h_{0,\,j}$$

$j = 0...63$  (first half of first column)  $h_{64i\,+\,j} = h_{i,\,j} + h_{\mathrm{i}+1,\mathrm{j}-64}$   $i = 0...62,\,j = 64...127$  (EQ 3.6)  $h_{64\,\cdot\,62\,+\,j} = h_{63,\,j}$   $j = 64...127$  (second half of last column)

where h with an index refers to the unidimensional histogram, and h with two indices refers to the bidimensional histogram.

## 3.4 Columns of the Bidimensional Histogram

In order to extract all the information available in the columns of the bidimensional histogram, we have to understand the factors that affect them. These factors are analyzed in the following.

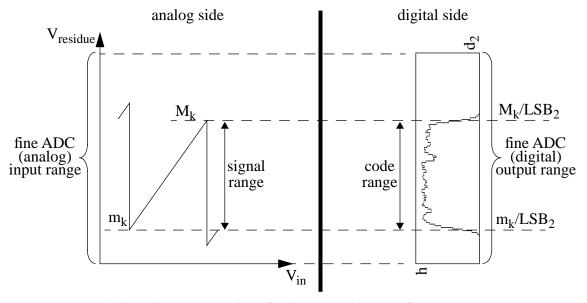

We have mentioned before that the residue dictates the shape of the histogram. The mechanism is illustrated in Figure 3.9. Since the residue signal for code  $d_1=k$  ranges from  $m_k$  to  $M_k$ , the output codes  $(d_2)$  will range from  $m_k/LSB_2$  to  $M_k/LSB_2$ . Hence it is possible

FIGURE 3.9 Relationship between Residue Sections and Histogram Columns

to estimate the bounds of each residue section from the bounds of the corresponding histogram column. For convenience, from now on all the voltages will be expressed in terms of  $LSB_1$  or  $LSB_2$  so that we can use the same notation for analog values and their digital equivalent. For instance,  $M_k$  will be both the analog upper bound of the residue and the projection thereof on the digital axis.

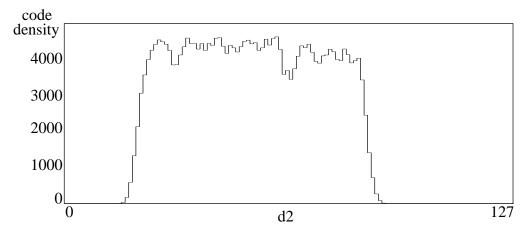

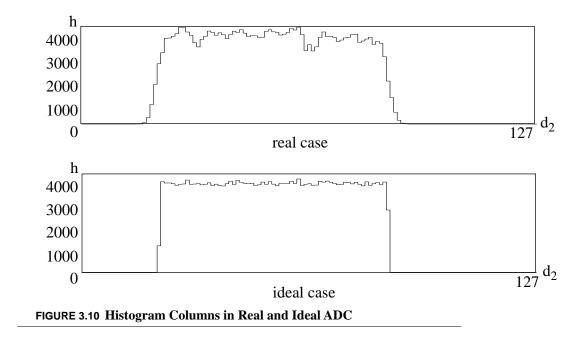

A closer look at the histogram column reveals that its shape is not what we might expect to see for an ideal ADC in which the residue has the same bounds (see Figure 3.10). In the

ideal case (simulated using a random uniform distribution with the same number of samples as in the real case), the heights of the non-zero bins are about equal, except for two incomplete bins at the left and right end. The presence of incomplete bins is explained by the relative position of  $m_k$  and  $M_k$  with respect to the closest thresholds of the fine ADC. For instance if  $m_k$  coincides with the threshold  $t_{2,j}$  then bin j-1 will be empty while bin j will be of average height, and if  $m_k$  is exactly in the middle between  $t_{2,j}$  and  $t_{2,j+1}$ , bin j will only be of half the average height.

Note that in both cases (real and ideal) there is some randomness in the middle region of the histogram. The signal applied at the input when building the histograms is in fact deterministic (triangular or sinusoidal waveforms), but we may consider it random because the number of samples used is very large (16 megasamples) and also the frequencies of the signal and of the clock were chosen to be incommensurate, to ensure that all the codes occur. Note that we are not interested in the time when a particular code occurs (this point of time cannot be considered random), but only in how often it occurs in a relatively long period of time.

However, two major differences can be noticed between the ideal and the real case. First, in the real case the lower and the upper bounds are not abrupt but rounded, which makes their accurate estimation a bit more difficult. This can be attributed to phenomena such as noise, hysteresis, drifts, and so on, which occasionally combine to push the residue outside of the nominal interval  $[m_k, M_k]$ .

Second, in the real case the middle region is not as flat as in the ideal case. The explanation lies in the nonidealities of the fine A/D subconverter: if the thresholds of this subconverter are different from the ideal values, we should not expect the bins to have the same height (since the bin height is proportional to the distance between the two thresholds that define the code of the bin). This suggests that the agreement between the residue and the bidimensional histogram is qualified by the linearity of the fine subconverter and it is this linearity that we should study first.

## 3.5 Fine A/D Subconverter Characterization

Residue bounds contain information about the errors in the amplifier A2, coarse A/D subconverter, and D/A subconverter, and will be used for the characterization of these components. On the other hand, the bounds do not contain any readily interpretable

information about the errors in the fine ADC, so a distinct method must be devised to evaluate them.

Code density tests provide part of the answer. If we had a histogram covering the whole range of the fine ADC, we would be able to estimate its errors, but such a histogram is not available. All we have are the columns of the bidimensional histogram, and there are two problems associated with them: most of them occupy only about half of the range (Figure 3.10, top), and there is a large amount of randomness in them, even for large data sets of 16 megasamples.

A solution to the latter problem is to increase the number of samples until the randomness is small enough compared to the expected bin heights. How many samples would be necessary? It can be easily demonstrated that if  $p_0$  is the probability of hitting a bin (e.g. for a uniform distribution and a 12-bit ADC,  $p_0$  is  $2^{-12}$ ) and n the number of samples, the expected value of the bin height is

$$\bar{h} = E[h] = np_0$$

(EQ 3.7)

and its variance is

$$\sigma_h = \sqrt{E[h^2 - E[h]^2]} = \sqrt{np_0(1-p_0)}$$

(EQ 3.8)

It follows that the coefficient of dispersion is

$$\frac{\sigma_h}{\bar{h}} = \sqrt{\frac{1-p_0}{np_0}} \tag{EQ 3.9}$$

(EQ 3.9) indicates that the accuracy is inversely proportional to square root of the number of samples. For instance, for a coefficient of dispersion of 1% we need 40 megasamples.

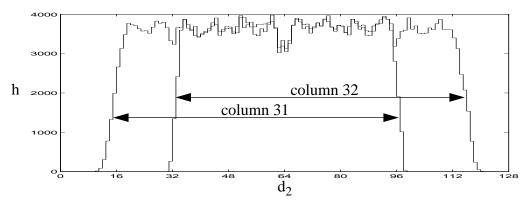

Getting so many samples can be a long and tedious task in the absence of automated test equipment. An alternative to increasing the number of samples is to use information not just from a single column, but from all the 64 columns. In Figure 3.11, two columns (31

FIGURE 3.11 Overlapped Columns of Bidimensional Histogram (Uniform pdf)

and 32) have been overlapped. It is easy to see that in the central region, the histograms follow the same pattern. In the case of a uniform pdf (for a triangular waveform), this is valid for all the columns, so we could simply average (the full bins in) the rows of the bidimensional histogram to get a more accurate estimate. Incidentally, this would also solve in part the other problem. Individual columns cover only half of the range, but some of them are shifted to the right, and some to the left, and combined together they cover more than half of the range.

However, if the input pdf is not uniform (e.g. for a sinusoidal waveform), we have the situation depicted in Figure 3.12. Although the columns seem to follow a similar pattern, there is a substantial difference between them, stemming from the fact that these columns correspond to different sections of the pdf of the input signal.

This dependence on the pdf must be removed from the histogram, before any averaging can take place. Just like in code density tests, this can be accomplished by normalizing the histogram with respect to the estimated pdf. A general solution (that works for any input

signal pdf) is to find a polynomial p(i) that fits the unidimensional histogram, in a least-squares sense. To normalize the unidimensional histogram, we would use

$$h_i^{norm} = \frac{h_i}{p(i)}$$

$i = 0...4095$  (EQ 3.10)

Taking into account the relationship between the unidimensional and the bidimensional histograms (see Section 3.3), we can normalize the latter using:

$$h_{i,j}^{norm} = \frac{h_{i,j}}{p(64i+j)}$$

$i = 0...63, j = 0...127$  (EQ 3.11)

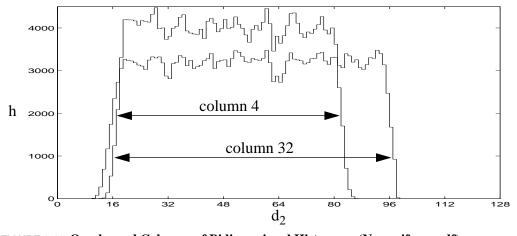

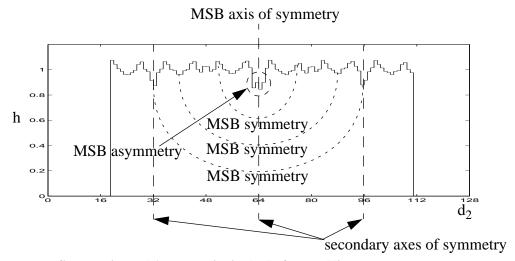

In the following we will assume that the bidimensional histogram has been normalized. In our calculations (in MATLAB), second-order polynomials have been used for p(i), since no improvement has been noticed for higher-order polynomials. The result of normalization and averaging is the reference histogram presented in Figure 3.13.

We explained in Section 2.6 that the errors in the A/D subconverters of the AD9042 fall into two categories: those which result in symmetrical changes on both sides of the vertical axis corresponding to the threshold, and those which result in asymmetrical changes in the codes next to the axis. The effect of these two categories of errors can be

FIGURE 3.12 Overlapped Columns of Bidimensional Histogram (Nonuniform pdf)

clearly seen in Figure 3.13. The left half (codes 0 to 63) is mirrored in the right half (codes 64 to 127), with respect to the MSB axis of symmetry  $d_2$ =63.5. Also the first quarter is mirrored in the second quarter, with respect to the secondary axis of symmetry  $d_2$ =31.5. The second quarter is mirrored into the third ( $d_2$ =63.5) which is mirrored into the fourth ( $d_2$ =95.5). In other words, bins x, 63-x, 64+x, and 127-x should be equal, where x ranges from 2 to 30. Only the codes next to the axes of mirroring are not symmetrical, which means that the relationship between the bins mentioned above is not valid for bins 62-65 (next to the MSB axis), bins 0-1 and 127-128 (which would have to be symmetric to those next to the MSB axis), and bins 31-32 and 95-96 (next to secondary axes of symmetry). In the case of the AD9042, we can use these symmetries to recreate the bins that were left empty because no column of the bidimensional histogram covered them. The final reference histogram for the AD9042 is shown in Figure 3.14.

However, most two-stage A/D converters use flash subconverters, in which case we have to make do with the histogram in Figure 3.13, since the other bins cannot be reconstructed.

FIGURE 3.13 Symmetries and Asymmetries in the Reference Histogram

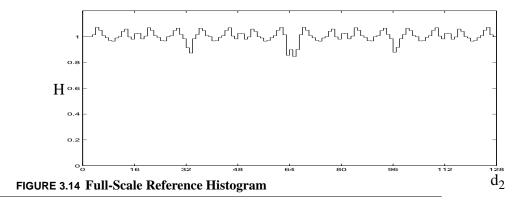

Note that the new histogram (Figure 3.14) covers the whole range of the fine ADC, and has significantly less randomness than the individual histogram columns from which it was created, because it contains information from all of them.

The next step is to apply the usual procedure from code density tests to the reference histogram, denoted here by H. We know that the bin height  $H_k$  is proportional to the difference between the thresholds that define the bin:

$$H_k = q \cdot (t_{2.k+1} - t_{2.k})$$

(EQ 3.12)

where q is a constant. Adding (EQ 3.12) for k from 0 to 127 we obtain:

$$\sum_{k=0}^{127} H_k = q \cdot (t_{2,128} - t_{2,0}) \tag{EQ 3.13}$$

$t_{2,128}$  and  $t_{2,0}$  are by definition  $128LSB_2$  and 0, respectively (see Section 2.4). q can be then calculated from (EQ 3.13) as:

$$q = \frac{\displaystyle\sum_{k=0}^{127} H_k}{t_{2.128} - t_{2.0}} \tag{EQ 3.14}$$

By replacing q in (EQ 3.12) and rearranging the terms, a formula for the thresholds of the fine subconverter can be derived:

$$\hat{t}_{2,\mathrm{k+1}} = \hat{t}_{2,\mathrm{k}} + H_k \cdot \frac{t_{2,128} - t_{2,0}}{127}$$

(EQ 3.15)

The results have been plotted in Figure 3.15. Only the estimated errors are presented, i.e. the deviations  $(\Delta \hat{t}_{2,\,k})$  of the estimated values  $(\hat{t}_{2,\,k})$  from the ideal values  $(\tilde{t}_{2,\,k}=k)$ . The top plot represents the difference between two consecutive errors, which is indicative of differential nonlinearity. One can verify that this plot is simply a scaled and offset version of Figure 3.14. The bottom plot is the cumulative sum of the differences shown in the top plot and is indicative of integral nonlinearity.

Note that the bottom plot has a different kind of symmetry from the top plot: the mirroring happens with respect not to a vertical axis but to a point. For instance, the left half is a mirrored version of the right half with respect to the point {63.5,0}. These symmetries are in good agreement with the expected behavior of the subconverter, as explained in Section 2.6.

The change corresponding to bit 6 (MSB) of the fine subconverter can be clearly seen at  $d_2$ =64. Also the changes corresponding to bit 5 are quite obvious at  $d_2$ =32 and  $d_2$ =96. Overall, these errors do not exceed +/-0.25  $LSB_2$ , and they must be taken into account when estimating the bounds of the histograms.

## 3.6 Histogram Smoothing

Now that the fine ADC has been characterized, out next goal is to characterize the coarse ADC, the DAC, and A2, based on residue bounds which can be estimated from histograms. Before proceeding to estimate them, it is necessary to remove from the histograms any distortions caused by the fine ADC errors. We call this procedure histogram smoothing.

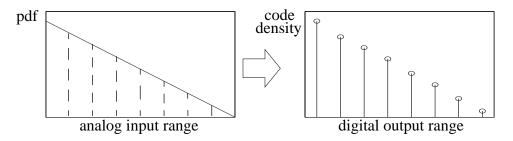

We have already talked briefly in Section 3.4 about the distortion of the histograms caused by the fine ADC. For an ADC with no threshold errors, the envelope of the histogram is proportional to the pdf, as depicted in Figure 3.16 (MATLAB simulations with a 100,000 samples from a signal with a triangular pdf). Note that we have represented the histograms using a stem representation, instead of the customary stairstep, in order to make the envelope obvious. It is easy to notice that the bins in the code density plot are proportional to the area delimited by two consecutive thresholds, marked on the pdf plot with vertical dashed lines.

FIGURE 3.17 Relationship between pdf and Histogram for ADC with Threshold Errors

In reality, the fine ADC suffers from threshold errors, as we have seen in the previous chapter. As a result, the histogram might not reflect accurately the pdf. Figure 3.17 illustrates this situation, with random threshold errors between -0.3 and 0.3 *LSB*. It is hard to believe that the histogram at the right actually originates from the pdf at the left, but this is indeed the case.

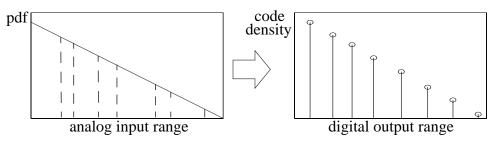

What we would need is a procedure to make the histogram agree better with the pdf, and this should not be too difficult since we have already calculated the errors that cause the distortion.

Let p(x) be the pdf, and  $t_k$  the thresholds of an ADC. If the number of samples is very large, we can estimate the bin height by:

FIGURE 3.16 Relationship between pdf and Histogram for Ideal ADC

$$h_k \cong const. \int_{t_k}^{t_{k+1}} p(x)dx$$

(EQ 3.16)

This formula can be approximated as

$$h_k \cong const.(t_{k+1} - t_k) \cdot p\left(\frac{t_k + t_{k+1}}{2}\right) \tag{EQ 3.17}$$

Therefore the bin height is set by the pdf at the midpoint between the two thresholds and the difference between the two thresholds.

(EQ 3.17) indicates that the histogram is in fact a plot of pairs

$$\left\{\frac{\tilde{t}_k + \tilde{t}_{k+1}}{2}, const.(t_{k+1} - t_k) \cdot p\left(\frac{t_k + t_{k+1}}{2}\right)\right\}.$$

On the other hand, the plot of the pdf

is made up of pairs  $\{x,p(x)\}$ . A comparison between the two forms suggests what we have to do to correct the distortion in the histogram. First we have to adjust the bin height

$$h_k \leftarrow h_k \cdot \frac{LSB}{\hat{t}_{k+1} - \hat{t}_k} \tag{EQ 3.18}$$

and then we have to adjust its position too. Instead of  $\frac{\tilde{t}_k + \tilde{t}_{k+1}}{2}$  we should put it at

$\frac{\hat{t}_k + \hat{t}_{k+1}}{2}$  (note that we are using estimated values, because this is all we have). The result

can be seen in Figure 3.18. Note that the bins are now at irregular intervals, but their envelope reflects the pdf with high accuracy.

FIGURE 3.18 Relationship between pdf and Smoothed Histogram for Real ADC

We can now apply this procedure to the columns of the bidimensional histogram, using the thresholds estimated in Section 3.5,  $(\hat{t}_{2,k})$ . An example of a smoothed histogram is shown in Figure 3.19.

There is still randomness in the histogram because we used a finite number of samples, but systematic errors have been eliminated, so that we can now go on to the next step.

Bound Estimation 46

## 3.7 Bound Estimation

After a histogram has been normalized and smoothed, the histogram bounds should coincide with the residue bounds. The last difficulty in estimating these bounds is the fact that they are rounded by noise.

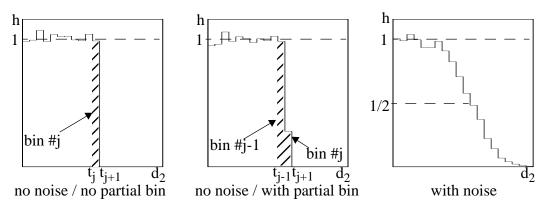

Histogram bounds without and with noise are depicted in Figure 3.20. In the noiseless case the estimation of the bounds is straightforward. If j is the rightmost full bin and j+1 is the empty bin next to it (Figure 3.20, left), we would estimate  $M_k$  as:

FIGURE 3.20 Histogram Bound without and with Noise

$$\hat{M}_k = \hat{t}_{i+1}$$

(EQ 3.19)

If there is a partial bin after the last full bin, the estimate would be

$$\hat{M}_k = \hat{t}_j + \frac{h_j}{\bar{h}}(\hat{t}_{j+1} - \hat{t}_j)$$

(EQ 3.20)

where  $h_j$  is the height of bin j and  $\bar{h}$  is the average bin height. It is easy to see that when  $h_j$  goes to zero (partial bin almost empty) the estimate  $\hat{M}_k$  goes to  $\hat{t}_j$ , and when  $h_j$  goes to  $\bar{h}$  (partial bin almost full) the estimate  $\hat{M}_k$  goes to  $\hat{t}_{j+1}$ , which agrees with (EQ 3.19).

Bound Estimation 47

This formula does not work any more for the case with noise.  $M_k$  is probably located somewhere between the last full bin (i.e. bin not affected by rounding) and the first empty bin.

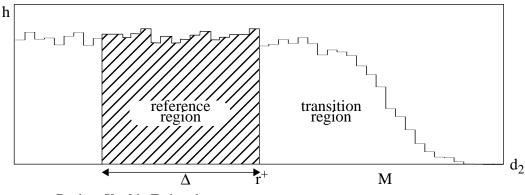

There are a number of solutions to this problem, all of which assume that the noise is additive and has symmetric pdf. The solution presented here is based on the observation that in the presence of noise, if there were a bin centered exactly at the bound, its height would be about 1/2 (see Figure 3.20, right), i.e. half of the average bin height which is 1 because the histogram has been normalized.

Let us approximate the shape of the transition region with a polynomial f using the least-squares method, so as to minimize

$$\sum_{j_{1}}^{j_{2}} \left( f\left(\frac{\hat{t}_{j} + \hat{t}_{j+1}}{2}\right) - h_{j} \right)^{2}$$

where  $j_1$  and  $j_2$  are the limits of the transition region, and  $j_2$  -  $j_1$  is typically 7-8  $LSB_2$ . A low order polynomial (second- or third-order) has to be used to ensure that the randomness is averaged out. Regardless of the noise level, the value of the polynomial calculated at the actual bound  $M_k$  should be equal to 1/2, so that

$$\hat{M}_k = \left\{ x, f(x) = \frac{1}{2} \right\}$$

(EQ 3.21)

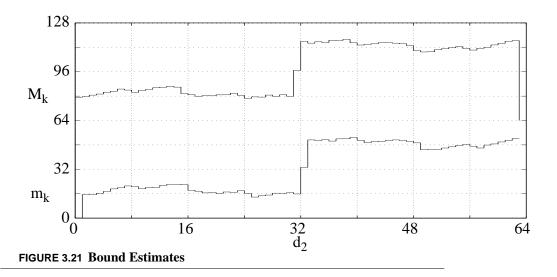

A similar approach can be used to estimate the lower bounds,  $m_k$ . The estimates of the upper and lower bounds thus obtained are shown in the figure below. The reader is urged to compare Figure 3.21 to Figure 3.5. The former is in fact the estimated contour of the latter, and they are in good agreement.

Bound Estimation 48

We also need to know the variance of these estimates, preferably expressed in  $LSB_2$ . Finding a mathematical formula is quite a difficult task, so we preferred an empirical approach. We used N=16 sets of 1 megasample derived from the same input signal, calculated the bound estimates for each of them, and then estimated the variance of the population of bound estimates:

$$\sigma_M(1Meg) = \sqrt{\frac{\sum_N (\hat{M}_k - \overline{\hat{M}_k})^2}{N-1}}$$

(EQ 3.22)

This is valid for 1 megasample and must be divided to  $\sqrt{N}$  for N megasamples. The resulting variance for 16 megasamples is less than 0.1 LSB<sub>2</sub>.