# Computational RAM: Implementation and Bit-Parallel Architecture

by

Christian Cojocaru

A thesis submitted to the

Faculty of Graduate Studies and Research

in partial fulfilment of the requirements

for the degree of

Master of Engineering

Ottawa-Carleton Institute for Electrical Engineering

Department of Electronics

Carleton University

Ottawa, Ontario

Canada K1S 5B6

January 1995 Copyright 1995, Christian Cojocaru

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Tour fee butter interess e

Life friet. Witten fenfengern en

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive la permettant à Bibliothèque nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette à disposition la des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-08957-6

CHRISTIAN COJOCARU

Dissertation Abstracts International is arranged by broad, general subject categories. Please select the one subject which most nearly describes the content of your dissertation. Enter the corresponding four-digit code in the spaces provided.

CONFINENCE FARE HAPLETARY FOR MAD SUBJECT TERM TO PARALLEL ARCHAT CALICL

#### **Subject Categories**

Physical

Biogers hemistrs

# THE HUMANITIES AND SOCIAL SCIENCES

| COMMUNICATIONS AND TH       | E ARTS       | Psychology               | 0525 | PHILOSOPHY, RELIGION AND |      | Ancient                             | 0579         |

|-----------------------------|--------------|--------------------------|------|--------------------------|------|-------------------------------------|--------------|

| Architecture                | 0729         | Peading                  | 0535 | THEOLOGY                 |      | Medieval                            | 0581<br>0582 |

| Art History                 | 0377         | Religious                | 0527 | Philosophy               | 0422 | Modern<br>No                        | 0328         |

| Cinerra 2                   | <u> </u>     | Sciences                 | 0714 | Religion                 |      | Black                               | 0331         |

| Dance                       | 0378         | Secondary                | 0533 | General                  | 0318 | African Asia, Australia and Oceania |              |

| Fine Arts                   | 0357         | Social Sciences          | 0534 | Biblical Studies         | 0321 |                                     | 0334         |

| Information Science         | 0723         | Socialogy of             | 0340 | Clergy                   | 0319 | Canadian                            | 0335         |

| Journalism                  | 0391         | Special                  | 0529 | History of               | 0320 | European                            | 0336         |

| Library Science             | 0399         | Teacher Training         | 0530 | Philosophy of            | 0322 | Latin American<br>Middle Eastern    | 0333         |

| Mass Communications         | 6708         | Technology               | 0710 | Theology                 | 0469 | United States                       | 0337         |

| Masi                        | 0413         | Tests and Measurements   | 0288 | •                        |      | History of Science                  | 0585         |

| Merch Communication         | 0459         | Vocational               | 0747 | SOCIAL SCIENCES          |      | Law                                 | 0398         |

| i water                     | 0465         |                          |      | American Studies         | 0323 | Political Science                   | 03/0         |

| 1,112,11                    |              | LANGUAGE, LITERATURE AND |      | Anthropology             |      | Ge. al                              | 0615         |

| EDUCATION                   |              | LINGUISTICS              |      | Archaeology              | 0324 | International Law and               | 00.5         |

| Commerci                    | 0515         | Language                 |      | Cultural                 | 0326 | Relations                           | 0616         |

| Administration              | 0514         | General                  | 0679 | Physical                 | 0327 | Public Administration               | 0617         |

| Adult and Continuing        | 0516         | Ancient                  | 0289 | Business Administration  |      | Recreation                          | 0814         |

| Agricultural                | 0517         | Linguistics              | 0290 | General Control          | 0310 | Social Work                         | 0452         |

| Ari                         | 0273         | Modern                   | 0291 | Accounting               | 0272 | Sociology                           | •            |

| Bilingual and Multicultural | 0282         | Literature               |      | Banking -                | 0770 | General                             | 0626         |

| Business                    | 0688         | General                  | 0401 | Managemen!               | 0454 | Criminalogy and Penology            | 0627         |

| Community College           | 0275         | Classical                | 0294 | Marketing                | 0338 | Demography                          | 0938         |

| Curriculum and Instruction  | 0727         | Comparative              | 0295 | Canadian Studies         | 0385 | Ethnic and Racial Studies           | 0631         |

| Early Childhood             | 0518         | Medieval                 | 0297 | Economics ,              | 0501 | Individual and Family               |              |

| Elementary                  | 0524         | Modern                   | 0298 | General                  | 0501 | Studies                             | 0628         |

| finance                     | 02/7         | African                  | 0316 | Agricultural             | 0503 | Industrial and Labor                |              |

| Guidance and Couriseling    | 0519         | American                 | 0591 | Commerce Business        | 0505 | Relations                           | 0629         |

| Health                      | 0580         | Asian                    | 0305 | Finance                  | 0508 | Public and Social Welfare           | 0630         |

| Higher ,                    | 0745         | Canadian (English)       | 0352 | History                  | 0509 | Social Structure and                |              |

| History_of                  | 0520         | Canadian (French)        | 0355 | <u>f</u> apor            | 0510 | Development                         | 0700         |

| Home Economics              | 0278         | English                  | 0593 | Theory                   | 0511 | Theory and Methods                  | 0344         |

| Industrial                  | 0521         | Germanic                 | 0311 | folklore                 | 0358 | Transportation                      | 0709         |

| Language and Literature     | 0279         | Latin American           | 0312 | Geography                | 0366 | Urban and Regional Planning         | 0999         |

| Mathematics                 | 0280         | Middle Eastern           | 0315 | Gerontology              | 0351 | Women's Studies                     | 0453         |

| Music                       | 0522<br>0998 | Romance                  | 0313 | History                  | 0578 |                                     |              |

| Philosophy of               | 0523         | Slavic and East European | 0314 | General                  | 02/6 |                                     |              |

#### THE SCIENCES AND ENGINEE

0425

Radiology Recreation

| INE OCIENCES          | AND   | EMAINTERING               |               |                             |      |                            |             |

|-----------------------|-------|---------------------------|---------------|-----------------------------|------|----------------------------|-------------|

| BIOLOGICAL SCIENCES   |       | Geodesy                   | 0370          | Speech Pathology            | 0460 | Engineering                | 0537        |

| Agriculture           |       | Geology                   | 0372          | Toxicology                  | 0383 | General                    | 0538        |

| General               | 0473  | Geophysics                | 0373          | Home Economics              | 0386 | Aerospace                  | 0539        |

| Agronomy              | 0285  | Hydrology                 | 03 <b>8</b> 8 | CHINCHES CEITHETS           |      | Agricultural               | 0540        |

| Animal Culture and    |       | Mineralogy                | 0411          | PHYSICAL SCIENCES           |      | Automotive                 | 0541        |

| Natrition             | 0475  | Paleobotány               | 0345          | Pure Sciences               |      | Biomedical<br>Chemical     | 0542        |

| Animal Pathology      | 0476  | Paleoecology Paleoecology | 0426          | Chemistry                   |      | Civil                      | 0543        |

| Food Science and      |       | Paleontology              | 0418          | General                     | 0485 | Electronics and Electrical | 0544        |

| Technology            | 0359  | Paleozoology              | 0985          | Agricultural                | 0749 | Heat and Thermodynamics    | 0348        |

| Forestry and Wildlife | 0478  | Palynology                | 0427          | Analytical                  | 0486 | Hydraulic                  | 0545        |

| Plant Culture         | 0479  | Physical Geography        | 0368          | Biochemistry                | 0487 |                            | 0546        |

| Plant Pathology       | 0480  | Physical Oceanography     | 0415          | Inorganic                   | 0488 | Industrial<br>Marine       | 0547        |

| Plant Physiology      | 0817  |                           |               | Nuclear                     | 0738 | Materials Science          | 0794        |

| Range Management      | 0777  | HEALTH AND ENVIRONMENTA   | Ĺ             | Organic                     | 0490 | Mechanical                 | 0548        |

| Wood Technology       | 0746  | SCIENCES                  |               | Pharmaceutical              | 0491 |                            | 0743        |

| Biology               |       | Environmental Sciences    | 0768          | Physical                    | 0494 | Metallurgy                 | 0551        |

| General               | 0306  | Health Sciences           | 0, 30         | Polymer                     | 0495 | Mining<br>Nuclear          | 0552        |

| Anatomy               | 0287  | General                   | 0566          | Radiation                   | 0754 |                            | 0549        |

| Biostotistics         | 0308  | Audrology                 | 0300          | Mathematics                 | 0405 | Packaging<br>Petroleum     | 0765        |

| Botony                | 01.5  | Chemotherapy              | 0992          | Physics                     |      | Sanitary and Municipal     | 0554        |

| ( ell                 | 03/9  | Dentistry                 | 0567          | General                     | 0605 | System Science             | 0790        |

| tiology               | 0329  | Education                 | 0350          | Acoustics                   | 0986 | Geotechnology              | 0428        |

| Entomology            | 0353  | Hospital Management       | 0769          | Astronomy and               |      | Operations Research        | 0796        |

| Conclus               | 0.369 | Human Development         | 0758          | Astrophysics                | 0606 | Plastics Technology        | 0795        |

| Limitalous            | 0*93  | Immunology                | 0982          | Atmospheric Science         | 0608 | Textile Technology         | 0994        |

| Microbiology          | 0410  | Medicine and Surgery      | 0564          | Atomic                      | 0748 | Textile Technology         | 0,,,        |

| Molecular             | 0307  | Mental Health             | 0347          | Electronics and Electricity | 0607 | PSYCHOLOGY                 |             |

| Neuroscience          | 0317  | Nursing                   | 0569          | Elementary Particles and    | •    | General                    | 0621        |

| Channography          | 0416  | Nutrition                 | 0570          | High Energy                 | 0798 | Behavioral                 | 0384        |

| Physiology            | 0433  | Obstetrics and Gynecology | 0380          | Fluid and Plasma            | 0759 | Clinical                   | 0622        |

| Radiation             | 0821  | Occupational Health and   | 5555          | Molecular                   | 0609 | Developmental              | 0620        |

| Veterinary Science    | 0778  | Therapy                   | 0354          | Nuclear                     | 0610 | Experimental               | 0623        |

| (Aslead)              | 04*2  | Ophthalmology             | 0381          | Optics                      | 0752 | Industrial                 | 0624        |

| Buckilly on &         |       | Pathology                 | 0571          | Radiation                   | 0756 | Personality                | 0625        |

| Calculated            | 0786  | Pharmacology              | 0419          | Solid State                 | 0611 | Physiological              | 0989        |

| Medical               | 0760  | Pharmacy                  | 0572          | Statistics                  | 0463 | Psychobiology              | 0349        |

|                       |       | Physical Therapy          | 0382          | * * * .                     |      |                            | 0632        |

| EARTH SCIENCES        |       | Public Health             | 0573          | Applied Sciences            |      | Psychometrics              | 0451        |

| Reserve homistry      | 0425  | D = 4 - 1                 | 0574          | Applied Mechanics           | 0346 | Social                     | <del></del> |

# The undersigned recommend to the Faculty of Graduate Studies and Research acceptance of the thesis

Computational RAM: Implementation and Bit-Parallel Architecture

submitted by Christian Cojocaru, Dipl.Eng. in partial fulfilment of the requirements for the degree of Master of Engineering

Thesis Supervisor

Chairman,

Department of Electronics

Ottawa-Carleton Institute for Electrical Engineering

Department of Electronics

Faculty of Engineering

Carleton University

January 9, 1995

#### **Abstract**

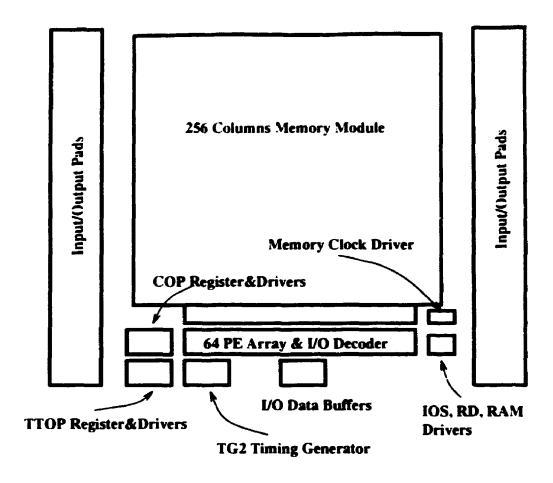

Computational RAM (C\*RAM) was previously proposed as a low-cost Single Instruction Multiple Data computing architecture integrating simple processing elements (PE) into a semiconductor memory circuit. The work presented in this thesis advances the C\*RAM project in two directions. First, a 64 processor array was designed and integrated with a 64 kbit ASIC memory module in a 0.8 µm triple-metal BiCMOS technology. Interdependent circuit and physical design have led to a dense PE array, taking 2.7% of the memory area. Functional C\*RAM chips have been tested, allowing the project to continue with system and application work. Second, a novel bit-parallel oriented PE architecture is proposed and a 512 PE Parallel Computational RAM (PC\*RAM) is designed and implemented. The new PE array can execute bit-parallel add/subtract, comparison and shift-and-add integer multiplication on programmable length words. All bit-parallel operations are performed without intermediate memory access, resulting in speed, power consumption and system interface advantages over the more traditional bit-serial SIMD approach.

#### Acknowledgments

Part of the direct financial support for this project was provided by Micronet, a National Centres of Excellence programme of the Natural Sciences and Engineering Research Council of Canada (NSERC). Integrated circuit fabrication was provided by Northern Telecom Electronics (NTE), both directly and through the Canadian Microelectronics Corporation (CMC). CMC also supplied design software and cell libraries. Test equipment was supplied by NSERC through their Industrial Research Chair programme. I would like to gratefully acknowledge the support of these organizations.

The collaboration with the Memory Design Group in Bell-Northern Research allowed this project to attain real-life dimensions. I would like to thank David Somppi for his support and Randall Gibson for very useful technical discussions.

Duncan Elliott from University of Toronto has introduced me to his Computational RAM world, with brief but dense and challenging e-mail messages. I hope his pioneering work will graduate someday into a real technology product.

I would like to mention here the very enjoyable atmosphere in the Department of Electronics at Carleton University, with too many friends to list. Dave Skoll served as a walking manual for the IC design software. Luc Lussier helped with test board design and examples on how to make things happen. Dr. Martin Lefebvre supervised my initial layout work. Thanks to all.

I had the great opportunity to have Dr. Martin Snelgrove as supervisor. His capacity to synchronize on my sometimes sketchy ideas on very short notice, understand them and suggest alternatives was essential in guiding this work in the right direction. I would like to thank Martin for his talent to communicate his vast electronics (but not only) knowledge, and for his admirable patience and generosity in helping his students.

Finally, I would like to express my heartfelt gratitude to my parents, Ecaterina and Dan. They have left their home in Romania to recreate its familiar atmosphere here, helping me to concentrate on my studies as they did for so many years.

# **Contents**

| 1 Introduction to C*RAM                                       | 1  |

|---------------------------------------------------------------|----|

| 1.0 The C*RAM Concept                                         | 1  |

| 1.1 Conventional Computers and Integrated Circuits Technology | 3  |

| 1.2 Parallel Computers - Brief Overview                       | 3  |

| 1.3 Semiconductor Memory as an IC Category                    | 5  |

| 1.4 C*RAM - An SIMD-IC Memory Hybrid                          | 6  |

| 1.5 Computational RAM History                                 | 7  |

| 1.6 Thesis Contributions                                      | 7  |

| 1.7 Thesis Organization                                       | 8  |

| 2 SIMD and Semiconductor Memory                               | 10 |

| 2.1 Single Instruction Multiple Data (SIMD) Computers         | 10 |

| 2.2 SIMD Machines Similar to C*RAM                            | 12 |

| 2.2.1 The AIS-5000 Parallel Processor                         | 13 |

| 2.2.2 The SRC Processor-In-Memory (PIM)                       | 13 |

| 2.2.3 The NEC Integrated Memory Array Processor (IMAP)        | 14 |

| 2.3 SRAM and DRAM                                             | 16 |

| 2.3.1 Static Random Access Memory (SRAM)                      | 16 |

| 2.3.2 Dynamic Random Access Memory (DRAM)                     | 18 |

| 2.4 C*RAM Economics                                           | 20 |

| 2.4.1 DRAM Economics                                          |    |

| 2.4.2 C*RAM Area and Yield Issues                             | 21 |

| 3 Processing Element Circuit and Physical Design      | 24  |

|-------------------------------------------------------|-----|

| 3.0 Introduction                                      | 24  |

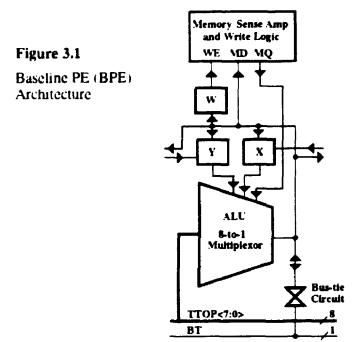

| 3.1 Architecture of the Baseline Processing Element   | 24  |

| 3.1.1 Communication between PEs                       | 26  |

| 3.1.2 Conditional Execution Support                   | 28  |

| 3.1.3 Baseline PE Control Lines                       | 29  |

| 3.2 Processing Element CMOS Circuit Design - Strategy | 30  |

| 3.3 8-to-1 Multiplexor ALU                            | 31  |

| 3.3.0 Circuit Alternatives                            | 31  |

| 3.3.1 Logic and Physical Order of the Selection Lines | 37  |

| 3.3.2 ALU Transistor Sizing                           | 38  |

| 3.3.3 ALU Layout                                      | 4() |

| 3.4 ALU-Register Loop                                 | 43  |

| 3.5 Register Design                                   | 45  |

| 3.5.1 Shift-Left/Right Implementation                 | 46  |

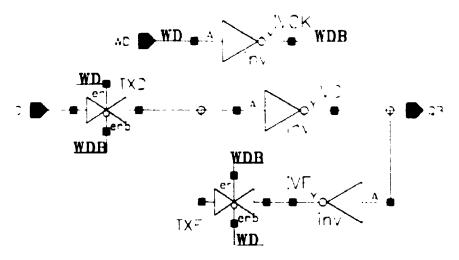

| 3.5.2 Dual-Access Latch                               | 47  |

| 3.5.3 Dual-Access Latch Transistor Sizing             | 49  |

| 3.5.4 Single-Access Latch Transistor Sizing           | 51  |

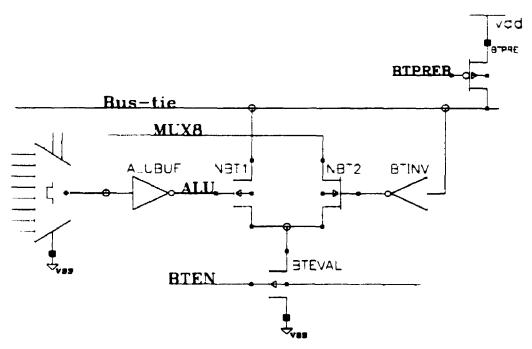

| 3.5 Bus-tie Circuit Implementation                    | 53  |

| 3.6.1 Circuit Alternatives                            | 53  |

| 3.6.2 Proposed Bus-tie Circuit Implementation         | 56  |

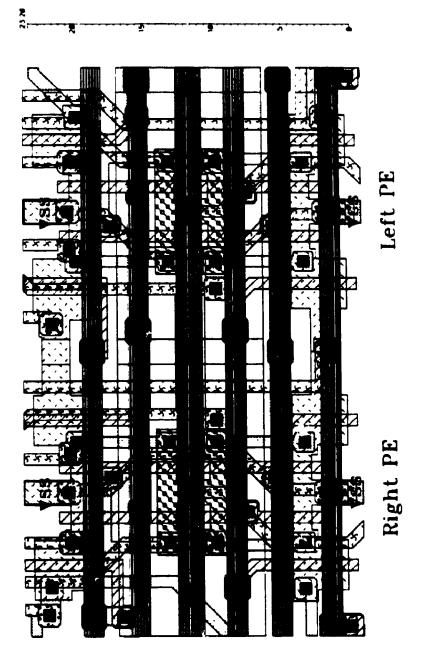

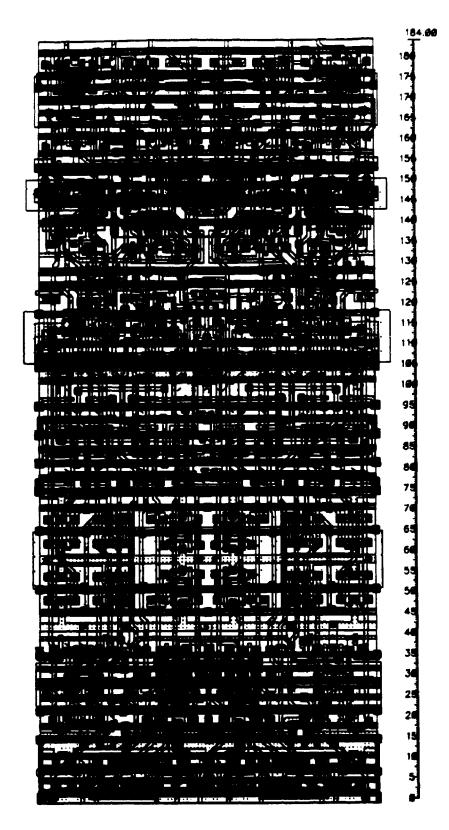

| 3.7 Processing Element Layout                         |     |

| 3.8 Summary                                           | 65  |

| 4 BATMOS Computational RAMs                           | 66  |

| 4.0 Using a Platform RAM                              | 66  |

| 4.1 BNR's Modular SRAM                                | 67  |

| 4.1.1 SRAM Modularity Parameter for C*RAM             | 68  |

| 4.2 C*RAM Data Input/Output                           | 70  |

| 4.2.1 Output Data Circuitry                           |     |

| 4.2.2 Input Data Circuitry                            |     |

| 4.2.3 Input/Output Buffers                            |     |

W TOO BE THE COME WIND DOOR OF WHITE IT WE HAVE BEEN AND A CONTROL OF THE CONTROL

|            | 4.3 C*RAM Instruction Multiplexing                           | 78  |

|------------|--------------------------------------------------------------|-----|

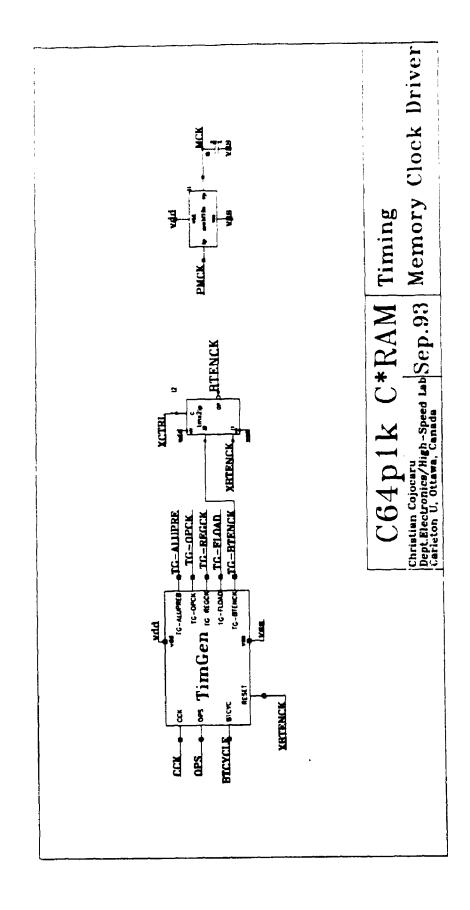

|            | 4.4 Timing Generation                                        | 80  |

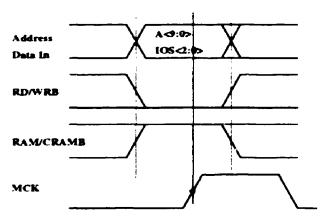

|            | 4.4.1 External Timing                                        | 8() |

|            | 4.4.2 Internal Timing Circuitry                              | 81  |

|            | 4.4.3 Timing Generation in the 512 PE C*RAM                  | 83  |

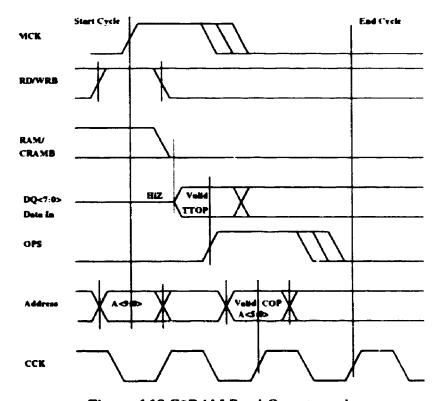

|            | 4 5 64 PE C*RAM Cycles                                       | 86  |

|            | 4.5.1 Memory Write Cycle                                     | 86  |

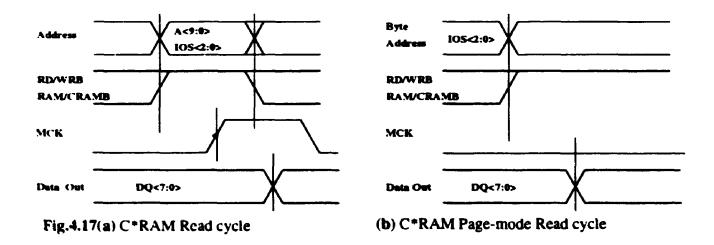

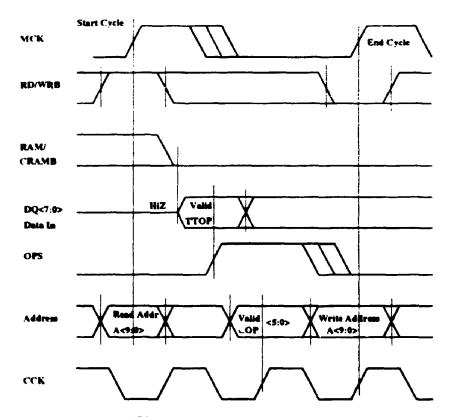

|            | 4.5.2 Memory Read and Page-mode Read Cycles                  | 86  |

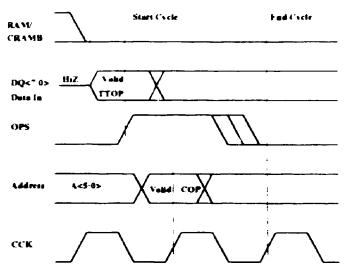

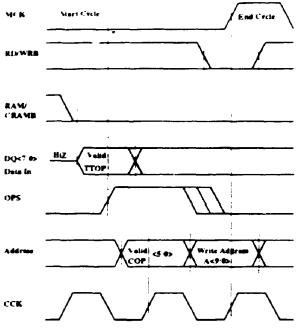

|            | 4.5.3 C*RAM Operate Cycle                                    | 87  |

|            | 4.5.4 Read-Operate Cycle                                     | 87  |

|            | 4.5.5 Operate-Write Cycle                                    | 88  |

|            | 4.5.6 Read-Operate-Write Cycle                               | 88  |

|            | 4.6 Synopsis of BATMOS Computational RAMs                    | 89  |

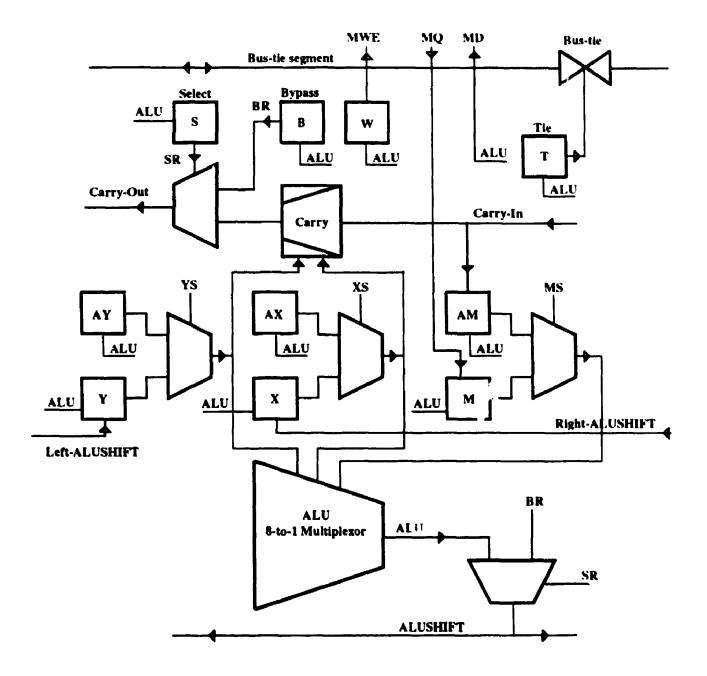

| <b>5</b> 7 | The Bit-Parallel Oriented Processing Element                 | 91  |

|            | 5.0 Motivation                                               | 91  |

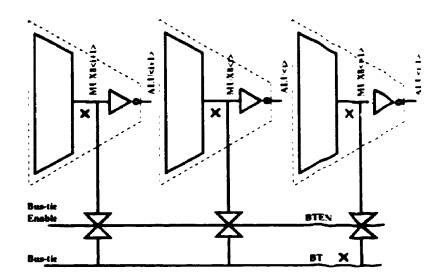

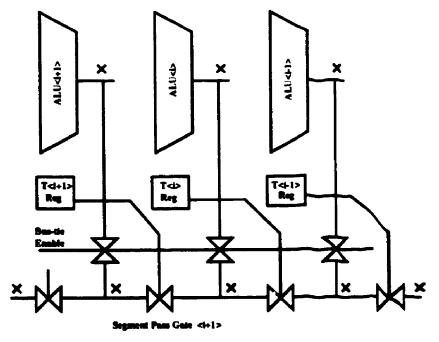

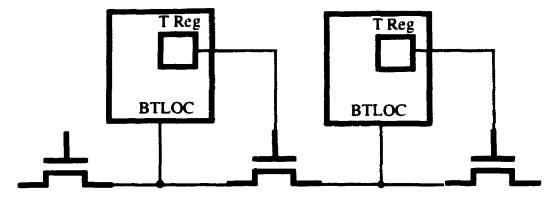

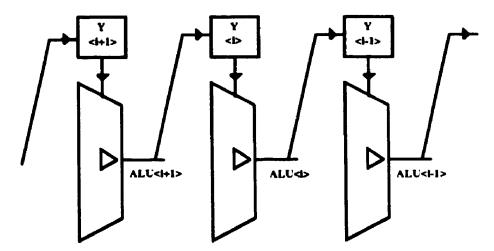

|            | 5.1 Programmable Segments Bus-tie (PSB) Network              | 92  |

|            | 5.1.1 Use of the Programmable Segments Bus-tie               | 94  |

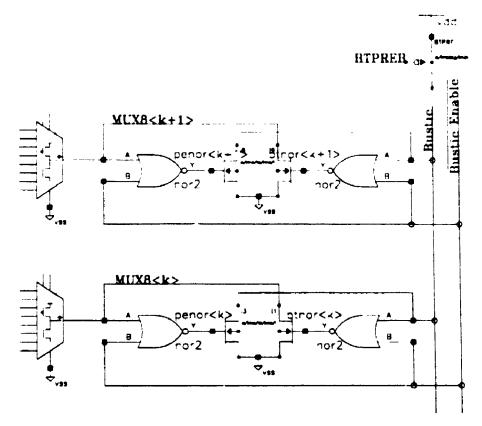

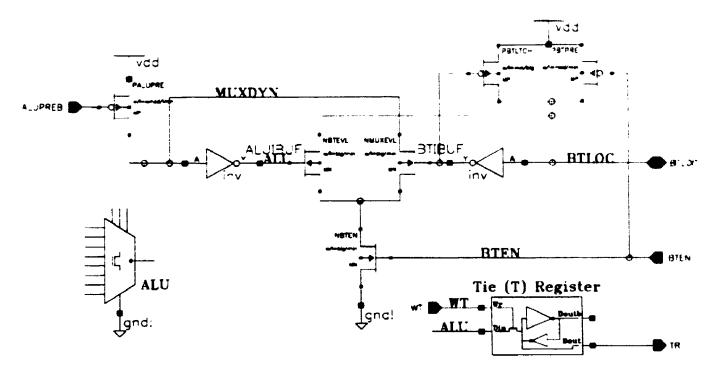

|            | 5.1.2 Circuit Implementation                                 | 96  |

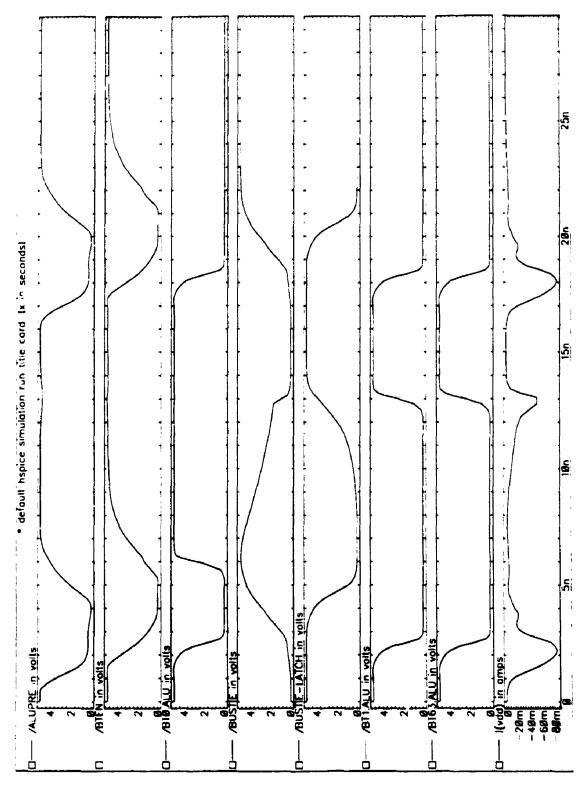

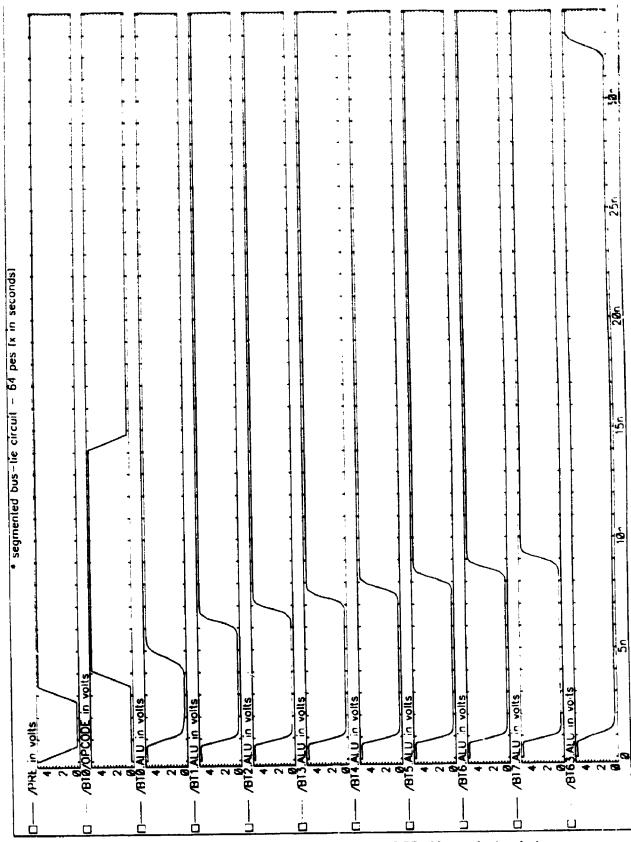

|            | 5.1.3 PSB Simulation                                         | 98  |

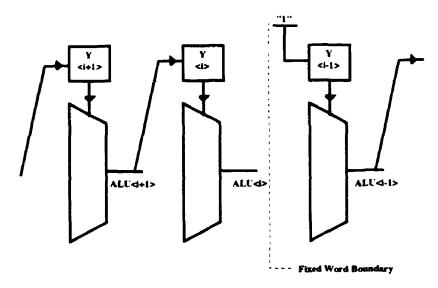

|            | 5.2 Shift Operations with Word Boundaries                    | 01  |

|            | 5.2.1 Circuit Implementation                                 | 03  |

|            | 5 3 Dedicated Add/Subtract Ripple-Carry Circuit              | 04  |

|            | 5.3.1 Ripple-Carry Circuit Implementation                    | 07  |

|            | 5.3.2 Ripple-Carry Chain Simulation                          | 09  |

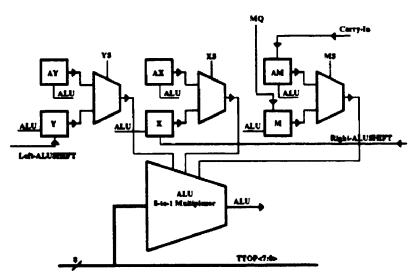

|            | 5.4 Bit-Parallel Integer Multiplication with the Extended PE | 13  |

|            | 5.4.1 Extended Register Set                                  | 13  |

|            | 5.4.2 Bit-Parallel Multiply Example                          | 17  |

|            | 5.4.3 Signed Multiply                                        |     |

|            | 5.4.4 Bit-Parallel Multiply Execution Time                   |     |

|            | 5.5 System Advantages of Bit-Parallel C*RAM                  |     |

|            | 5.6 Summary                                                  |     |

|            | •                                                            |     |

| 6 C*RAM Testing                                    | 125   |

|----------------------------------------------------|-------|

| 6.0 Introduction                                   | 126   |

| 6 1 Test Setup Hardware                            | . 126 |

| 6.1.1 C*RAM Test Board                             | . 128 |

| 6.2 Test Software                                  | . 129 |

| 6.2.1 C*RAM Testing with the CRAMTest Program      | 130   |

| 6.2.2 Automatic Memory Testing                     | 131   |

| 6.3 Test Results                                   | 131   |

| 7 Proposed Developments and Conclusions            | 132   |

| 7.1 Independent PE Addressing                      | . 132 |

| 7.1.1 Proposed Solution - Dual-Mode Column Decoder | . 133 |

| 7.2 Future C*RAM Work                              | . 134 |

| 7.2.1 Processing Element and C*RAM Architecture    | . 135 |

| 7.2.2 C*RAM System Hardware                        | . 135 |

| 7.2.3 C*RAM Software                               | . 136 |

| 7.3 Conclusions                                    | . 137 |

| Bibliography                                       | 138   |

| Appendices                                         | 142   |

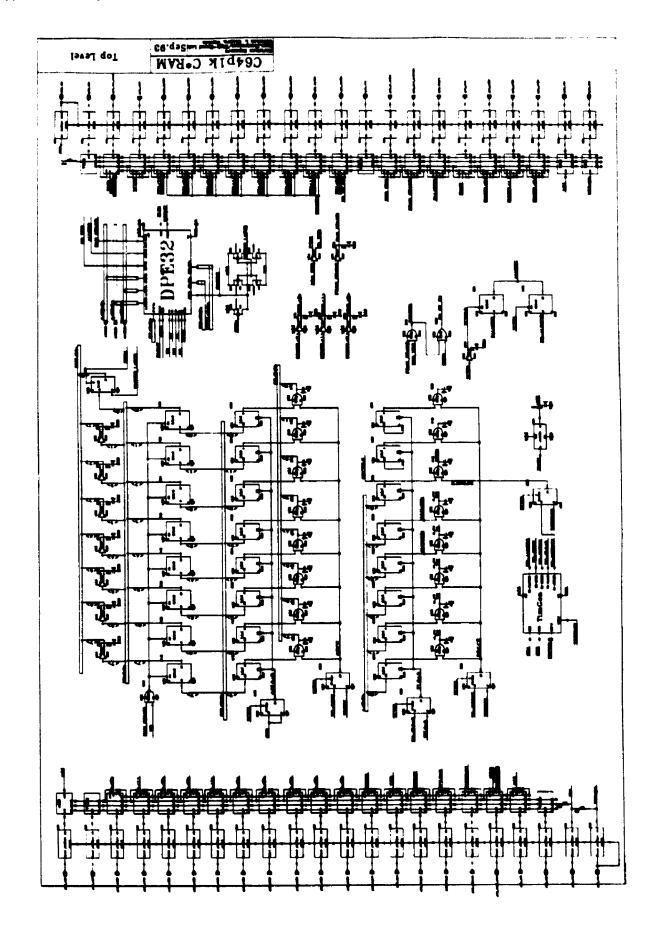

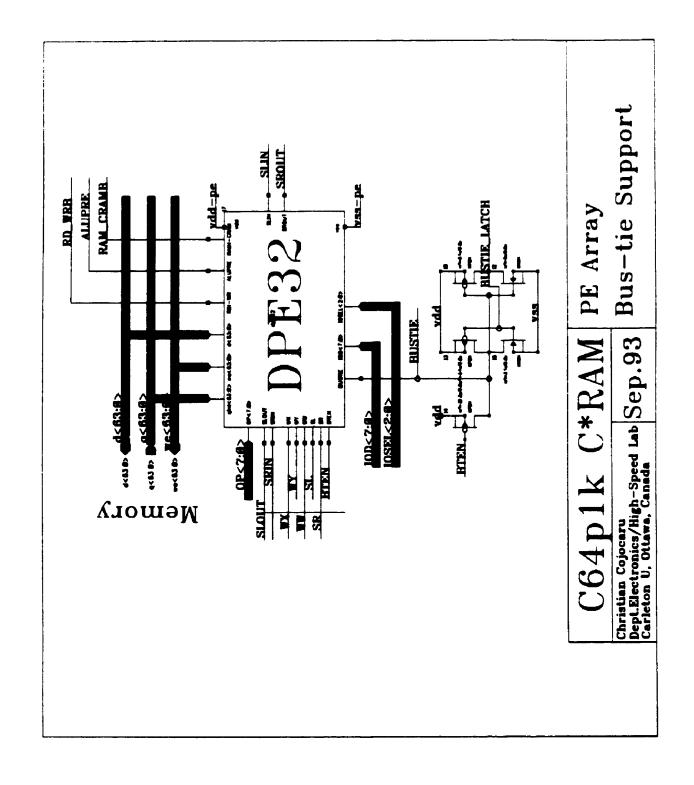

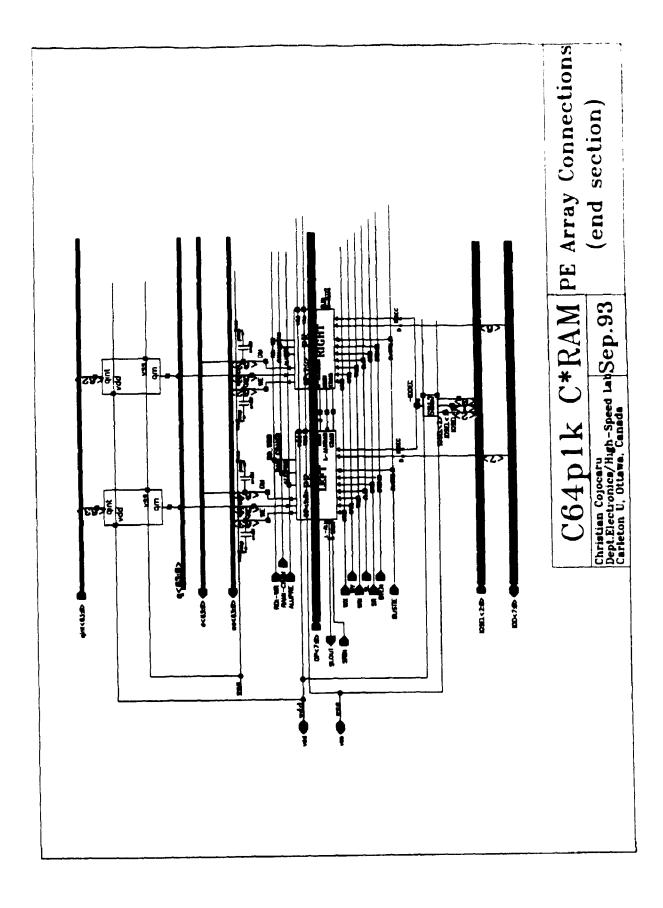

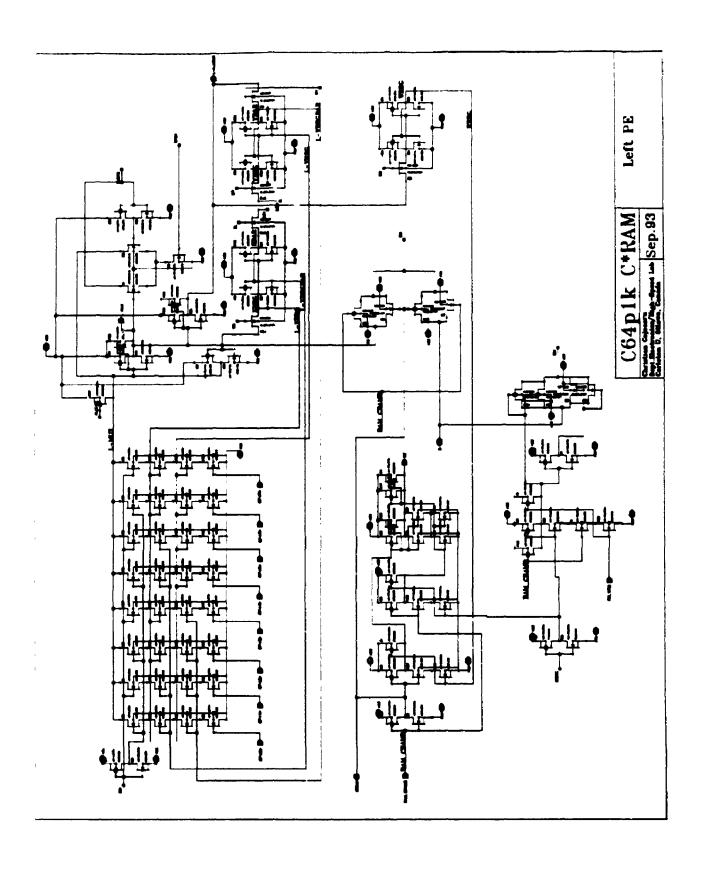

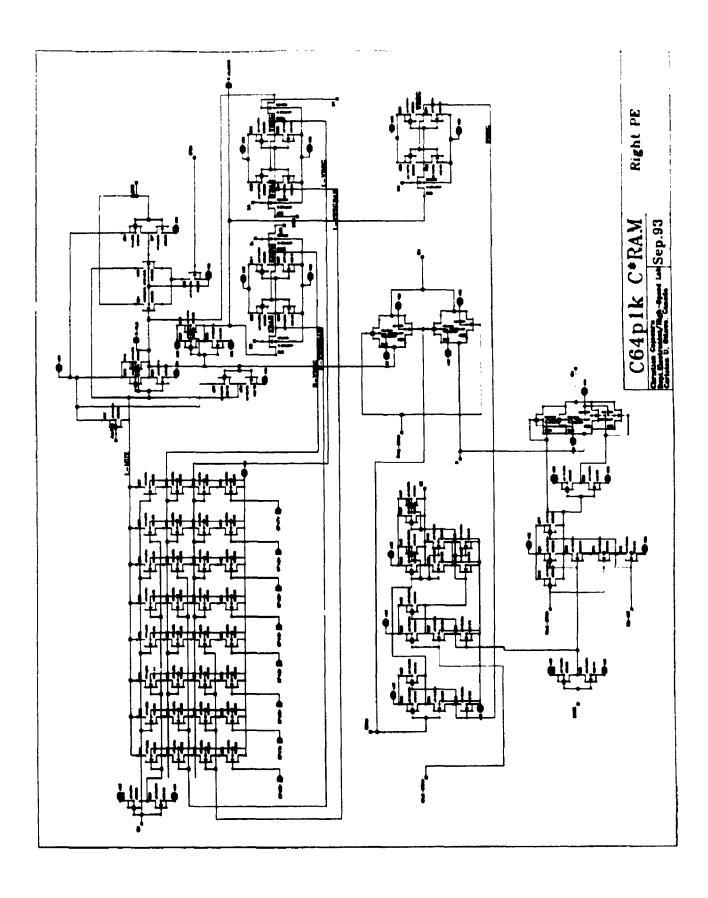

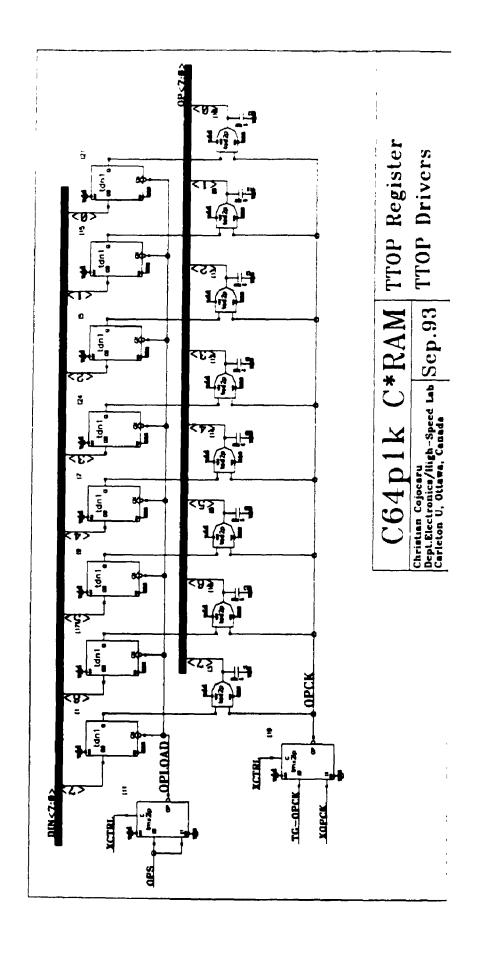

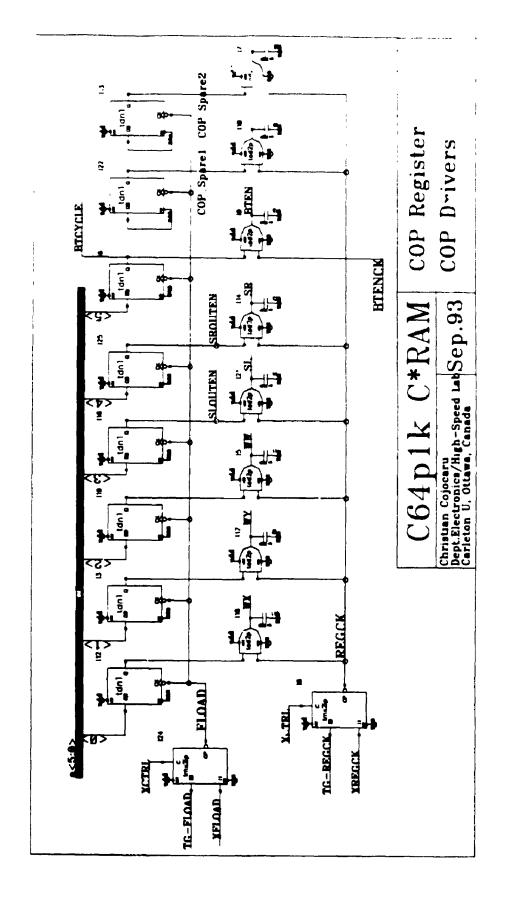

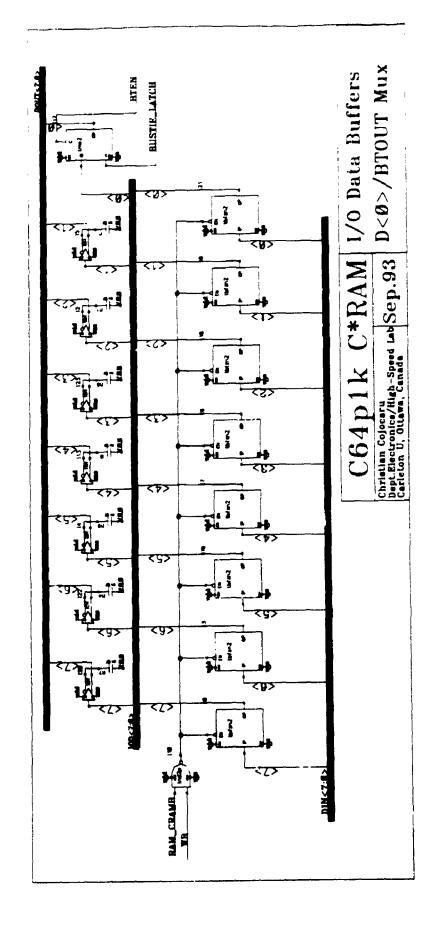

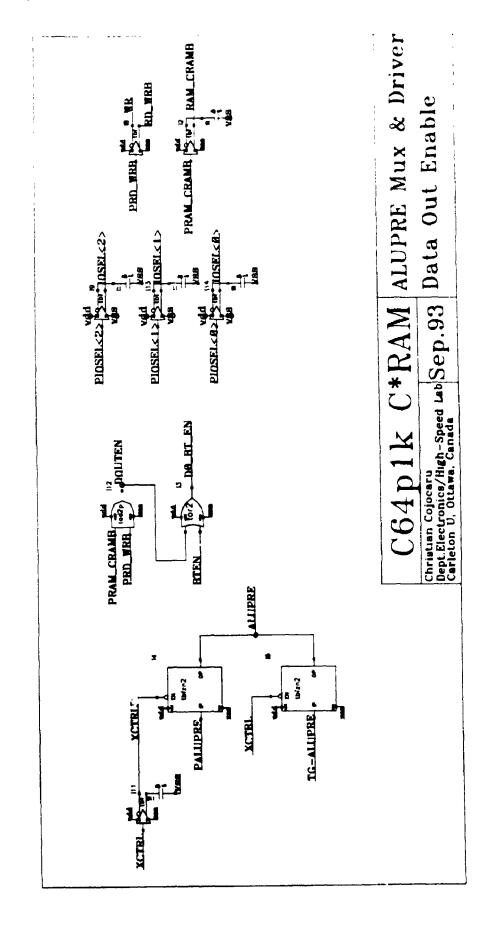

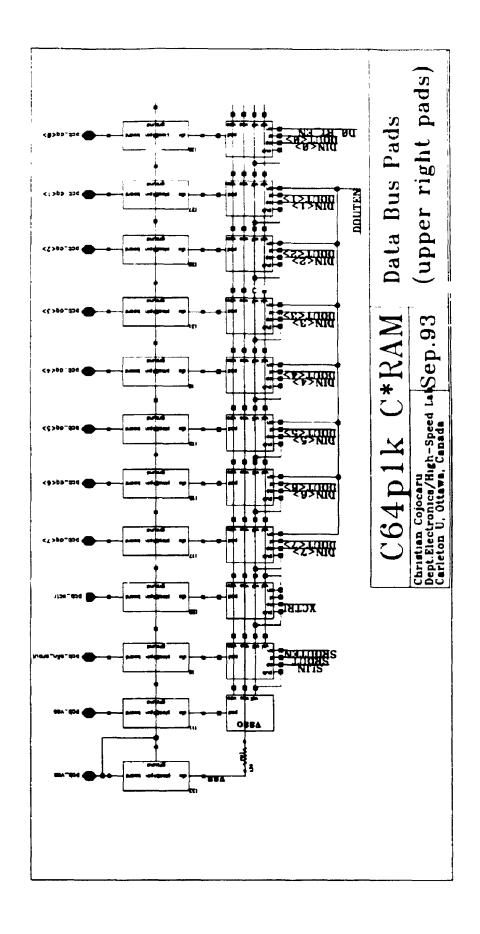

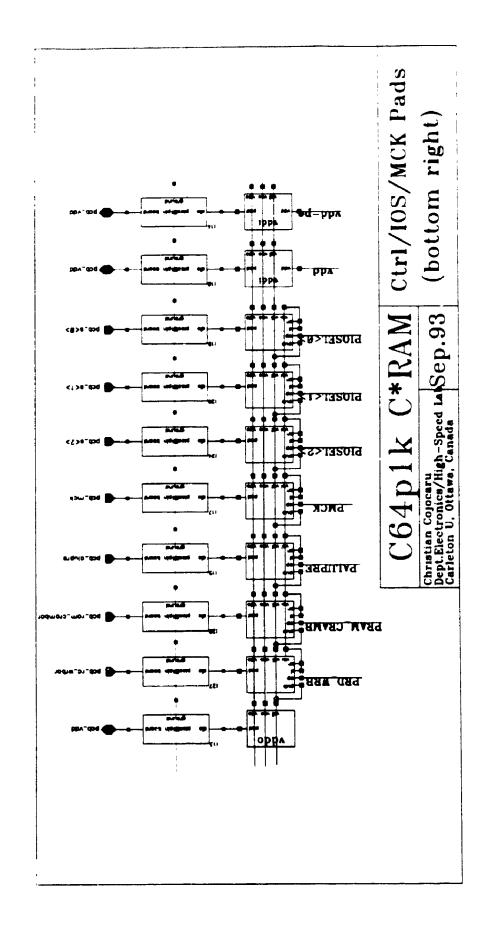

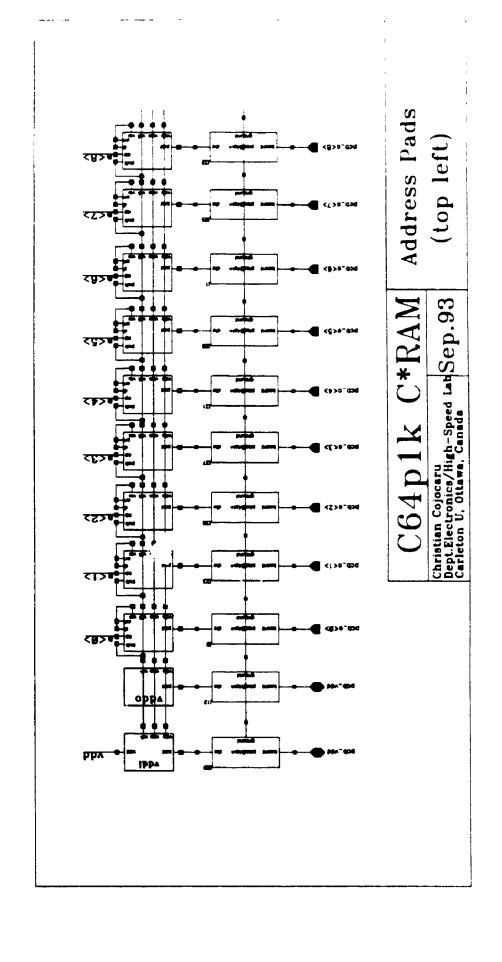

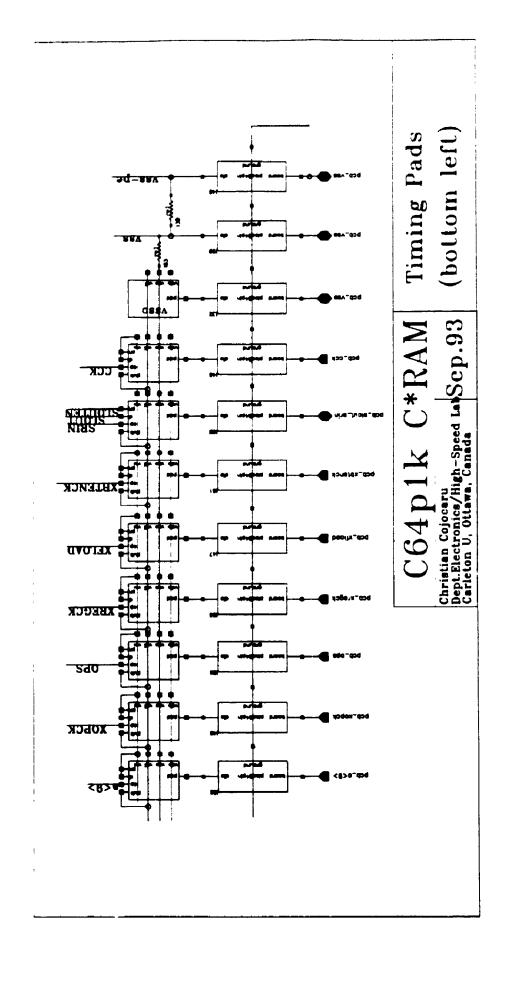

| A C64p1k Schematics                                | 142   |

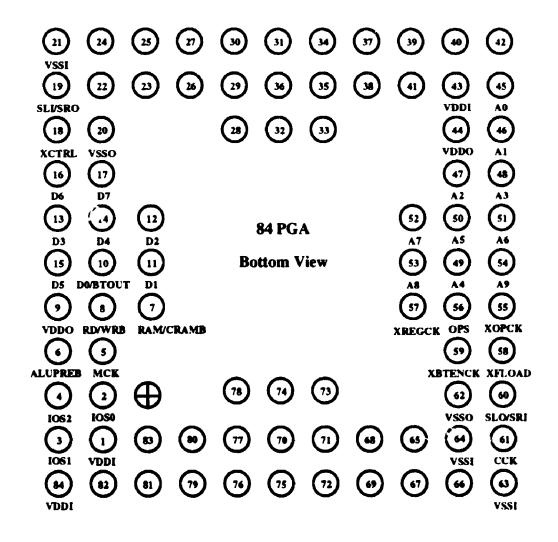

| B C64p1k Pinout                                    | 157   |

| C C64p1k Test Board Schematic                      | 158   |

# **List of Figures**

| 1.1(a) | Random Access Memory (RAM)                                   | 2  |

|--------|--------------------------------------------------------------|----|

| 1.1(b) | Computational RAM (C*RAM)                                    | 2  |

| 1.2(a) | Conventional computer                                        | 2  |

| 1.2(b) | C*RAM enhanced computer                                      | 2  |

| 2.1    | Example SIMD architecture                                    | 11 |

| 2.2    | SIMD PE intercommunication networks                          | 11 |

| 2.3(a) | Full CMOS SRAM cell                                          | 16 |

| 2.3(b) | HRL SRAM cell                                                | 16 |

| 2.4    | Generic SRAM structure                                       | 17 |

| 2.5    | DRAM core cell                                               | 18 |

| 2.6    | Generic DRAM (after [Taka93])                                | 19 |

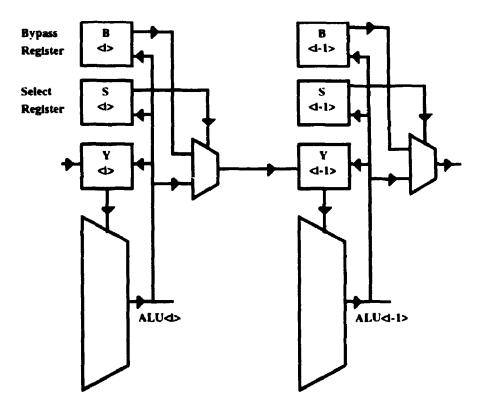

| 3.1    | Baseline PE (BPE) architecture                               | 25 |

| 3.2    | Two ALUs executing the XOR3 function                         | 26 |

| 3.3    | Shift-right data flow                                        | 27 |

| 3.4    | Bus-tie data flow                                            | 28 |

| 3.5    | Conditional write-back to memory using the W register        | 29 |

| 3.6    | MUX8 static CMOS implementation                              | 32 |

| 3.7    | DYN5N dynamic logic implementation of the 8-to-1 multiplexor | 33 |

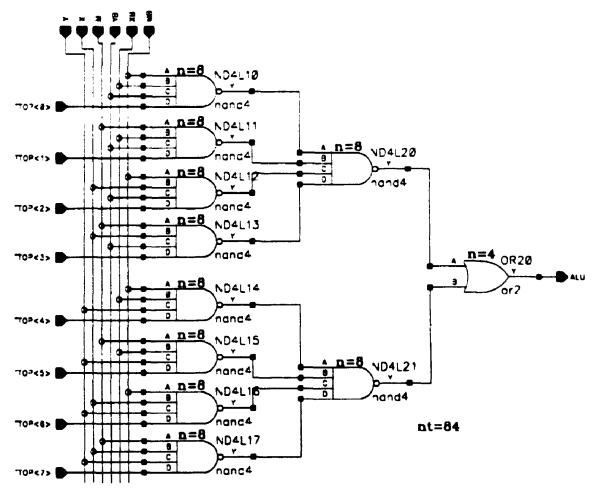

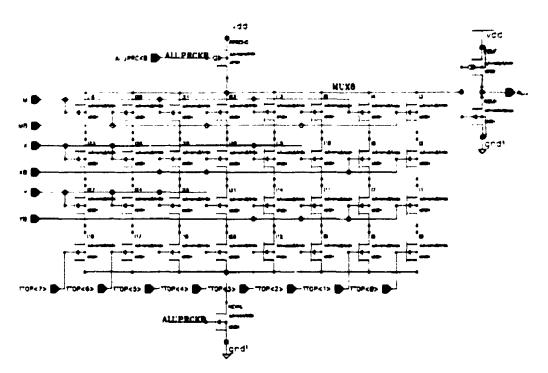

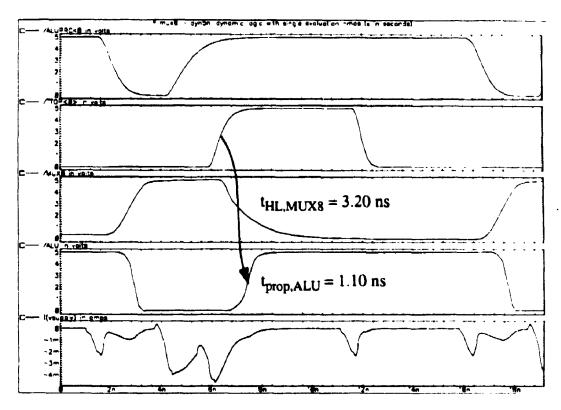

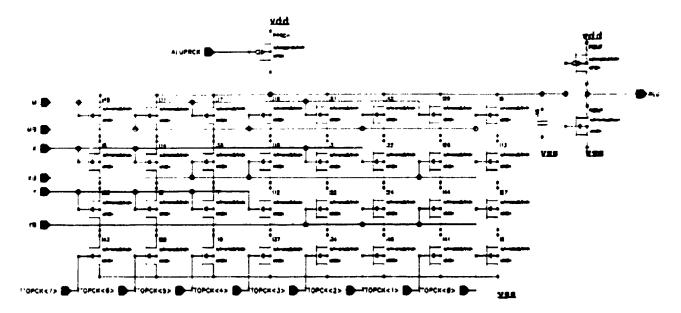

| 3.8    | Spice simulation of DYN5N                                    | 34 |

| 3.9    | DYN4N dynamic implementation of MUX8                         | 35 |

| 3.10   | Pseudo-dynamic DYN4N with latch-back PMOST (PLATCH)          | 36 |

| 3.11   | ALU operation cycle                                          | 37 |

| 3.12(a | 1) ALU propagation delay function of NMOST width wnmx8                      | 39 |

|--------|-----------------------------------------------------------------------------|----|

| 3.12(t | O) ALU discharge evaluation time function of wnmx8                          | 30 |

| 3.13   | ALU precharge, discharge and total energy as function of wnmx8              | 40 |

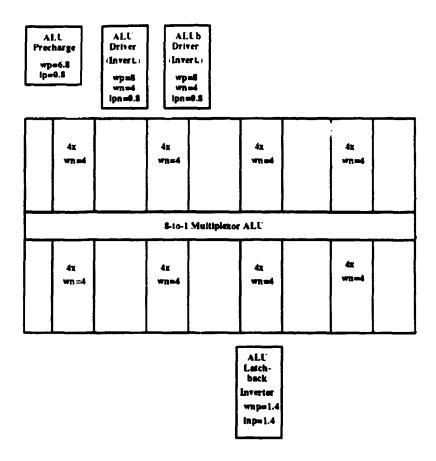

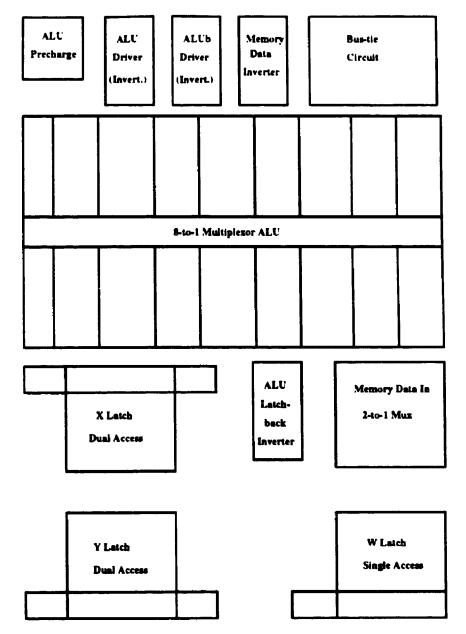

| 3.14   | ALU floor-plan                                                              | 41 |

| 3.15   | ALU multiplexor layout                                                      | 42 |

| 3.16   | An example of an CMOS edge-triggered D flip-flop                            | 43 |

| 3.17   | CMOS D-latch, requiring 10 transistors                                      | 44 |

| 3.18   | Timing of ALU operation, followed by register write                         | 45 |

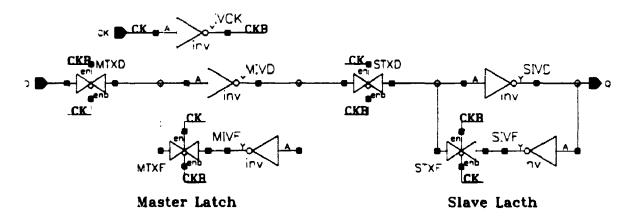

| 3.19   | Final circuit for single-access D-latch                                     | 46 |

| 3.20   | Dual-access D-latch                                                         | 48 |

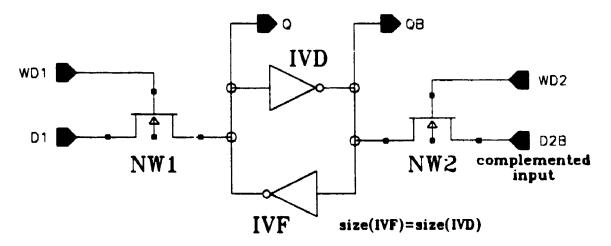

| 3.21   | A symmetric dual-access D-latch                                             | 48 |

| 3.22   | Writing a "1" then a "0" in the dual-access latch (YR waveform)             | 50 |

| 3.23(a | ) LOW-HIGH latch write time t <sub>WLH</sub> function of access NMOST width | 50 |

| 3.23(t | ) Energy spent in latch state reversal                                      | 50 |

| 3.24(2 | 1) LOW-HIGH latch write time twlh function of write driver size             | 51 |

| 3.24(t | Energy spent in latch reversal function of write driver size (NMOST width)  | 51 |

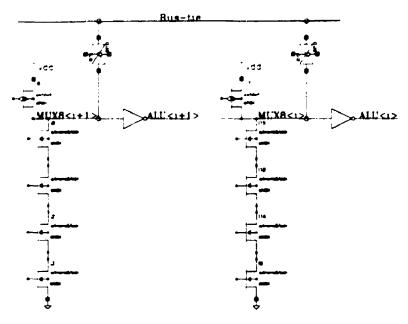

| 3.25   | Layout of X and Y registers in two adjacent PEs                             | 52 |

| 3.26   | Symbolic diagram of Bus-tie circuitry                                       | 53 |

| 3.27   | Global wired-OR with precharged bus                                         | 54 |

| 3.28   | Bidirectional Bus-tie with transmission gates                               | 55 |

| 3.29   | Active Bus-tie circuit proposed by Elliott                                  | 56 |

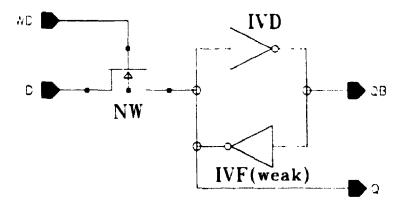

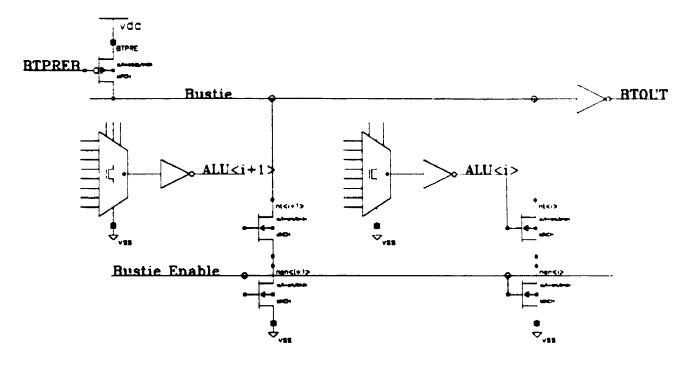

| 3.30   | Proposed compact Bus-tie circuit                                            | 57 |

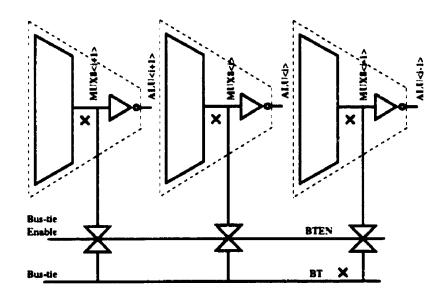

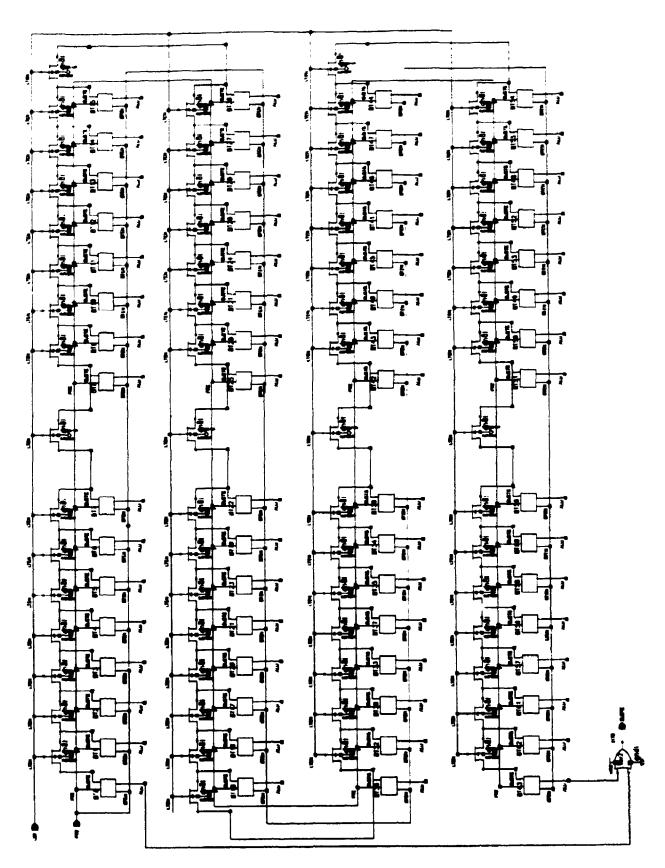

| 3.31   | Array connection of 64 Bus-tie circuits                                     | 58 |

| 3.32   | Spice simulation of worst-case 64 PE Bus-tie cycle                          | 59 |

| 3.33   | Bus-tie circuit layout in two adjacent PEs                                  | 60 |

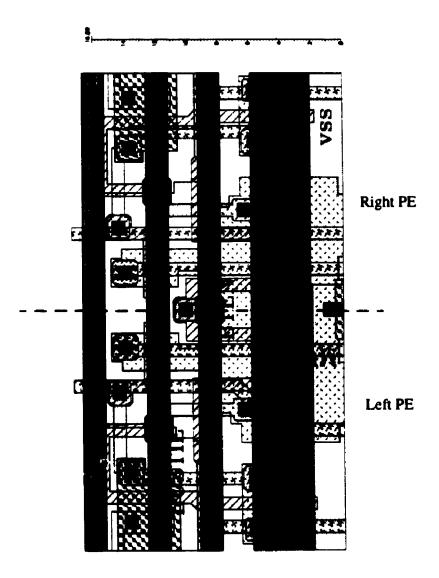

| 3.34   | Processing Element layout floor-plan                                        | 62 |

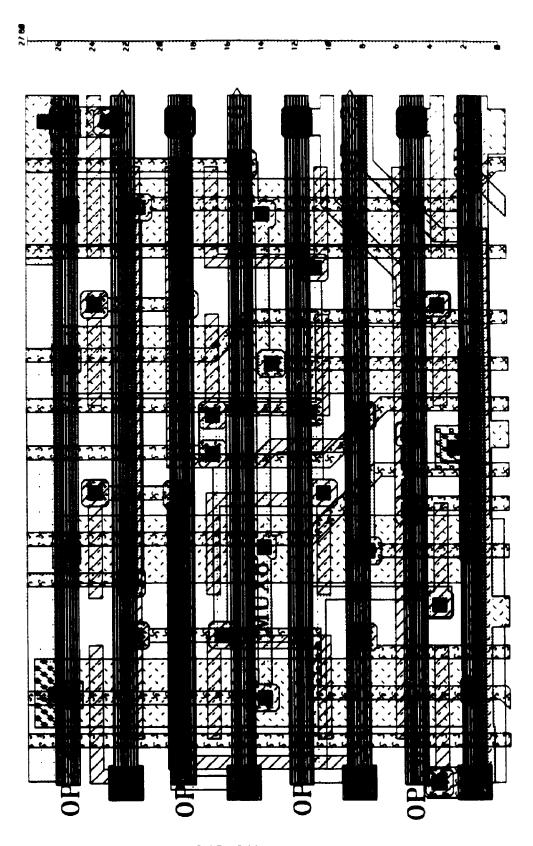

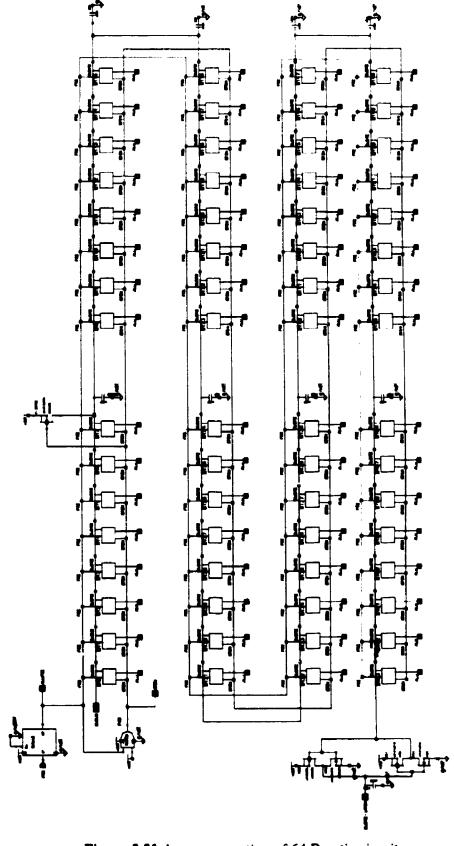

| 3.35   | Dual Processing Element layout                                              | 64 |

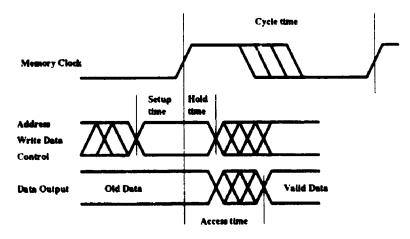

| 4.1    | BNR's synchronous SRAM timing                                               | 67 |

70

71

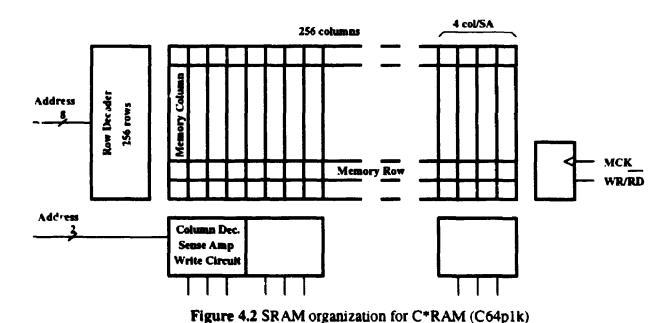

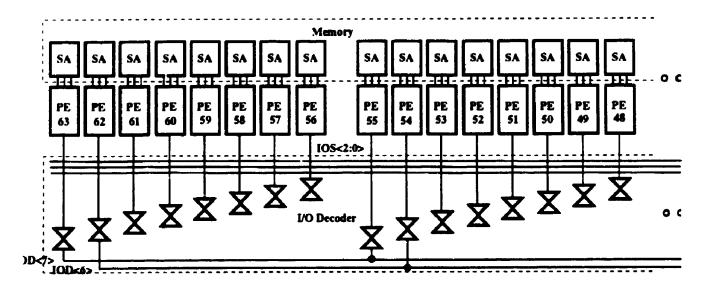

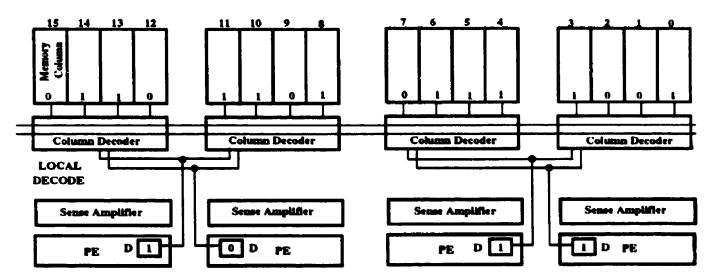

SRAM organization for C\*RAM (C64plk)

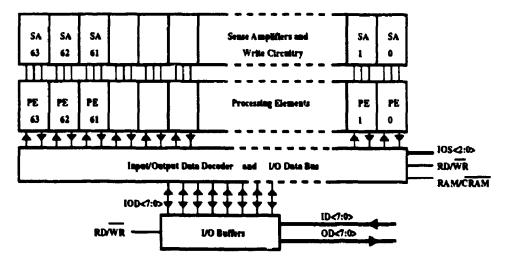

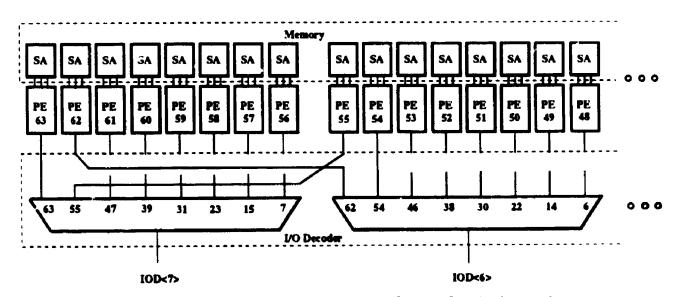

64 PE C\*RAM Input/Output organization

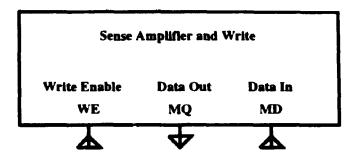

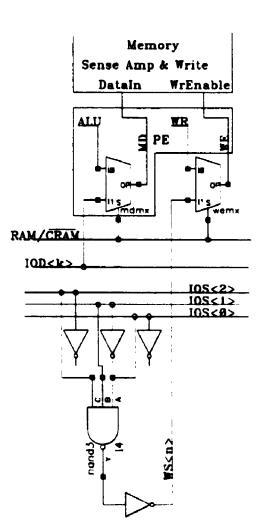

1 bit memory interface

4.2

4.3

4.4

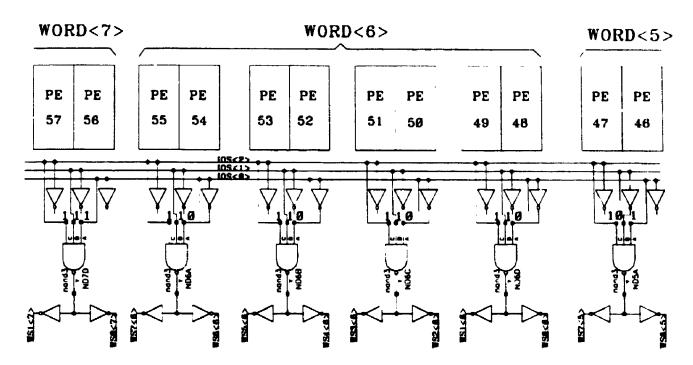

| 4.5        | Logic function of I/O Data Decoder                             | 72  |

|------------|----------------------------------------------------------------|-----|

| 4 6        | Practical arrangement of the I/O Decoder                       | 73  |

| <b>4</b> 7 | Decoding section in the I/O Decoder                            | 74  |

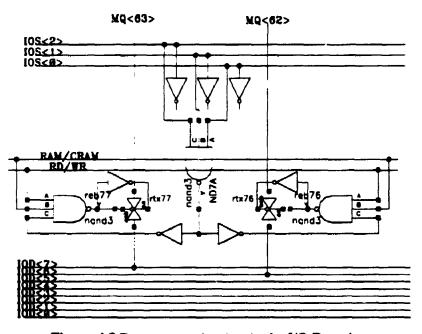

| 4 8        | Data output circuitry in the I/O Decoder                       | 75  |

| 49         | Data input circuitry in the I/O Decoder                        | 76  |

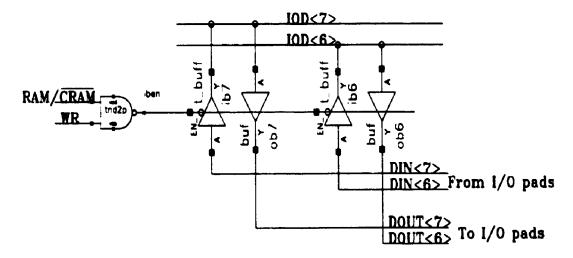

| 4 10       | Input/Output buffers                                           | 77  |

| 4.11       | TTOP register and associated enable/driver AND gates           | 79  |

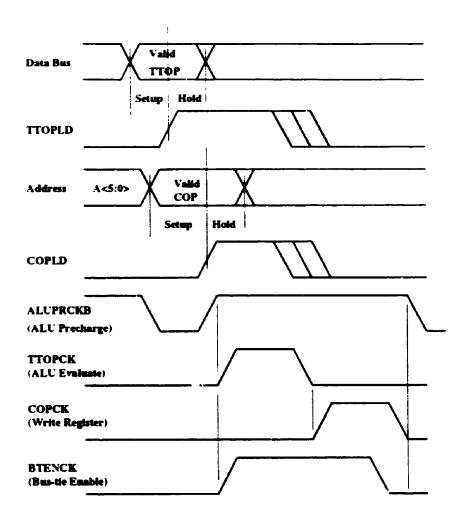

| 4 12       | Example of C*RAM specific timing signals                       | 81  |

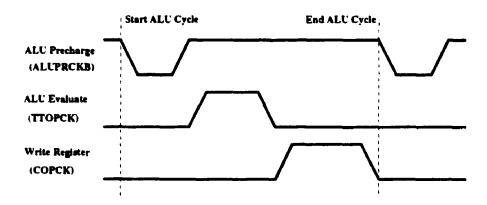

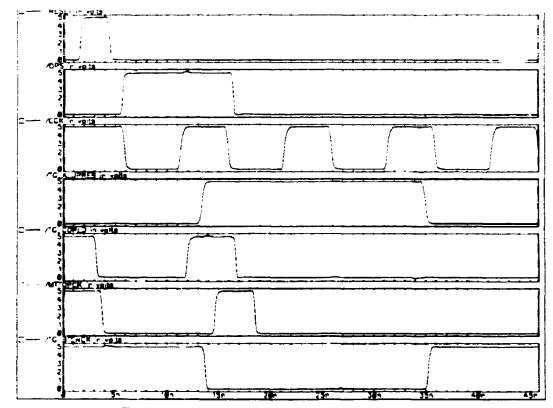

| 4.13       | Timing Generator PE standard cycle                             | 84  |

| 4.14       | Timing Generator Bus-tie cycle                                 | 84  |

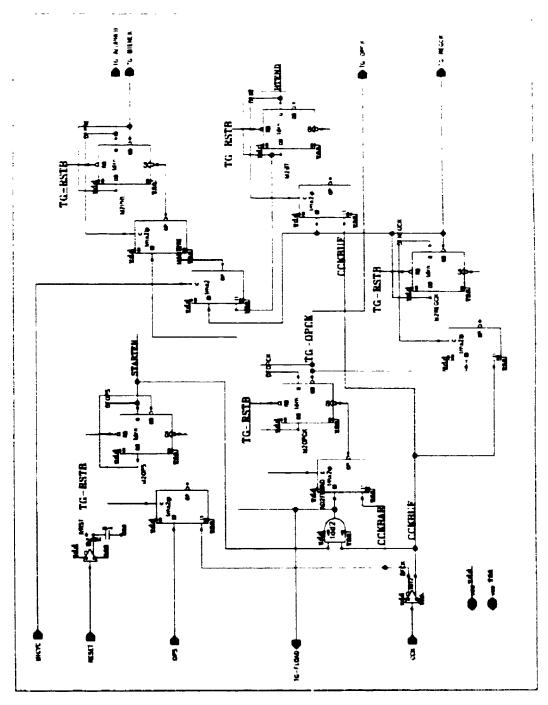

| 4.15       | Timing Generator electrical schematic                          | 85  |

| 4.16       | C*RAM Write cycle                                              | 86  |

| 4.17(a     | a) C*RAM Read cycle                                            | 86  |

| 4.17(t     | n)C*RAM Page-mode Read cycle                                   | 86  |

| 4.18       | C*RAM Operate cycle                                            | 87  |

| 4.19       | C*RAM Read-Operate cycle                                       | 87  |

| 4.20       | C*RAM Operate-Write cycle                                      | 88  |

| 4.21       | C*RAM Read-Operate-Write cycle                                 | 88  |

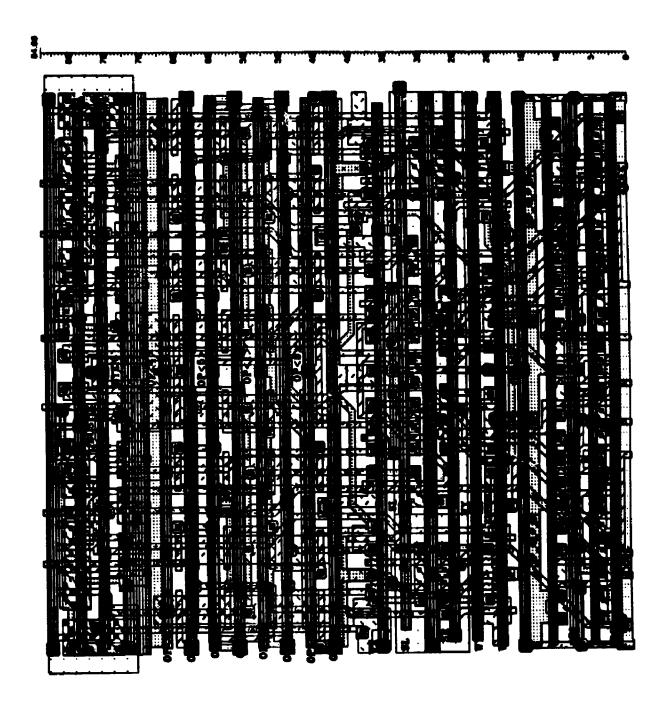

| 4.22       | 64 PE Computational RAM floor-plan                             | 90  |

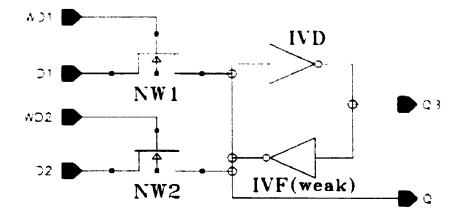

| 5.1        | Bus-tie circuit in the Baseline PE                             | 93  |

| 5.2        | The Programmable Segments Bus-tie (PSB) Network                | 93  |

| 5.3        | PSB circuit implementation within a PE                         | 97  |

| 5.4        | PSB Network connections                                        | 98  |

| 5.5        | Programmable Segments Bus-tie network simulation               | 99  |

| 5.6        | 64 PE PSB circuit                                              | 100 |

| 5.7        | Global Shift-right data flow                                   | 101 |

| 5.8        | A restricted configuration for Segmented Shift                 | 102 |

| 5.9        | Introducing shift boundaries while conserving the Global Shift | 102 |

| 5.10       | Flexible implementation of Segmented Shift                     | 103 |

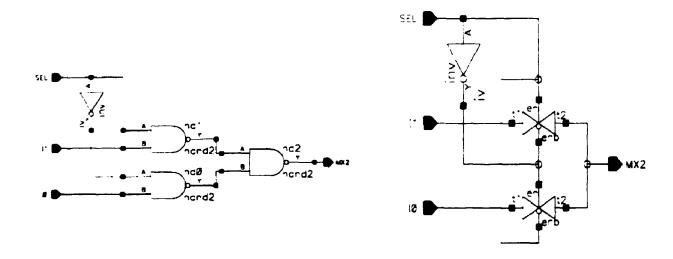

| 5.11       | Logic gate multiplexor                                         | 104 |

| 5.12       | Transmission gate multiplexor                                  | 104 |

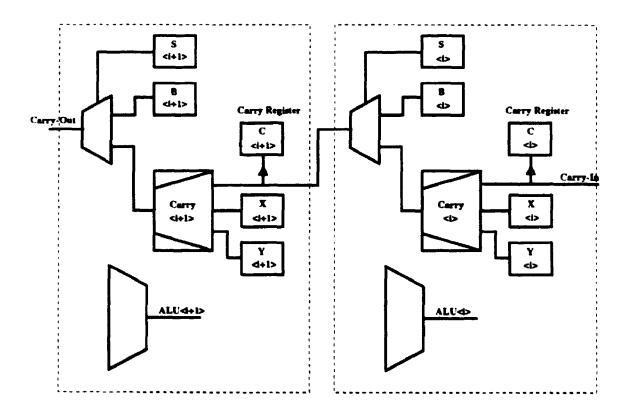

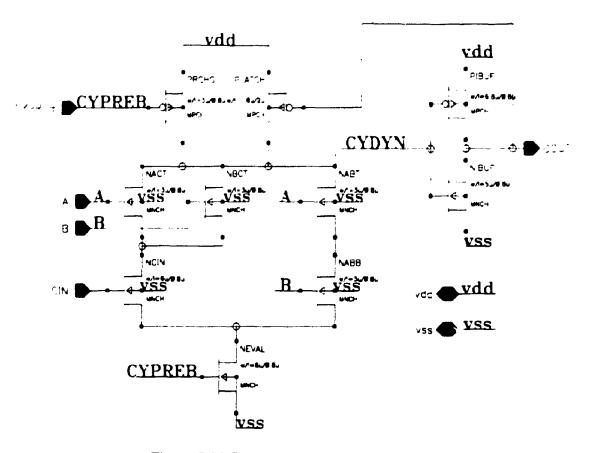

| 5.13  | Carry block in the Extended PE                              | 106 |

|-------|-------------------------------------------------------------|-----|

| 5.14  | Carry circuit schematic                                     | 108 |

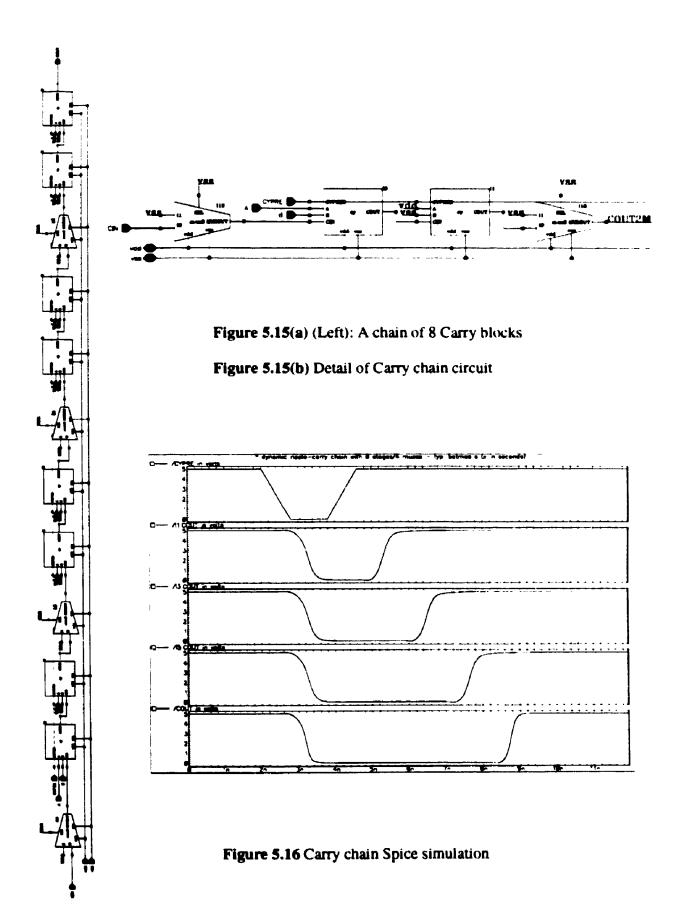

| 5.150 | a) A chain of 8 Carry blocks                                | 111 |

| 5.150 | b) Detail of Carry chain circuit                            | 111 |

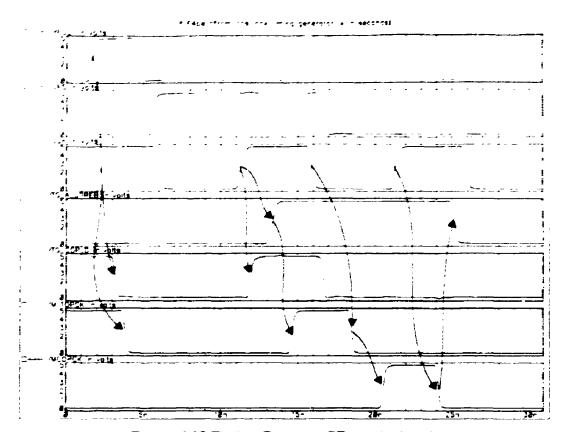

| 5.16  | Carry chain Spice simulation                                | 111 |

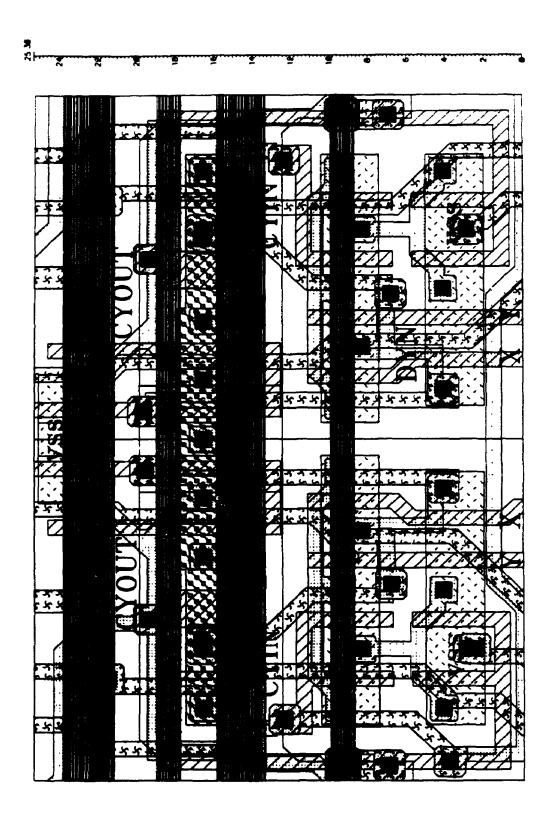

| 5.17  | Layout of Carry blocks in adjacent PEs                      | 112 |

| 5.18  | Data registers in the Extended PE                           | 113 |

| 5.19  | Extended PE (XPE) architecture                              | 115 |

| 5.20  | Dual (Left-Right) Extended PE layout                        | 116 |

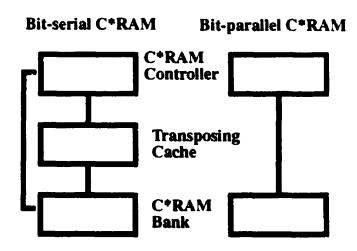

| 5.21  | Bit-serial vs. Bit-parallel C*RAM systems                   | 122 |

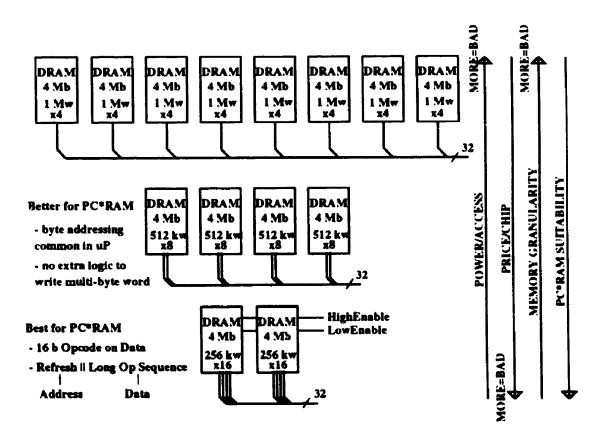

| 5.22  | 32-bit memory subsystem with x4, x8 and x16 DRAMs           | 123 |

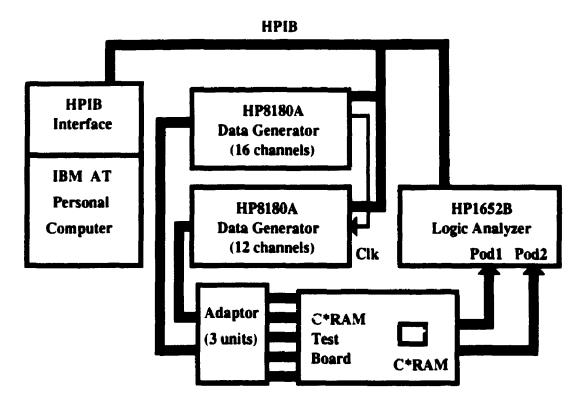

| 6.1   | C*RAM test setup                                            | 128 |

| 7.1   | Column decoder controlled by PE registers in an SRAM C*RAM  | 133 |

| Lis   | t of Tables                                                 |     |

| 2.1   | Comparison of BATMOS C*RAMs and CRAM-like SIMD machines/ICs | 15  |

| 3.1   | Examples of logic functions of 3 variables                  | 25  |

| 4.1   | Platform SRAM Modularity Range                              | 68  |

| 4.2   | Synopsis of BATMOS C*RAM chips                              | 89  |

| 5.1-5 | .8                                                          |     |

|       | Bit-Parallel Multiplication Example                         | 118 |

# **Abbreviations and Terms**

ALU = Arithmetic and Logic Unit

ASIC = Application Specific Integrated Circuit

BiCMOS = Bipolar and CMOS technology

BPE = Baseline Processing Element

CMOS = Complementary Metal-Oxide-Semiconductor

C\*RAM = Computational Random Access Memory

CS = Carry Save; a redundant way of representing numbers with 2 bits per digit

DRAM = Dynamic RAM

FP = Floating Point

GPIB = General Purpose Interface Bus; another name for the HPIB

HPIB = Hewlett-Packard Interface Bus: an interface for programmable instruments

LSB = least significant bit

MIMD = Multiple Instruction Multiple Data

MOST = Metal-Oxide-Semiconductor (MOS) transistor

MSB = most significant bit in a multibit word (by convention here in the leftmost position)

PCB = Printed Circuit Board

PC\*RAM = Parallel Computational RAM

PE = Processing Element

RAM = Random Access Memory

SA = Sense Amplifier; circuit that amplifies a reduced differential voltage from the memory core into full logic levels.

SIMD = Single Instruction Multiple Data

SIMM = Single In-line Memory Module; a compact way of mounting multiple memory chips on a small PCB.

SRAM = Static RAM

$V_{th} = MOS$  transistor threshold voltage

# Chapter 1

## **Introduction to C\*RAM**

#### 1.0 The C\*RAM Concept

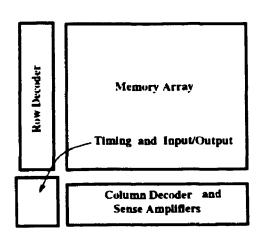

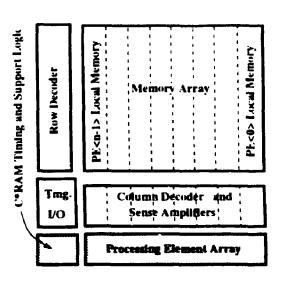

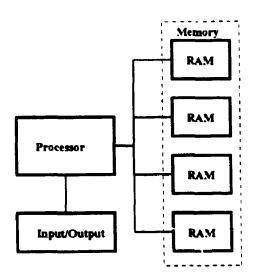

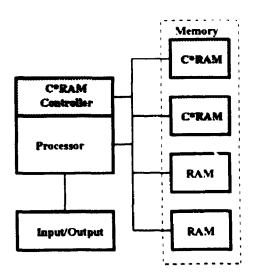

Computational Random Access Memory (abbreviated in the following as C\*RAM) is an integrated circuit which adds a large number of minimal processing elements to a semiconductor memory array, Figure 1.1 [Elli92]. A hypothetical commercial C\*RAM would have 2048 Processing Elements (PE), each having 100-150 transistors, integrated in a 16 megabit Dynamic RAM. The objective is to enhance the memory subsystem of a computer with low-cost local computing power, while conserving its conventional storage function, Figure 1.2. The main advantages of this computing structure are:

- a. it uses the wide internal bandwidth inherent in high-density memories, currently wasted or sparsely used;

- b. avoids or minimizes the power dissipated in processor-memory data transport by keeping applicable computation inside memory, and

- c. it is an incremental change of the well-established conventional computer.

The processing elements are organized in a Single Instruction Multiple Data (SIMD) linear array, the most economical in terms of silicon area. This memory localized computing structure has a data parallel nature and maps well to applications in the area of image and video processing, recently gaining more importance in the workstation/personal computer market. A large number of other applications can benefit from the fine grain parallelism of C\*RAM: scientific (numerical)

computation, database search, data compression, neural and genetic algorithms. In order to achieve production yields and market pricing comparable to semiconductor memory, the extra silicon area taken by the processing elements has to be small, estimated at maximum 20% of the memory chip.

Fig.1.1(a) Random Access Memory (RAM)

Fig.1.1(b) Computational RAM (C\*RAM)

Fig.1.2(a) Conventional computer

Fig.1.2(b) C\*RAM enhanced computer

### 1.1 Conventional Computers and Integrated Circuits Technology

The vast majority of computers in use today are organized around the structure called the Von Neumann architecture (also referred to as "conventional computer"). This structure has two main functional blocks, the processor and the memory. The processor does the computation (logic and arithmetic) and system control functions, executing instructions and working on data stored in the memory. Both instructions and data are in binary format and are identified by their address in the memory. The processor does the address housekeeping, i.e. keeps track of what kind of informations is stored at which address, in an otherwise uniform binary space.

The tremendous advances in semiconductor integrated electronic circuits in the last three decades have resulted in million-transistor processors being integrated in a single chip (microprocessors) and have allowed the memory to attain single-chip capacities of 256 megabit. While chip densities have increased for both elements, the microprocessor speed of operation has advanced much more than that of integrated memories. The original communication channel between processor and memory has become more and more of a bottleneck, defined by it's bandwidth in bytes/second. The economics of memory pricing have dictated the most significant variation on the von Neumann structure, namely the introduction of a fast (but expensive) small memory named "cache" between the fast microprocessor and the slow (but inexpensive) large main memory. A processor+memory single chip system has not become a viable alternative for general purpose computers because programs have surpassed hardware advances by demanding even more instruction and data memory.

# 1.2 Parallel Computers - Brief Overview

Functional limits are on the horizon for the conventional structure. Processing speed is the main limit, bringing with it power and thermal constraints. Processor clocking frequencies have attained today (end 1994) 200 MHz for mainstream silicon technology (DEC Alpha, [IESp93]). Beside the speed gap between processors and memory, there are growing technological problems associated with increasing clock frequencies, especially in the areas of signal integrity and heat dissipation [Schu93].

One solution to the these limits is parallel processing [Alma93], [PRI491], [Patt94]. A parallel computer has multiple processors executing instructions simultaneously. A vast number of structures can be described in this manner. An early classification was made by Flynn [Flyn66] and has the categories:

- 1. Single Instruction-stream Single Data-stream computers (SISD), the conventional architecture.

- 2. Single Instruction-stream Multiple Data-stream (SIMD): all processors execute the same instruction.

- 3. Multiple Instruction-stream Multiple Data-stream (MIMD): the processors execute independent program flows, processing different data.

Computers with multiple processors or execution units have been built under the generic categories of superscalar architectures, vector supercomputers, massively parallel processors or Very Long Instruction Word (VLIW). Superscalar is a characteristic associated with the latest generation of microprocessors, and refers to the simultaneous execution of two to four instructions, typically arithmetic operations. Vector supercomputers (e.g. the Cray machines) have an intermediate number (e.g. 4 to 64) of very powerful processing units and typically use exotic technologies (e.g. gallium arsenide logic chips, liquid Freon cooling). In a similar vein, recent generations of mainframe computers have multiple processors (4 to 8) and use non-mainstream technologies (bipolar emitter coupled logic, special cooling) [IESp89]. In recent years, a number of massively parallel computers (MPC) have been developed by clustering tens or hundreds of conventional microprocessors with a memory system. These MPCs have been built in both SIMD and MIMD categories.

While building the hardware proved feasible for a majority of machines, the clear problem that appeared in the process was defining the software (operating system, languages, compilers) that would make efficient use of the machine. The problem is especially difficult for MIMD machines, where multiple program threads have to use common resources and exchange data. The result of the expensive hardware and of the non-standard software is that the parallel machines occupy a very high-end market niche (although a growing one), far from the popularity of workstations or personal computers.

### 1.3 Semiconductor Memories as an Integrated Circuits Category

The semiconductor technology advances that lead to the integration of multi-million transistor processors have also created a number of specializations within the Integrated Circuits (IC) industry, with fairly distinct technical cultures. There is first a distinction between full-custom ICs, like processors and memory, and Application Specific ICs (ASICs). The ASICs are typically built by customizing the metal interconnect layers overlaid on a standard pre-designed transistor structure, called gate array. There is a large variety of other ASIC design methods, including standard cell, sea-of-gates, and in the last decade, Field Programmable Gate Arrays (FPGA).

In the full-custom category, the specialization occurred between the random logic ICs, such as the microprocessors and the semiconductor memory. Within the latter there are distinctive categories, but the largest market segment is the Random Access Memory (RAM), with two different technologies, the Static RAM (SRAM) and the Dynamic RAM (DRAM). Due to the difference in the basic memory cell, DRAM offers four times more storage capacity than SRAM, but is also four to six times slower. Because DRAM prices are four to six times lower than equivalent SRAM, the main memory in the workstation and personal computers is build with DRAM. The high end computers (mainframes, supercomputers) use SRAM for the main memory. The big market for SRAMs though is as cache memory. A cache memory bridges the speed gap between the fast microprocessors (90 MHz for Intel Pentium used in today's high end personal computers) and the cost-effective but slow DRAM main memory (e.g. 70 ns access time, 120 ns cycle time).

Both SRAM and DRAM share the block structure in Figure 1.1(a). Details on the differences are given in Chapter 2. The memory core (the actual storage area) is organized in rectangular blocks, composed of rows and columns. In each memory read access, a row of information is amplified to full logic levels by the row of sense amplifiers. Out of the large number of bits amplified (e.g. 2048 in a 4 Mb DRAM), only a small fraction (e.g. 1, 4, 8) are selected as chip output, transmitted on the system bus and used for processing by the Central Processing Unit (CPU, i.e. the microprocessor). The C\*RAM concept is built on the intention to use the large internal memory bandwidth in order to do SIMD computation within the memory chip.

# 1.4 C\*RAM - An SIMD-IC Memory Hybrid

The C\*RAM concept tries to establish a common point between the architecture intensive SIMD machine world and the circuitry intensive SRAM/DRAM memory world. The C\*RAM starts from the memory structure and builds an SIMD machine by adding processors along one of the memory array dimensions. All trade-offs are resolved in favor of keeping the resulting structure as close as possible to memory, in terms of area and system interface. The reason is that C\*RAM is intended to substitute part of the main memory (as shown in Figure 1.2(b)) with the goal to add low-cost SIMD capability to conventional computers. Computation that maps well to the SIMD model benefits thus not only from an extremely large bandwidth, but also from the low-power allowed by keeping data transport on chip.

In view of its higher density and lower cost, DRAM is assumed to be the platform of choice for building C\*RAM. Since DRAM functions by periodically regenerating the information stored in the core, it offers a higher internal bandwidth than SRAM. Large capacity SRAMs could be used for more specialized or higher end machines, or as a stage in building system and applications experience.

The main problem that faces C\*RAM is the economics of high-density memories, discussed in Chapter 2. Technical issues in a C\*RAM system are the gap between memory input/output speed and the internal computing power (I/O vs. internal bandwidth), and the rather small size of local memory. The forces at work for standard DRAM are also addressing these C\*RAM problems. First, faster interfaces, such as Synchronous DRAM, are becoming more popular. As an alternative, the already established second serial access port (similar to the Video DRAM common in performance video buffers) could be used in high-end systems. Secondly, the local memory size issue has still to be decided by real applications, while ever increasing DRAM densities move the limit higher.

As is usually the case in technology history, fairly recently it surfaced that similar ideas are being developed by a number of groups in the world. Some of the closest concepts are the Processor-in-Memory (PIM) developed at the Supercomputing Research Centre in U.S.A. and the Nippon Electric Company Integrated Memory Array Processor (IMAP) chip. These chips are presented in

more detail in Chapter 2.

# 1.5 Computational RAM History

This section briefly presents the efforts made by the Canadian group in the field of integrating an SIMD-memory hybrid. The first SIMD experiments were made by Snelgrove and Loucks at University of Toronto in 1978, with a machine called VASTOR [Louc80]. Efforts to integrate VASTOR were hampered by the crudeness of tools/technology available in the academic environment. A 64 Processing Elements 8 kb SRAM based C\*RAM prototype in 1.2 µm CMOS technology was designed by Duncan Elliott, at University of Toronto, in 1989, using a simplified PE (no interprocessor communication). In 1990 Elliott started designing a DRAM based C\*RAM in cooperation with Mosaid Inc, a project mentioned in [Elli92], but the foundry partner upgraded its process and the project was abandoned.

#### 1.6 Thesis Contributions

There are two main directions where this thesis advances the C\*RAM project. First, a 64 Processing Element C\*RAM part is designed and implemented in the most advanced technology available in Canada at this time, Northern Telecom's 0.8 µm BiCMOS, using a 64 kb memory module made available by Bell-Northern Research. One major thrust within this implementation was the design of an extremely area-efficient processing element, that demonstrates what the limits are in adding PEs to ASIC memories. On the same level with the compactness criterion was the design of PE circuitry safe-guarded against potential technology hazards, such as leakage currents. The overall goal of this implementation was to obtain functional parts, allowing the C\*RAM project to continue with building a system and hence insuring the "reality" of the concept in the eyes of possible applications partners.

Secondly, this work explores novel structures of C\*RAM processing elements. Although Elliott's Baseline PE is very simple and hence allows for many variations/enhancements, the proposed Extended PE attempts to maximize the arithmetic power of the PE while maintaining a close control of the silicon area expenses required. The Baseline PE simplicity was a result of its DRAM target. The C\*RAMs described here are based on ASIC SRAM, which, due to its more relaxed

area constraints, lead to extending the PE functionality. The Extended PE could be adopted on a DRAM platform, with a corresponding loss in processor count.

A first enhancement to the Baseline PE is the so called "Programmable Segments Bus-ue" (PSB), which is implemented in a second C\*RAM chip, still with 64 PEs but a smaller 512 bit local memory (referred to as Cs64p512). This chip also demonstrates a novel system oriented C\*RAM feature, the integration of a RAM serial access port.

The original bit-parallel oriented PE array is designed into a third C\*RAM chip, with 512 PE and 480 bit local memory (C512mp512). Beside the Programmable Segments Bus-tie, the new PE introduces support for Programmable Word Boundaries (PWB) and a hard-wired ripple-carry chain, resulting in flexible word length bit-parallel operation. The Extended PE demonstrates the minimal hardware structure capable of performing bit-parallel integer multiplication entirely within the PE array, i.e. without intermediary memory access, resulting in speed, power and system interface advantages over the classical bit-serial approach. This final chip (currently in fabrication) also includes a tighter timing circuit, close to what a commercial chip is expected to feature. In general, the interface of this chip reflects the experience accumulated during this work, including a first attempt to design a C\*RAM subsystem.

# 1.7 Thesis Organization

Chapter 2 gives first an overview of SIMD machines and discusses projects similar to C\*RAM. It presents then more details on the SRAM and DRAM memory categories and their suitability as starting platforms for building C\*RAM. The economic aspects of memory and C\*RAM are presented at the end.

Chapter 3 begins by presenting the architecture of the Baseline Processing Element (BPE), defined by Elliott. Most of the chapter is dedicated to the detailed CMOS circuit and physical design of the BPE.

Chapter 4 describes the design of the Computational RAMs implemented in Northern Telecom BiCMOS technology (BATMOS). The chapter introduces the industrial family of modular SRAM

used as C\*RAM platform, then presents the C\*RAM specific logic blocks, including the Input Output circuitry, timing generation and C\*RAM instruction multiplexing. Detailed timing diagrams of C\*RAM cycles are shown at the end of the chapter.

Chapter 5 introduces the original Bit-Parallel Processing Element architecture and presents the arguments in favor of bit-parallel oriented C\*RAM. A detailed presentation of the circuit modifications and additions to the Baseline PE is followed by a step-by-step description of a bit-parallel integer multiply example, as executed by the new PE architecture.

Chapter 6 presents the experimental results. The BATMOS C\*RAM hardware and software test environment is described here.

Chapter 7 discusses ideas that could be implemented in future generations of C\*RAM, focussing on adding independent PE addressing with a minimum of area overhead. The chapter ends with a summary of this work and with a discussion of possible developments of the C\*RAM project.

# Chapter 2

# **SIMD and Semiconductor Memory**

This chapter will present in more detail the two technical categories C\*RAM is based on, SIMD machines and semiconductor integrated memories, together with the adaptations required of both in order to integrate them into the Computational RAM SIMD-memory hybrid.

### 2.1 Single Instruction Multiple Data (SIMD) Computers

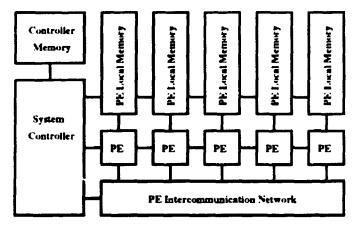

SIMD machines consist of multiple processing elements (PEs) executing the same instruction, each PE acting on different data stored in its local memory space, Figure 2.1, [Hord90], [Alma89]. Compared to their classic counterpart, MIMDs, these machines offer a much more tractable software environment and the hardware is easier to build. The reason is that the single program flow does not need the hardware and software complexity required to synchronize the MIMD multiple instruction and data flows. SIMD is best mapped to the "data parallel" programming model, for which the same processing sequence is applied to a large set of data. Most SIMD machines built so far have used large numbers (hundreds or thousands) of very simple processors, being referred to as Massively Parallel SIMD.

In general, when examining an SIMD machine, the following characteristics should be identified:

- 1. Complexity of the individual PE.

- 2. PE intercommunication network.

- 3. Independent local memory addressing capability.

- 4 Local memory size and PE-memory integration level.

PE complexity can be characterized by data word length, number of internal registers, functionality of the arithmetic and logic unit (ALU).

Figure 2.1 Example SIMD architecture

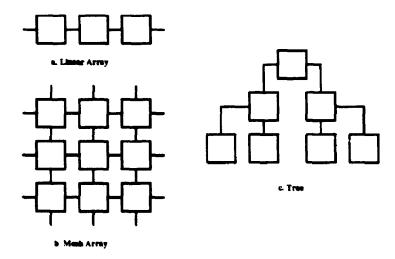

One important criterion that differentiates between SIMD machines is the intercommunication network between processors. Some typical examples are linear array, mesh (bidimensional array), tree network and hypercube, of which the first three are shown in Figure 1.4 a,b,c respectively. The linear array network is the simplest, with one PE connected to just two neighbors. The mesh array arranges the PEs in a bidimensional configuration, with one PE connected to its four neighbors.

Figure 2.2 SIMD PE intercommunication networks

The hypercube network extends the spatial cube arrangement to n-dimensional (above 3 dimensions) spaces, each PE being connected to nothers. The various connection networks try to anticipate and minimize the communication costs of certain classes of application programs. By providing increased complexity in the communication network, the architecture designers drive up the complexity and cost of hardware, in terms of board interconnections and/or in terms of silicon area. To date, the most commercial success in the SIMD category has been associated with the rather simple mesh-connected arrays (DAP, MPP).

The linear array and mesh networks are well suited for VLSI integration because of their regularity. C\*RAM attempts to adapt a PE array to a memory structure, and, due to the minimal supplementary area constraints discussed in section 2.4, the linear array is the best choice. The PEs (assuming no interconnection) are forced to match the unidimensional arrangement of the sense amplifier array. A PE intercommunication network has to be then unfolded and mapped to the rectangular area adjacent to the PE array. The left-right communication is the natural choice for the linear array, taking only two routing channels per link. More complicated communication networks will require more routing channels, exponentially more routing channels for the higher-order networks. When the network has to be extended between chips, the linear and mesh networks are the only ones to extend with a low and constant number of pins, an important factor in setting the chip cost.

#### 2.2 SIMD Machines Similar to C\*RAM

The last twenty years have seen a number of massively parallel SIMD machines being developed. Some of them, like MPP (Massively Parallel Processor) from MasPar, DAP (Distributed Array Processor) from Active Memory Technology and Connection Machines (CM-2, CM-5) from Thinking Machines Corp. are currently in commercial use. These machines demonstrate that there is a market for applications that are handled well by the SIMD computing paradigm. On the other side, these SIMD machines target a niche high-end market. They are typically large and expensive, because they use simple processors in low integration-level chips separated from the local memory. Their computing power is related to the number of processors, hence more of them means more PE chips, more memory chips, more boards and interconnections, driving the final cost high. Using separate local memory, the number of PEs integrated on a chip becomes limited by the number of package pins required for the memory interface.

This section will present three architectures similar to C\*RAM, in order to show the extent of interest in this class of computers and to present classes of applications. The SIMD literature is much richer in machine references [PRI491], but we restrict the discussion to those architectures that use a linear organization of the PE array with unidimensional communication networks. The assumption here is that the nature of the intercommunications network has a major impact on how applications are written for a particular machine and on the performance of these applications. The AIS-5000 was chosen because it is highly similar to the C\*RAM Baseline PE array, while the PIM and IMAP were chosen because they integrate the PEs with their local memories into a single chip, coming very close (PIM especially) to the basic C\*RAM idea.

#### 2.2.1 The AIS-5000 Parallel Processor [Smit88]

This is a commercial SIMD machine which has 1024 single-bit PEs in the maximum configuration. While the PEs are physically organized in a linear array, the system software can emulate a

bidimensional array. The main difference to C\*RAM is that the PEs are not integrated in the

memory. Instead, gate array ASICs with 8 PE/chip are connected to commodity SRAM chips. The

authors claim that separate PE and memory is an advantage because it permits use of the low-cost

standard SRAM. The unspecified disadvantage though is physical size: the maximum configuration of the machine has 8 printed circuit boards, with associated high costs and reliability problems. The PE is built around a 16-to-1 multiplexor, similar to the C\*RAM (which has an 8-to-1

multiplexor, Chapter 3) and other single-bit SIMD machines.

The AIS-5000 is used commercially in machine vision tasks, but in [Smit88] other general purpose functions are evaluated (content addressable memory, bit string classifier, vector correlation). The designers of the machine demonstrate that for many image-based algorithms in use, the linear (unidimensional) array is superior in price/performance to the popular \_\_sh arrays.

### 2.2.2 The SRC Processor-in-Memory (PIM) [Gokh92]

An integrated SIMD project developed at the Supercomputing Research Centre (SRC) in Maryland. USA, the PIM is a chip that integrates 64 PEs with 2 kb local memory. Again, the PEs are

connected in a linear array. The PE structure is more complex than the baseline C\*RAM PE, by an estimated factor of 4-5, complex enough to admit a pipelined operation. There are three local registers and an ALU that generates three logic functions. The PIM PEs execute one command every 70 ns. Interprocessor communication is performed through a so called "parallel prefix network", a global OR function and a programmable-partition OR (POR) network. The parallel prefix network allows PEs at fixed positions to send data to groups of neighboring PEs. The programmable-partition OR network can execute logic-OR on power of 2 groups of PIM chips. The PIM to system interface is a 4-bit memory data bus, inherited apparently from the SRAM the chip was built upon. A number of PIM chips have been designed into a single-board SIMD subsystem that plugs into the system bus of a SUN workstation.

The applications discussed are cross-correlation and prime number searching, but the machine was probably designed for intensive cryptography analysis problems, as suggested by the affiliation of SRC to the Institute for Defense Analyses. A very recent development (Sept.1994) [EET816] has Cray Computer Corp. announcing they will use an extended PIM chip for a CRAY machine memory system, the project being sponsored by the U.S. National Security Agency.

The PIM project and its recent development are very close to C\*RAM in both basic concept - small area PE array added to memory - and system organization. One of the important differences is that the SRC team does not mention DRAM as a possible platform for the PIM chip.

#### 2.2.3 The NEC Integrated Memory Array Processor (IMAP) [Yama94]

This chip was introduced at the 1994 ISSCC by researchers from Nippon Electric Company, targeting real-time low-level image processing applications. The IMAP integrates 64 8-bit processing elements with a 2Mb SRAM, the highest level of integration recorded for C\*RAM-like chips. The main peculiarity of the IMAP chip is the fact that each PE can independently address a 256-word memory page in the local memory. This feature is demonstrated as important for certain operations (image histogram, Hough transforms), where it substantially reduces execution time over an architecture without independent addressing. The PE structure is closer to typical 8-bit microprocessors (18 register file, 8-bit ALU, shifter block, multiplier look-up table) hence it is much more complex than a C\*RAM PE. This PE results in an 50% memory-50% processors bal-

ance in IMAP (as suggested by the chip microphotograph). The PE clock is 40 MHz while the SRAM speed is 80 MHz. The chip has block redundancy, and is implemented in an aggressive 0.55 µm BiCMOS technology with SRAM enhancements. Although not explicitly mentioned in the paper, the independent PE addressing feature must require replicating a row decoder block for each local memory, because the cited 128 columns per row are not sufficient to supply a 256 word page. The resulting area overhead could be acceptable for a 50%-50% processor to memory balance, but not for a 10%-90% hybrid that targets replacing memory, as is the case of C\*RAM.

Table 2.1 summarizes characteristics of C\*RAM and of the architectures presented above. Also included in Table 2.1 are the two most representative C\*RAM chips designed for this work, discussed in detail in Chapter 4. In the table, the PE complexity entry refers to the relative PE transistor count, with the Baseline C\*RAM PE discussed in Chapter 3 as reference. When the actual number was not available, an estimate was made based on the PE functional description. Similarly, the communication network complexity refers to the number of inter-PE channels, relative to the Baseline PE.

Table 2.1 Comparison of BATMOS C\*RAMs and C\*RAM-like SIMD machines/ICs

|                         | C*RAM<br>C512mp512 | C*RAM<br>C64p1k | AIS-5000  | SRC PIM | NEC<br>IMAP |

|-------------------------|--------------------|-----------------|-----------|---------|-------------|

| Memory-integrated PEs   | yes                | yes             | no        | yes     | yes         |

| PEs/chip                | 512                | 64              | 8         | 64      | 64          |

| Word length (bits)      | 1 or 2n, n>0       | 1               | 1         | 1       | 8           |

| PE count • Word length  | 512                | 64              | 8         | 64      | 512         |

| Local Memory (bits)     | 480                | 1024            | 32 kb     | 2048    | 32 kb       |

| PE Cycle Time (ns)      | 15                 | 20              | 100       | 70      | 25          |

| PE Rel. Complexity      | 2                  | 1               | 3 (est)   | 5 (est) | 92          |

| Network Rel. Complexity | 1.5                | 1               | l (est)   | 4 (est) | 16          |

| External I/O Width      | 8                  | 8               | 4         | 4       | 4           |

| Redundancy              | no                 | no              | no        | no      | block       |

| Design/Technology       | FC-ASIC            | FC-ASIC         | GateArray | •       | SRAM        |

#### 2.3 SRAM and DRAM

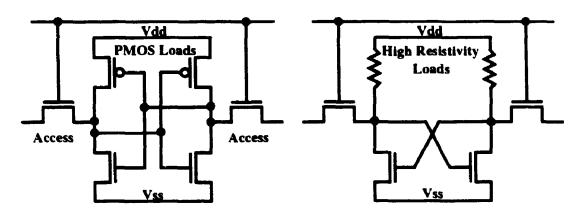

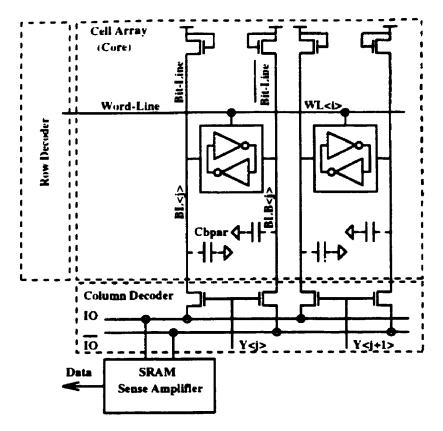

#### 2.3.1 Static Random Access Memory (SRAM)

A block-level diagram of an SRAM is shown in Figure 2.4. The basic memory cell, represented symbolically as two back-to-back inverters, is represented at the transistor level in Figure 2.3. The SRAM cell is a positive feed-back structure (latch) with two stable states. There are three different implementations for the cell, depending on what kind of elements are used as the cell loads: diffused (bulk) PMOS transistors (in a standard CMOS process), Figure 2.3(a), high resistivity polysilicon loads (also called giga-ohm poly), Figure 2.3(b), or thin-film PMOS transistors deposited over the rest of the devices in the cell. The last two alternatives are process enhancements used specifically for SRAM design in order to obtain compact cell layout, and are not available in general-purpose ASIC processes.

Fig.2.3(a) Full CMOS SRAM cell

Fig.2.3(b) HRL SRAM cell

A sketchy description of an SRAM read cycle follows. The SRAM address is partitioned in two sections, serving as inputs to the row and column decoders. Most conventional SRAMs are asynchronous (i.e. there is no clock in the interface), and an Address Transition Detect (ATD) circuit initiates an access cycle once the address lines are stable for a certain duration. The row decoder selects and activates one Word Line (WL) that turns on all the access transistors in the selected row. The selected cells begin driving the associated Bit Lines (BL) and their complements, BLB (Bit Line Bar), which are typically precharged HIGH outside active cycles. The cell sees the bit lines as large capacitive loads, to be discharged by the cell NMOS drivers to the sensitivity level

Figure 2.4 Generic SRAM structure

of the sense amplifier. The column decoder selects one (assuming one bit interface) BL/BLB pair and connects it to the differential I/O bus. This bus is the differential input to the SRAM amplifier which regenerates full logic levels and drives an output buffer. The signal carried by both the bit line pairs and by the I/O bus is a small differential voltage (tens or hundreds milivolt), with a DC level close to the precharge voltage.

A key point when building an SRAM-based C\*RAM is that one sense amplifier is associated with a group of array columns. For C\*RAM, the number of sense amplifiers dictates the maximum number of PEs, because the PE input needs the full logic level from the SA output. The main SRAM design trade-off is between sensing speed on one side and low-power and high density on the other side: more columns connected to the same sense amp is good for density and power (there are fewer SAs overall) but bad for sensing speed because of the increased capacitance of the I/O lines, leading to a smaller sensed signal. For example, in one 1 Mb SRAM [Wada87] there is one SA for every 16 columns, for a total of 128 SAs per chip, and the resulting access time is 37 ns. In another 1 Mb SRAM using similar technology, [Mats87], there are only 8 columns per SA

for a total of 256 SAs and a shorter 25 ns access time. This last SRAM has in fact a two-level hierarchy of sense amplifiers, four of the first-level SAa being connected to one second-level SA. In both 1 Mb SRAMs, there are a total of 512 rows and 2048 columns, organized in a number of blocks, hence there are 512 cells in one bit column.

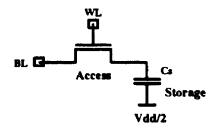

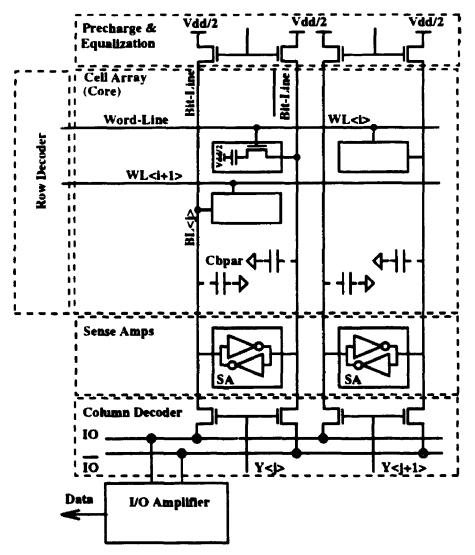

#### 2.3.2 Dynamic Random Access Memory (DRAM)

The basic 1T-DRAM cell, shown in Figure 2.5, has just one access transistor and one storage capacitor. The information is stored as electrical charge on the cell capacitor, and is periodically read and rewritten - a process called refresh - in order to compensate for charge leakage. There are no circuit variations but there are plenty of technological alternatives to implement the basic cell. Up to and including most 1 Mb DRAMs, the basic cell was planar [Prin91] and DRAM was considered the semiconductor process technology driver. In the quest to reduce cell size and manufacture larger capacity DRAMs, the DRAM foundries were the first to decrease the feature size (finest line in the lithographic process). Starting with the 4 Mb level, the planar cell was replaced with three-dimensional structures (stacked capacitor, trench capacitors), and the DRAM processes, while still very aggressive, became too specialized to be representative of other semiconductor categories. For example, most ASICs are connection-limited by the number of metal layers available, rather than logic gat 3-limited by the process lithographic resolution.

Figure 2.5 DRAM core cell

A DRAM block diagram is shown in Figure 2.6. Compared to SRAM, the main difference is the presence of one sense amplifier for every column, localized between the bit lines and the Input/Output (I/O) lines. In the large majority of DRAMs, the sense amplifier (SA) is a latch (similar to the SRAM cell but without access transistors) whose power supply connection is controlled by a transistor. One SA per column is necessary to do the refresh operation, i.e. to regenerate the full

logic levels and drive them back onto the bit lines in order to refresh the cell charge information. The SA layout is physically constrained now to the width of one memory column, which is in the order of microns for current generations DRAMs.

For a DRAM-C\*RAM, it seems that the maximum number of PEs can be much bigger when compared to SRAM-C\*RAM. In reality, even with the simple PE circuitry described in Chapter 3. the extremely small SA pitch requires that one PE correspond to a number of SAs (e.g. one PE for every 4, 8 or 16 SAs, depending on DRAM generation).

Figure 2.6 Generic DRAM (after [Taka93])

In DRAM design, the main parameter is the sensing voltage presented to the sense amplifier

input. This parameter depends on the ratio of cell storage capacitance (on the order of 50 H-10r-4 Mb DRAM) to the bit line parasitic capacitance, because this is the reduction factor applied to the cell voltage when the cell is selected for read-out. The limited cell capacitance combined with the parasitic bit line capacitance limits the number of DRAM cells connected in a column to a typical value of 128. In the SRAM examples presented above, there were 512 cells in a column. The SRAM can afford more cells per column because the cell contains active elements, which, given enough time, will drive the desired voltage differential on the bit lines. As a result of the smaller number of cells per column, hence more total columns, the DRAM will have more sense amplitiers than an equivalent size SRAM with an hypothetical 1 SA/column.

#### 2.4 C\*RAM Economics

#### 2.4.1 DRAM Economics

As mentioned in the first chapter, DRAM is considered the preferred platform for C\*RAM implementation, because of its predominance in computer main memory subsystems and video frame buffers.

The problem with DRAM-based C\*RAM is the access to DRAM fabrication technology, rather than designing and building the actual chip [IBMV94]. DRAM is a commodity IC category which require a very sizable capital investment (in the order of hundreds of millions US dollars). Once operational, the DRAM facility is geared towards high volume production to recover the capital investment, hence is quasi inaccessible for experimental prototyping. It has been noted that the time to recover capital costs rather than technological constraints dictates the DRAM generation advance interval. These facts explain why while there are a number of researchers trying DRAM+logic ideas [Lipo90], there are no actual proof-of-concept chips.

In economics terms, C\*RAM represents the "technological push" aspect rather than the "market pull". There are no working applications to demonstrate the advantages of C\*RAM over existing platforms. This is partly because there is no C\*RAM platform to enable experimenting with applications. A solution to this problem is the development of a software emulator, as close to the final hardware as possible. This work is underway at Carleton University [Cast94], based on the

on the C\*RAM chips presented in this work. A possible way to approach DRAM C\*RAM is building a system based on high-density SRAM C\*RAM. Such systems will address a higher-end market (because of the DRAM-SRAM price differential), but could be an intermediate stage in building up applications and market awareness of the technology.

#### 2.4.2 C\*RAM Area and Yield Issues

We assert that in order for C\*RAM to become a viable substitute for at least part of computer memory, the supplementary area taken by the PE array has to be a small fraction of an equivalent capacity memory. The C\*RAM chip cost includes the package and the silicon die costs. The C\*RAM pinout is expected to have 3-4 extra pins over the corresponding DRAM (Chapter 5). This would have been a problem a few years ago, when DRAM packages were highly standardized. Today (1994), the DRAM market displays a much larger variety of interfaces (wide word, Synchronous DRAM, Extended Data Out, Rambus DRAM) and packages, and having four more pins is no longer an iconoclastic idea. Hence, the price of the C\*RAM package is estimated to have a minor differential above the average DRAM package.

Chip area is one of the two factors affecting the manufacturing yield (ratio of good chips to total chips) and in turn the yield is the main factor determining the die cost.

The yield Y of memory chips can be estimated using the following formula [Prin91]:

(2.1) Poisson:

$$Y = \exp(-A \cdot D)$$

where:

A = chip area.

D = defect density of the manufacturing line.

The formula shows an exponential decrease of the yield with an increasing area, which supports the argument for minimal area increase of C\*RAM.

In order to improve manufacturing yields, especially in the first years of production, DRAM

designs include a number of redundant rows and columns. Upon detection of defective rows or columns, a spare element is activated typically by blowing on-chip fuses. The spare columns or rows are physically situated at the periphery of the array. The procedure is effective in increasing the final yield while keeping the same access time because there is no interdependence between rows or columns.

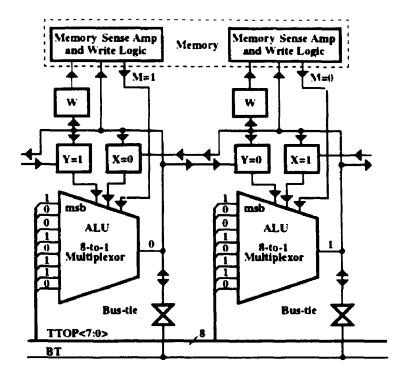

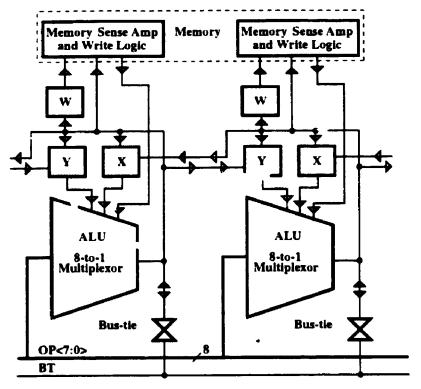

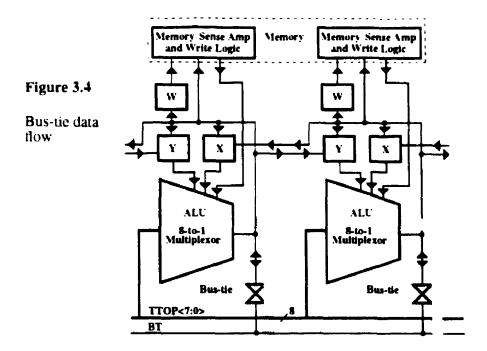

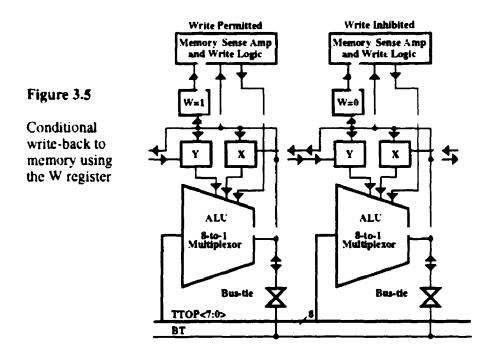

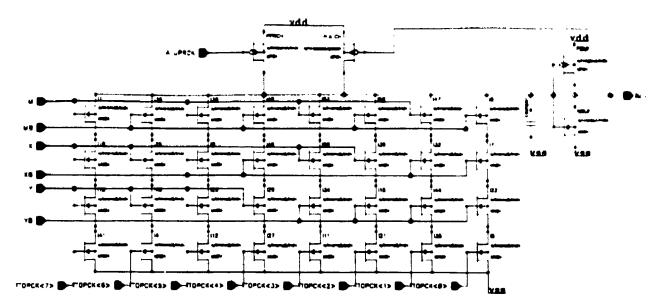

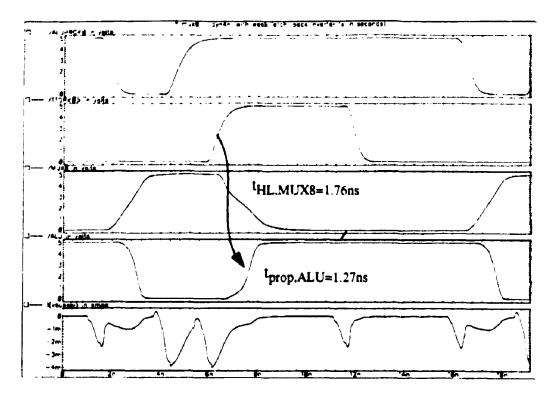

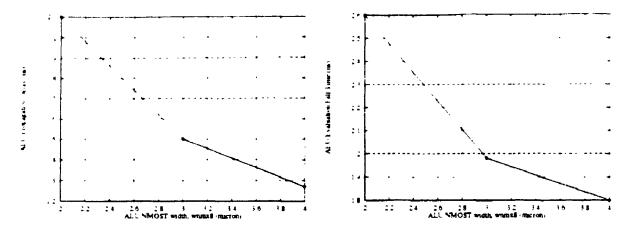

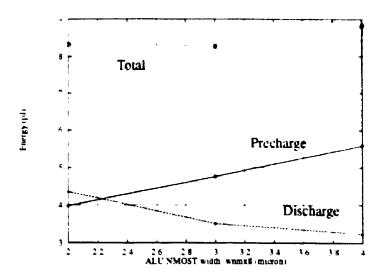

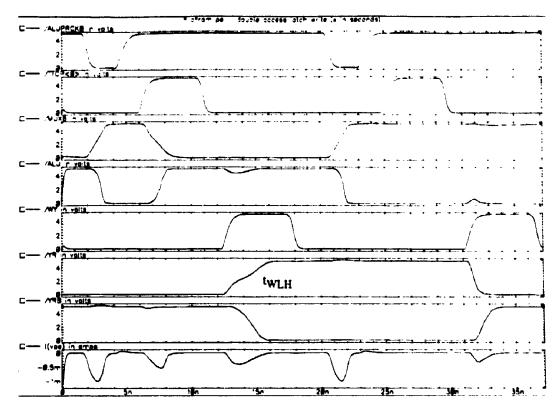

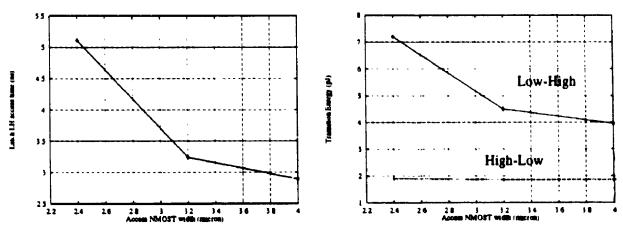

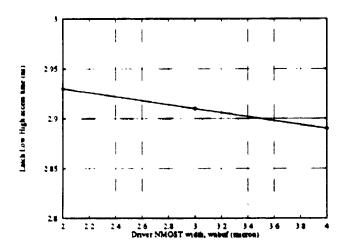

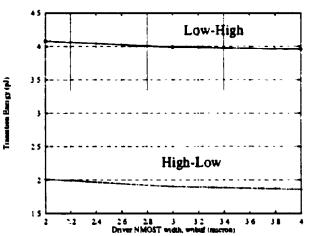

In contrast, most SIMD applications require some form of intercommunication between the PEs. The Baseline PE, presented in Chapter 3, has closest neighbor shift-left/right links. The Bit-parallel Extended PE array presented in Chapter 5 depends in large measure on local communication. Since PEs are directly associated with memory columns, the PE order imposed by local communication is transferred to the memory columns. The conclusion is that memory column redundancy methods cannot be practically applied to the PE array, if defective PEs are detected. Replacing a PE located in the middle of the array with a spare PE located at one extremity would have a destructive impact on operating speed, a 40 µm long line driven by close to minimum size transistors being replaced with a 5 mm one (numbers are estimated values).