## A Single-IF Receiver Architecture Using a Complex Sigma-Delta Modulator

by

#### Ashok Swaminathan

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Masters of Engineering

Ottawa-Carleton Institute for Electrical Engineering

Department of Electronics

Faculty of Engineering

Carleton University

Ottawa, Canada

© Ashok Swaminathan, 1997

|  | - |

|--|---|

|  |   |

|  |   |

|  |   |

## **Abstract**

In the growing market for portable communications, it is becoming more important to design high performance transceivers which consume little power. Currently, many architectures are exploited to give the maximum dynamic range while running off a 1 V battery. This makes it challenging to design components such as A/D converters which may be required to have 12-bit resolution.

This thesis proposes a new A/D converter called a Complex Bandpass  $\Sigma\Delta$  Modulator suitable for a Single-IF receiver architecture This modulator is based on existing bandpass  $\Sigma\Delta$  Modulator structures, and was designed to give roughly double the bandwidth performance of existing Bandpass  $\Sigma\Delta$  Modulators. Two versions of this modulator were designed and fabricated as switched C circuits in a 0.8 $\mu$ m BiCMOS technology, and the results are presented. The maximum SNDR of these modulators was 48dB with a bandwidth of 10kHz and a sampling rate of 4MHz with a power dissipation of 160mW. The maximum operating frequency was found to be approximately 45MHz.

This modulator was also tested with a suitable analog front-end operating at an RF of 1.9GHz and an IF of 60MHz. Results are presented for demodulated GMSK data (similar to GSM) for this receiver. This is meant to show the feasibility of using this type of  $\Sigma\Delta$  Modulator in a radio receiver.

## Acknowledgements

I would like to thank my supervisor Martin Snelgrove for his constant support and guidance throughout my MEng. His intuitive way of viewing things helped me grasp things about analog design that were more than a mystery before. And his connections helped to get my chips fabricated in time (to go to Italy). Thanks Marty.

A big thanks goes to Theo Varelas, Luc Lussier, Christian Cojocaru and the rest of the Philsar crowd. Without access to their platform chip, design tools and experience, this whole thesis wouldn't have been possible. Thanks guys.

Jose Macedo deserves the credit for at least half this research, since he provided a fully functional RF front-end for my chip. Thanks for putting in the time to lay out a front-end suitable for my A/D. I owe you one.

Of course, there's a zillion people that are responsible for keeping me sane throughout the past 2 years. Just to name a few: Phil Lauzon, Alana Wirta, Leonard Dauphinee, Walt Bax, and the rest of the radio group at Carleton. Thanks for the information, help and beer that you provided.

For financial support, thanks goes to NSERC and Micronet, without which I wouldn't have nearly as large a CD collection as I have today.

And finally, thanks to my sister and parents for their constant encouragement, questions and occasional pressure to get my thesis done. Hope you still got enough left for my PhD!

# Table of Contents

| Abstract        |                                                                                                                                                                                                                                                                                       | i                          |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Acknowledgem    | ents                                                                                                                                                                                                                                                                                  | ii                         |

| Glossary of Ter | rms                                                                                                                                                                                                                                                                                   | <i>x</i>                   |

| CHAPTER 1       | Introduction                                                                                                                                                                                                                                                                          | 1                          |

|                 | Motivation 1 Thesis Outline 3                                                                                                                                                                                                                                                         |                            |

| CHAPTER 2       | Radio Receivers & PCS                                                                                                                                                                                                                                                                 | 5                          |

|                 | Receivers - The Superheterodyne Technique Image Rejection in Receivers Existing Art - Dual IF Receiver Existing Art - Direct Conversion Existing Art - Single-IF Receivers Receiver Requirements for A/D Converters Emerging Standards for PCS Receiver Requirements Summary          | 71213141518                |

| CHAPTER 3       | Complex SD Modulator Theory  SD Modulation Complex Filter Theory Mismatch Effects in Complex Filters Complex SD Modulation Mismatch Issues in Complex SDM Dealing with Mismatch - Notching Image Noise Dealing with Mismatch - Post Compensation Complex SDM Transfer Function Design | 22<br>27<br>31<br>36<br>39 |

|            | Summary                                              |

|------------|------------------------------------------------------|

| CHAPTER 4  | Complex SD Modulator Design                          |

|            | Design Methodology                                   |

|            | Complex SD Modulator A: First Design53               |

|            | Complex SD Modulator B: Improved Design5'            |

|            | Adaptive DSP Compensation for Mismatch               |

|            | Summary                                              |

| CHAPTER 5  | Complex SD Modulator - Implementation & Results . 65 |

|            | Circuit Structure                                    |

|            | Performance of Circuit Blocks                        |

|            | Simulated Performance of the SD Modulator            |

|            | Experimental Performance of Modulator A              |

|            | Experimental Performance of Modulator B              |

|            | Summary85                                            |

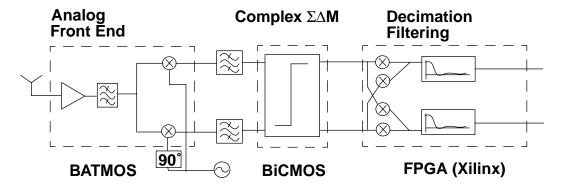

| CHAPTER 6  | The Complex IF Receiver82                            |

|            | The Single-IF Architecture Revisited8                |

|            | Analog Front-End89                                   |

|            | Complex SD Modulator9                                |

|            | Decimation Filtering92                               |

|            | Receiver Performance9                                |

|            | Summary10                                            |

| CHAPTER 7  | Conclusions and Future Work                          |

|            | Summary                                              |

|            | Conclusions                                          |

|            | Future Work                                          |

| References |                                                      |

| *          |                                                      |

|                                                           | v   |

|-----------------------------------------------------------|-----|

| Appendix A: Calculation of SD Coefficients                | 114 |

| Appendix B: Decimation Filtering in C                     | 117 |

| Appendix C: Performance of Receiver for other GMSK inputs | 122 |

|                                                           |     |

|                                                           |     |

|                                                           |     |

|                                                           |     |

|                                                           |     |

|                                                           |     |

|                                                           |     |

|                                                           |     |

|                                                           |     |

|                                                           |     |

|                                                           |     |

|                                                           |     |

|                                                           |     |

# List of Figures

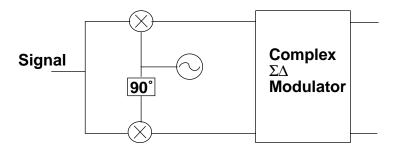

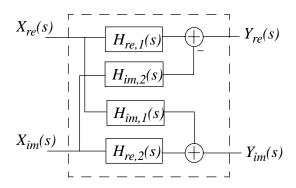

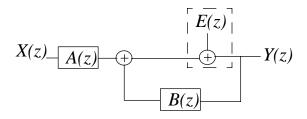

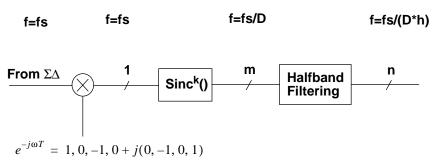

| FIGURE 1.  | A Complex SDM system 2                                                |

|------------|-----------------------------------------------------------------------|

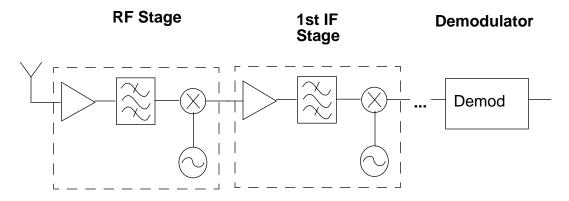

| FIGURE 2.  | Superheterodyne Receiver 6                                            |

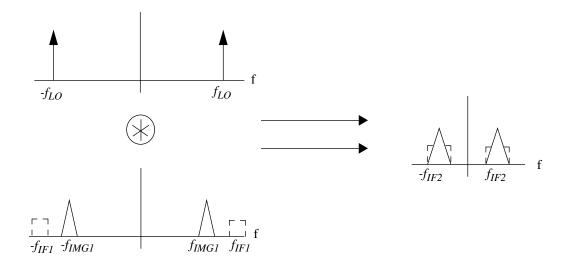

| FIGURE 3.  | Example of IR Technique in Dual IF Receiver 8                         |

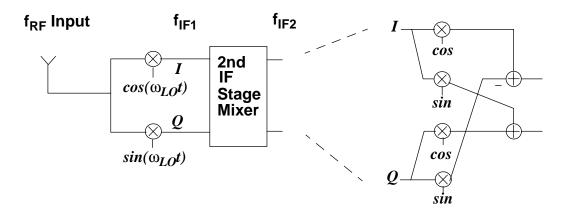

| FIGURE 4.  | Another IR Technique for Multiple IF Receivers 8                      |

| FIGURE 5.  | Dual IF Receiver 12                                                   |

| FIGURE 6.  | Direct Conversion Receiver 13                                         |

| FIGURE 7.  | Single-IF Receiver 14                                                 |

| FIGURE 8.  | Resolution vs. Bandwidth for A/D Converters 16                        |

| FIGURE 9.  | Proposed Single-IF Receiver with Complex SD Modulator 17              |

| FIGURE 10. | Anti-Alias Filter Requirements for Oversampling 23                    |

| FIGURE 11. | Effect of Feedback on Noise Shaping 24                                |

| FIGURE 12. | Transfer Function Design of 1st-order SD Modulator 24                 |

| FIGURE 13. | Pole-Zero Plot for STF and NTF for 1st-Order SD Modulator 26          |

| FIGURE 14. | Simple Passive Complex Filter 27                                      |

| FIGURE 15. | Generalized Complex Filter (assuming ideal transfer functions) 28     |

| FIGURE 16. | Generalized Complex Filter (assuming component mismatch) 30           |

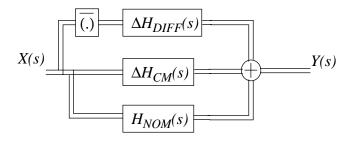

| FIGURE 17. | Complex Filter with Explicit Error Transfer Functions 31              |

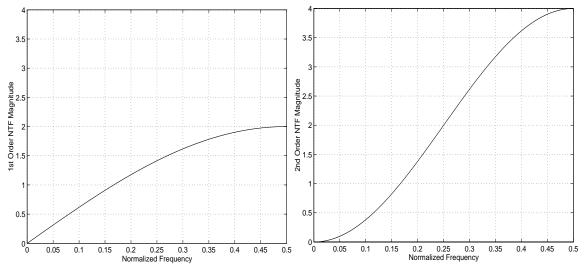

| FIGURE 18. | 1st and 2nd Order Lowpass Modulator NTFs 33                           |

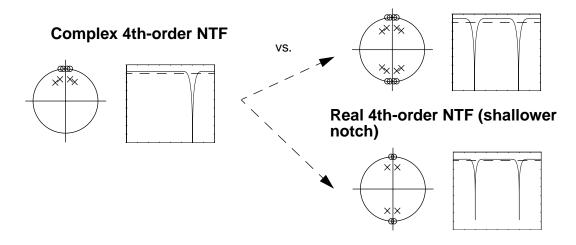

| FIGURE 19. | Complex vs. Real NTFs 34                                              |

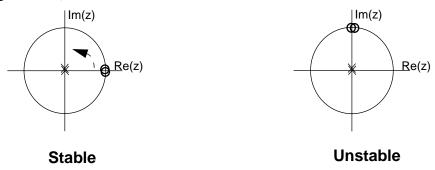

| FIGURE 20. | Effect of Complex Transform on NTF Stability 36                       |

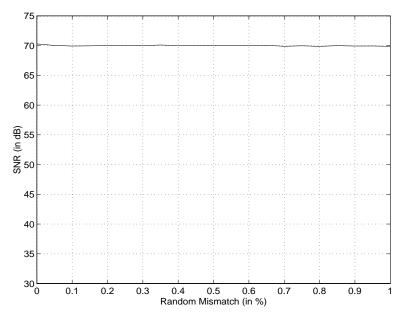

| FIGURE 21. | Response of Example Complex SDM for 0% and 1% Coefficient Mismatch 38 |

| FIGURE 22. | Notching Image Noise in NTF 39                                        |

| FIGURE 23. | Gain Compensation for Complex Filter Mismatch 40                      |

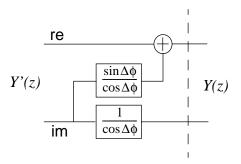

| FIGURE 24. | Phase Compensation for Complex Filter Mismatches 41                   |

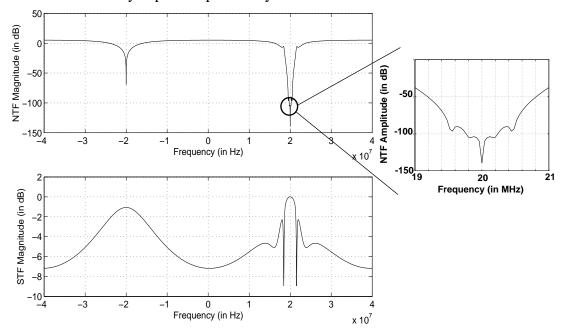

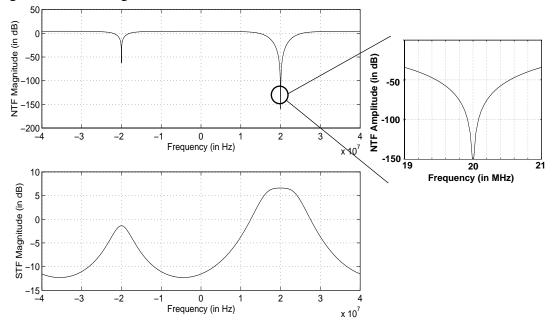

| FIGURE 25. | STF and NTF for Optimized 6th-order Complex SD Modulator 45           |

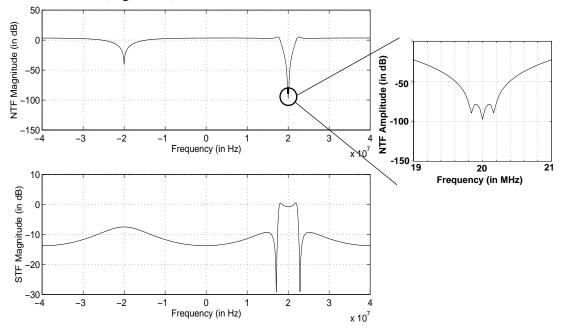

| FIGURE 26. | STF and NTF for Optimized 4th-order Complex SD Modulator 46           |

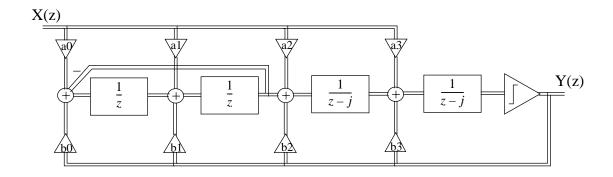

| FIGURE 27. | Block Diagram and Implementable TF of a SDM 50                        |

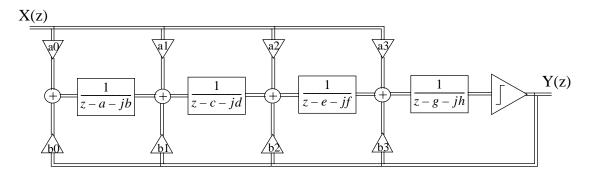

| FIGURE 28. | Cascade-of-Complex-Integrators Structure for Complex SD               |

|            | Modulator 51                                                          |

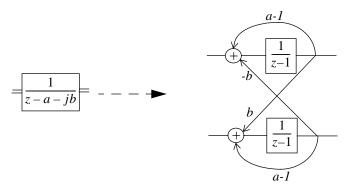

| FIGURE 29. | Complex Integrator using Discrete-Time Real Integrators 51            |

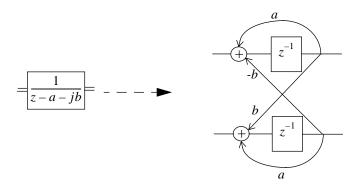

| FIGURE 30. | Complex Integrator using Discrete-Time Delay Blocks 52                |

| FIGURE 31. | STF and NTF for 4th-Order Complex Modulator with no                            |

|------------|--------------------------------------------------------------------------------|

|            | Optimization 54                                                                |

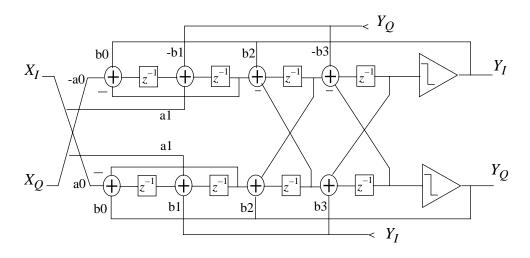

| FIGURE 32. | Z-domain Block Diagram of Complex SD Modulator 55                              |

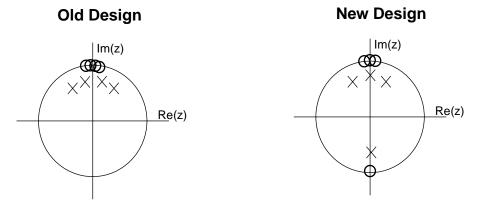

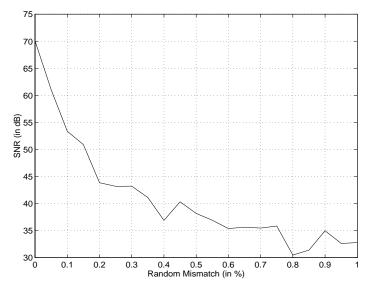

| FIGURE 33. | Effect of Mismatch on Complex SD Modulator A 57                                |

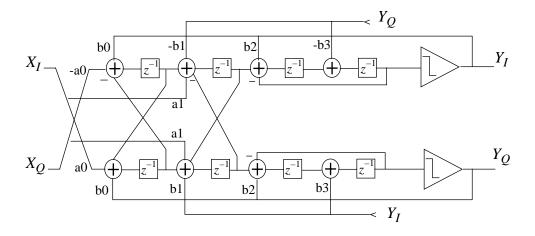

| FIGURE 34. | Z-Domain Diagram of Improved Complex SD Modulator 58                           |

| FIGURE 35. | Effect of Mismatch on Improved Complex SD Modulator 60                         |

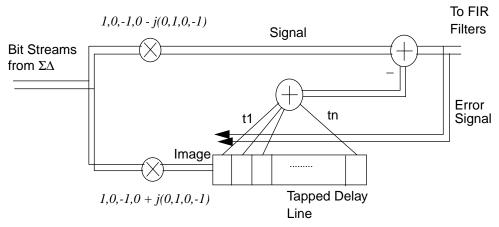

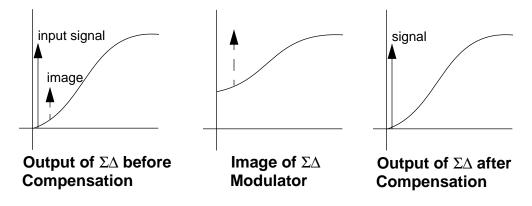

| FIGURE 36. | DSP Solution to Mismatch Problem 62                                            |

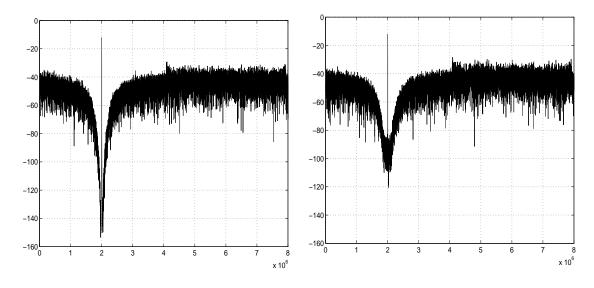

| FIGURE 37. | Comparison of Spectra in the DSP Solution to Mismatch 63                       |

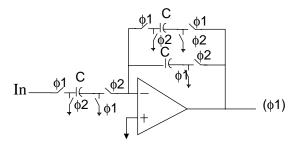

| FIGURE 38. | Switched-C Delay Cell 66                                                       |

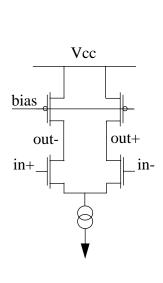

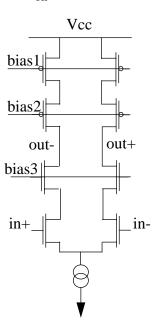

| FIGURE 39. | Single-transistor vs. Cascode Opamp Circuits 67                                |

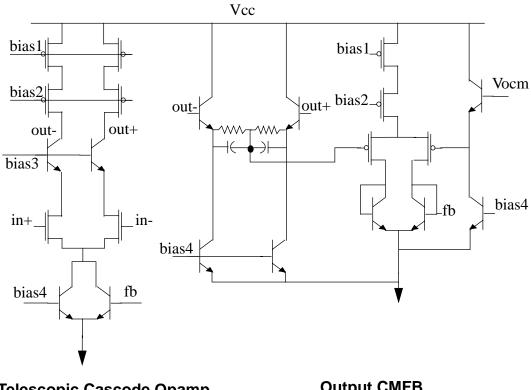

| FIGURE 40. | Telescopic Cascode Opamp used in Complex SD Modulator 68                       |

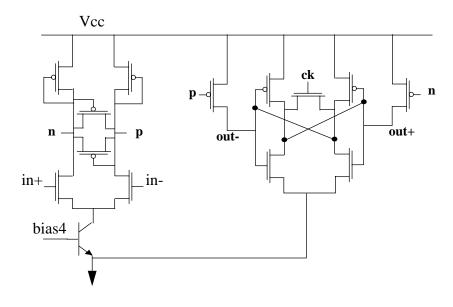

| FIGURE 41. | Comparator used for Modulator 69                                               |

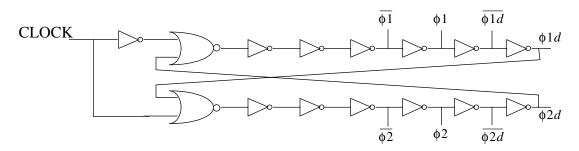

| FIGURE 42. | Clock Generator Schematic 69                                                   |

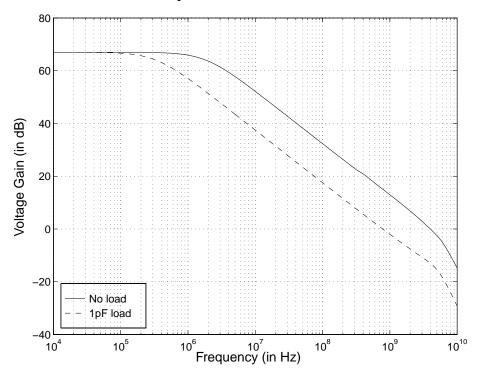

| FIGURE 43. | Opamp Response (Simulated) 71                                                  |

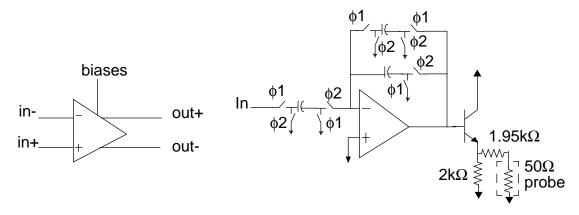

| FIGURE 44. | Test Circuits 72                                                               |

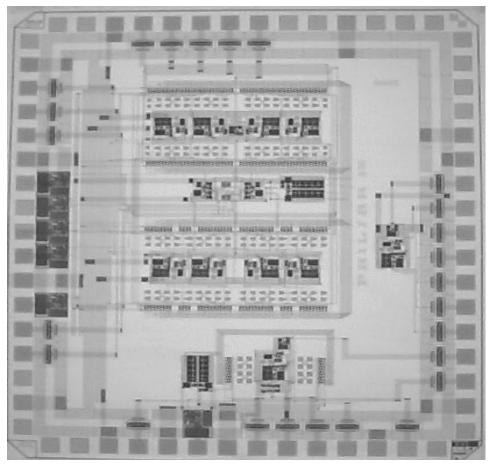

| FIGURE 45. | Layout of Modulator A 73                                                       |

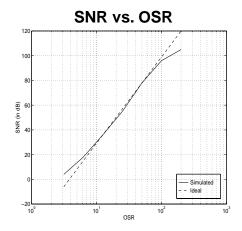

| FIGURE 46. | Performance Graphs of 4th-order Complex SD Modulator 75                        |

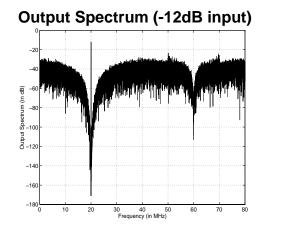

| FIGURE 47. | Simulated Response (non ideal) of Complex SD Modulator 76                      |

| FIGURE 48. | Output Spectrum for Complex Modulator (fs=4 MHz) 78                            |

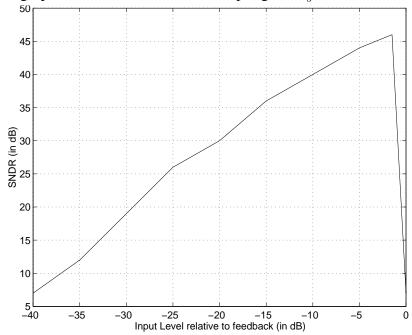

| FIGURE 49. | SNDR vs. Input Level for Complex Modulator (fs = 4MHz) 79                      |

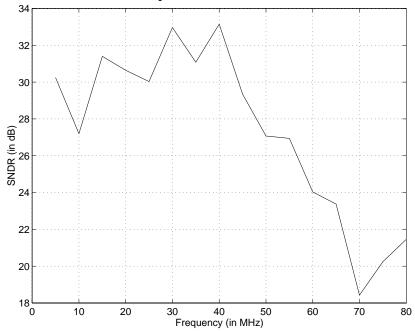

| FIGURE 50. | SNDR vs. Sampling Frequency for Complex SD Modulator (OSR = 200) 80            |

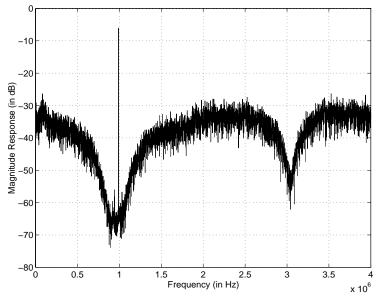

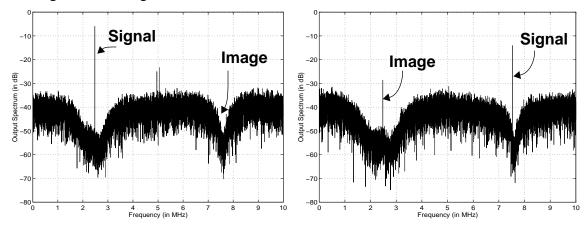

| FIGURE 51. | Image Rejection (experimental) of the Modulator 81                             |

| FIGURE 52. | Image Rejection (simulated) of the Ideal Modulator for random 1% mismatches 82 |

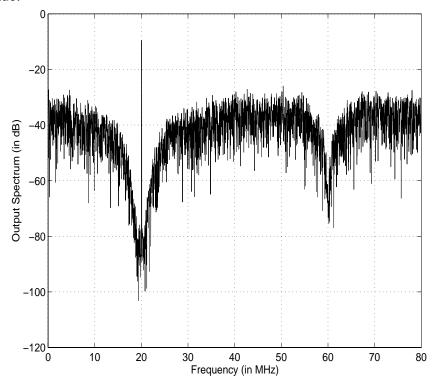

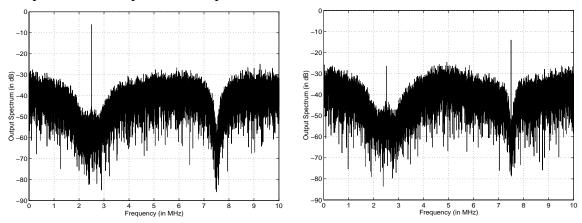

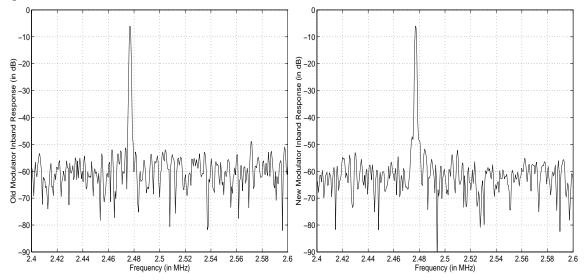

| FIGURE 53. | Spectrum Comparison of Old Modulator vs. New Modulator 83                      |

| FIGURE 54. | Comparison of Inband Spectra after Scaling Reference Voltages 84               |

| FIGURE 55. | Comparison of Spectra (Old Modulator) after Scaling Reference<br>Voltages 85   |

| FIGURE 56. | Single-IF Receiver Architecture Revisited 88                                   |

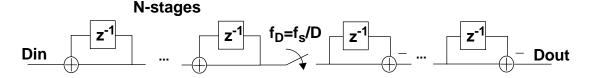

| FIGURE 57. | Decimation for Bandpass SD Modulators 92                                       |

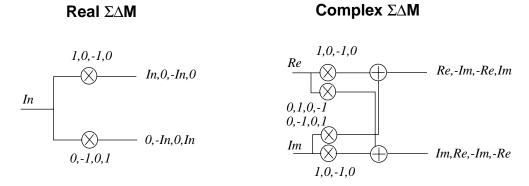

| FIGURE 58. | Digital I/Q Mixer for Real & Complex SD Modulators 93                          |

| FIGURE 59. | CIC Decimator for SD Modulators 95                                             |

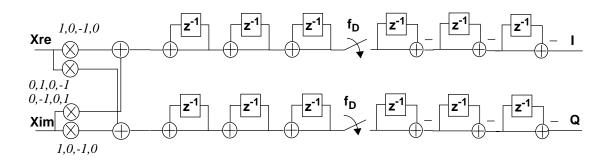

| FIGURE 60. | Complex Decimation Filter Implemented on Xilinx FPGA 96                        |

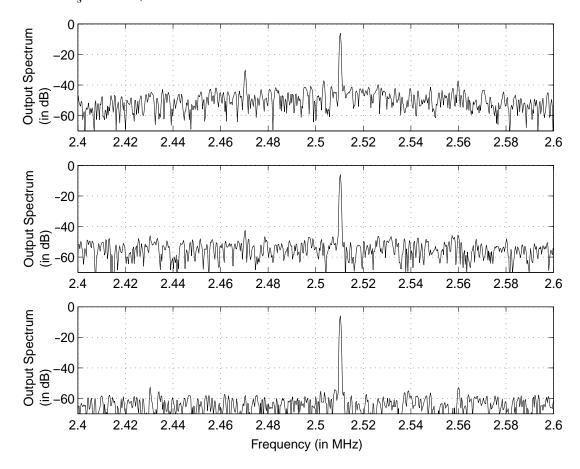

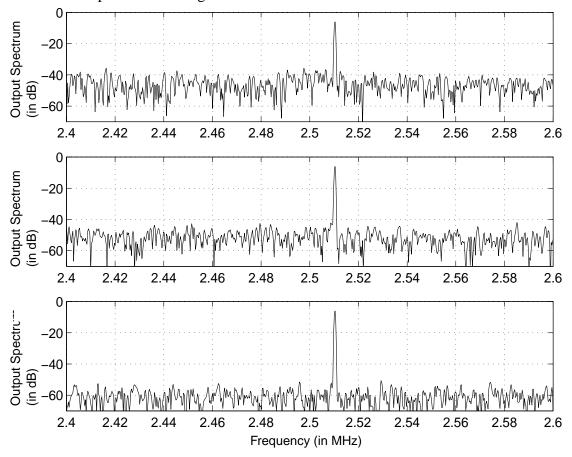

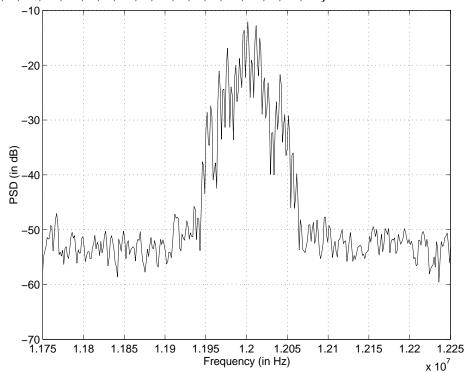

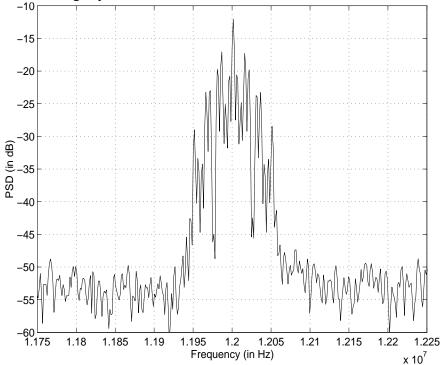

| FIGURE 61. | Performance of receiver, -30 dBm input tone 98                                 |

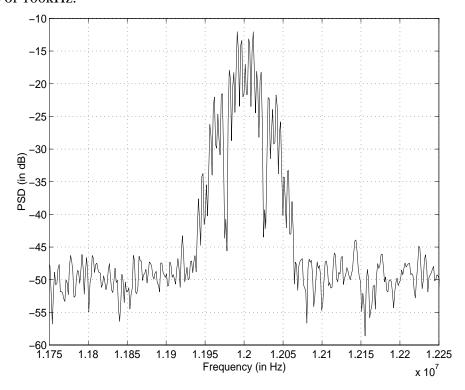

| FIGURE 62. | Spectra of Ideal GMSK and SD Modulator output 99                               |

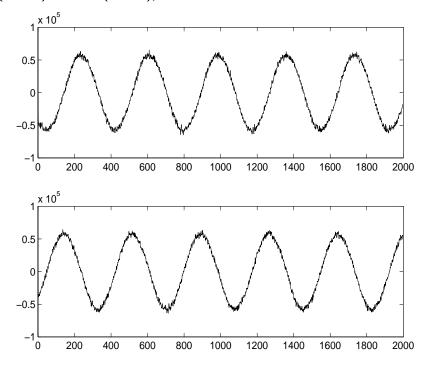

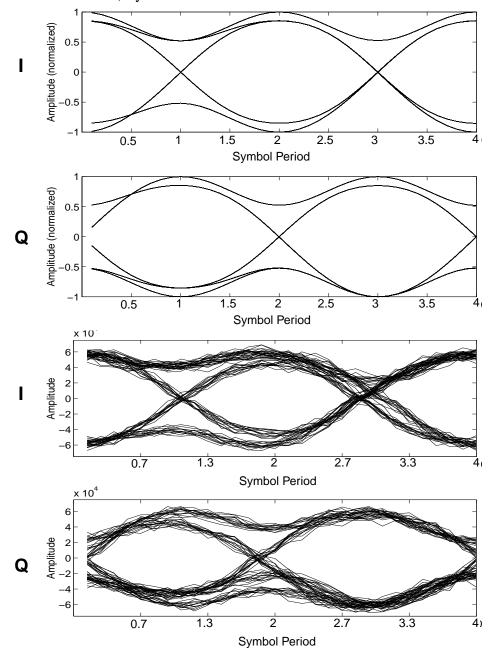

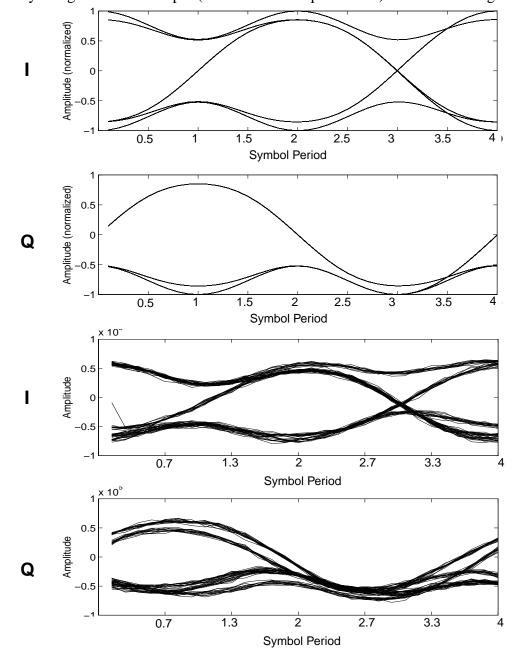

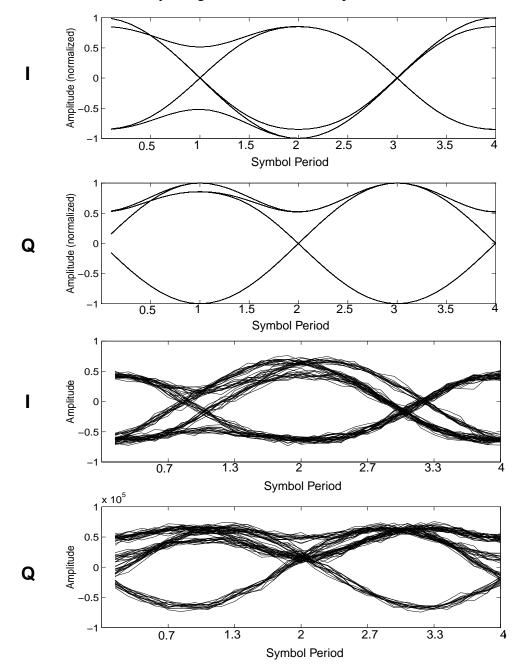

| FIGURE 63. | Eye Diagrams for receiver - Simulated and Experimental 100                     |

|            |                                                                | VIII |

|------------|----------------------------------------------------------------|------|

| FIGURE 64. | Simplified Z-Domain Block Diagram for calculating Coefficients | 114  |

| FIGURE 65. | Complex Coefficient Implementation 114                         |      |

| FIGURE 66. | Output Spectra of Modulator for GMSK Data 122                  |      |

| FIGURE 67. | Eye Diagrams (Simulated and Experimental) for GMSK Data 123    | 3    |

| FIGURE 68. | Output Spectra for GMSK Data 124                               |      |

| FIGURE 69. | Eye Diagrams (simulated and experimental) for GMSK Data 125    |      |

|            |                                                                |      |

|            |                                                                |      |

|            |                                                                |      |

# List of Tables

| TABLE 1.  | Specifications of some PCS Standards 19                        |

|-----------|----------------------------------------------------------------|

| TABLE 2.  | Coefficients for Complex SD Modulator 55                       |

| TABLE 3.  | Coefficients for Improved Complex SD Modulator 59              |

| TABLE 4.  | Simulated Performance of Circuit elements of Modulator 72      |

| TABLE 5.  | LNA Performance Specs (simulated) 89                           |

| TABLE 6.  | Notch Filter Performance Specs (experimental) 90               |

| TABLE 7.  | Mixer Performance Specs (experimental) 90                      |

| TABLE 8.  | Complete Receiver Specs (single mixer, experimental) 91        |

| TABLE 9.  | Complex SD Modulator Specs for Receiver Design 91              |

| TABLE 10. | Aliasing Attenuation vs. Filter Order & Signal Bandwidth (from |

|           | [Hog81] 94                                                     |

| TABLE 11. | Receiver Parameters 97                                         |

# Glossary of Terms

| ΣΔΜ    | Sigma-Delta Modulator                                |

|--------|------------------------------------------------------|

| AGC    | Automatic Gain Control                               |

| AWGN   | Additive White Gaussian Noise                        |

| BER    | Bit Error Rate                                       |

| BiCMOS | Bipolar Complementary Metal Oxide over Semiconductor |

| ΒΡΣΔΜ  | Bandpass Sigma-Delta Modulator                       |

| CΒΡΣΔΜ | Complex Bandpass Sigma-Delta Modulator               |

| CLB    | Carry Look-ahead Buffer                              |

| CMFB   | Common-Mode Feedback                                 |

| IF     | Intermediate Frequency                               |

| INTF   | Image Noise Transfer Function                        |

| IP3    | Third-Order Intercept Point                          |

| ISTF   | Image Signal Transfer Function                       |

| LMS    | Least-Mean Squares                                   |

| LNA    | Low Noise Amplifier                                  |

| LO     | Local Oscillator                                     |

| MSA    | Maximum Stable Amplitude                             |

| NF     | Noise Figure                                         |

| NTF    | Noise Transfer Function                              |

| OSR    | Over-Sampling Ratio                                  |

| PCN    | Personal Communication Network                       |

| PCS    | Personal Communications System                       |

| RF     | Radio Frequency                                      |

| SC     | Switched-Capacitor                                   |

| SNR    | Signal to Noise Ratio                                |

| STF    | Signal Transfer Function                             |

| TF     | Transfer Function                                    |

| UGBW   | Unity-Gain Bandwidth                                 |

|        |                                                      |

#### CHAPTER 1

## Introduction

"Everything that can be invented has been invented."

- Charles H. Duell, Commissioner, U.S. Office of Patents, 1899.

This thesis is about the design and implementation of a new type of Sigma-Delta Modulator ( $\Sigma\Delta M$ ) called a Complex Bandpass  $\Sigma\Delta M$ . To a lesser extent, it is also about the practicalities of incorporating this into a radio receiver. This circuit, which has been implemented for the first time, is demonstrated in a suitable receiver architecture as a proof-of-concept study.

#### 1.1 Motivation

For designers working on radio receivers, there has always been a push to design for higher performance at lower power. These two constraints are often contradictory however, so receivers trade off between them in order to meet a certain specification.

Traditionally, analog signal processing was used throughout the receiver. But today, more and more people are advocating the use of an Analog-to-Digital (A/D) converter in the receiver. All this does is change the representation of the signal, not the content, but it is

Motivation 2

easier to perform precise filtering with Digital Signal Processing (DSP). Also, DSP can be made programmable, giving one more degree of flexibility on the receiver (e.g. to handle multiple standards).

Existing art offers many ways to build this A/D converter. One way is by using a Bandpass Sigma-Delta Modulator (BP $\Sigma\Delta M$ ). This was first implemented in [Jan92] and has been developed by others for better performance [Lon93]. The reason this is considered to be an improvement for radio receivers is that this performs A/D conversion on the signal at an Intermediate Frequency (IF) and thus moves the A/D converter one step closer to the antenna.

By doing this, we eliminate the need for some analog signal processing circuits which can have limited performance due to component mismatch. DSP is not limited by that, since digital hardware can achieve perfect matching between components. Now a key question is: How can we design the A/D converter to give us maximum performance, where performance is defined both in terms of resolution and bandwidth (BW).

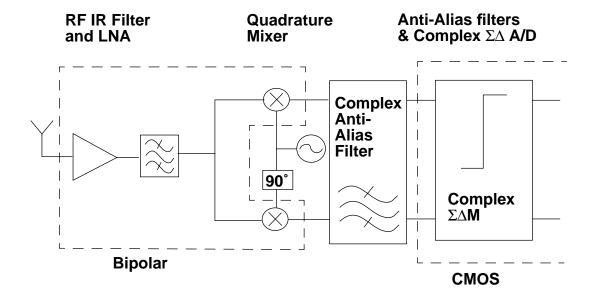

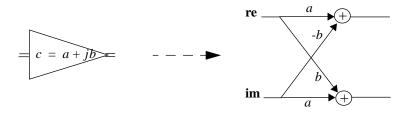

Recently, a new type of BP $\Sigma\Delta M$  has been proposed called a Complex  $\Sigma\Delta M$  [Jan94a][Azi95]. This is especially suited to an image-reject (IR) receiver because it operates on two orthogonal signals, which are found in IR receivers (see Figure 1).

FIGURE 1. A Complex SDM system

Thesis Outline 3

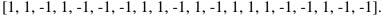

This type of  $\Sigma\Delta M$  is expected to give a factor of 2 improvement on bandwidth relative to a traditional BP $\Sigma\Delta M$  [Azi95]. To demonstrate the feasibility of this type of  $\Sigma\Delta M$ , a platform chip was modified [Phi96]. This allowed for quick design and fabrication of the prototype. The trade off was that the circuit wasn't optimized for this type of modulator architecture. The results outlined within are for the first silicon, to demonstrate the proof-of-concept of this modulator. [Jan97] outlines some results for a fully custom Complex  $\Sigma\Delta M$ .

This  $\Sigma\Delta M$  is ideal for any type of receiver (from AM to GMSK) but to demonstrate its feasibility, we have chosen to test it for a PCS application.

#### 1.2 Thesis Outline

This thesis is roughly split 70/30 between the design and implementation of a Complex  $\Sigma\Delta M$  and the implementation and testing of a Single-IF receiver using a Complex  $\Sigma\Delta M$ . Chapter 2 deals with the specifics of receiver architectures and where the  $\Sigma\Delta M$  fits in. It also discusses some PCS standards and targets GSM as the test standard we will use.

Chapter 3 talks about the theory behind a Complex  $\Sigma\Delta$  Modulator. It also discusses some of the prior art on Bandpass and Complex  $\Sigma\Delta$ M structures.

Chapter 4 is the design and architecture of the two Complex  $\Sigma\Delta M$  prototypes that we designed. It also discusses some of the innovations behind both these modulators.

Chapter 5 details the testing of both Complex  $\Sigma\Delta$  Modulators. It also draws conclusions about the SNR performance degradation that was found.

Chapter 6 presents results for the Complex  $\Sigma\Delta M$  integrated into a Single-IF radio receiver. This is done using an RF of 1.9GHz with GMSK modulation as the test benchmark.

Thesis Outline 4

Chapter 7 draws conclusions about the Complex  $\Sigma\Delta M$  and its feasibility in a radio receiver. It also discusses future enhancements that can be made to improve speed and performance of the modulator.

### CHAPTER 2

## Radio Receivers & PCS

"This 'telephone' has too many shortcomings to be seriously considered as a means of communication. This device is inherently of no value to us."

- Western Union internal memo, 1876

To better understand what specifications we should be designing an A/D converter for, it is important to understand where the A/D fits into a radio receiver. This section outlines the basic principles that radio receivers use, as well as a few examples from existing art on receivers. It also discusses the 'fit' of the A/D converter into these existing receivers, as well as what type of A/D converter would be required for specific receivers. Finally, this section also provides some background into some PCS standards. In the following chapters, we will show that a Complex  $\Sigma\Delta M$  is a feasible choice for an A/D converter for a receiver by using a PCS standard as a benchmark.

### 2.1 Receivers - The Superheterodyne Technique

Most current architectures are 'variations on a theme'; the theme being the superheterodyne radio receiver proposed by Armstrong in the early part of the century [Arm19]. This allowed receivers to be built that used fixed Intermediate Frequency (IF) filters instead of tunable-band ones. The advantage of this was that the fixed filters were

much simpler and had better response than their tunable equivalents. These radio receivers could have any number of IF stages where each IF stage tends to have the same form. This is shown below in Figure 2.

FIGURE 2. Superheterodyne Receiver

This entire receiver could be realized with analog components, but then any sort of mismatch between the circuits in each stage would degrade the performance of the receiver. To prevent this, we could digitize the signal with an A/D converter, because DSP has perfect matching between components. This A/D converter can be placed at any stage in the receiver of Figure 2, from the demodulator to the antenna. The trade-off is that the closer we move the A/D to the antenna, the faster it has to work and the more dynamic range it needs (translation: more expensive A/D) but the less analog components we need for the receiver.

This architecture is used in a lot of radio receivers. Unfortunately, it suffers from a problem with image rejection, which is discussed in the next section.

### 2.2 Image Rejection in Receivers

One major problem with any IF receiver is image rejection. During the mixing stage, some frequency,  $f_{IFI}$ , is mixed with an oscillator signal,  $f_{LO}$ , to produce a signal at  $f_{IF2} = f_{IFI} - f_{LO}$ . However, because mixing convolves both the positive and negative frequency components of a signal to  $f_{IF2}$ , the negative frequency component of the signal at a frequency  $f_{IMGI}$  (= $f_{LO}$ - $f_{IF2}$ ) also gets mapped to the same IF. This can be seen in , where by convolving the signals at  $f_{IMGI}$  and  $f_{IFI}$  by an oscillator signal  $f_{LO}$ , we end up adding the two signal together.

FIGURE 3. Mixing Images on top of Signals

One way to combat this is to filter the image out before the mixing stage [Mac96], but it may be necessary to have 80dB or more attenuation at  $f_{IMGI}$  which is only  $2*f_{IF2}$  away from the desired signal. If  $f_{IF2}$  is small enough, the Image Reject (IR) filter becomes extremely expensive (as it tends to a "brick wall" response). Typically these filter

constraints make  $f_{IF2} \approx f_{IFI}/10 \approx f_{RF}/100$ ; even then it is not possible to filter off the image completely.

Another way to combat this image problem is by using a one-sided oscillator signal to mix the desired signal to the desired IF. This is known in the literature as an Inphase/Quadrature (I/Q) mix or Image Reject mixing. By one-sided oscillator signal, we mean a complex-valued signal  $e^{j\omega t}=\cos\omega t+j\sin\omega t$  that has a one-sided spectrum. But with superheterodyne receivers, image rejection is needed at every stage to insure that no undesirable signals may degrade the quality of reception. This type of receiver has problems with matching between the I and Q channels, as is explained in later sections.

For example, to accomplish true image rejection in both mixers of a dual IF receiver, we would have to get the mixers to do complex mixing (because the second mixer now has both a complex input, and a complex oscillator signal) [Cro95]. This can be seen in Figure 3 where the second IF stage has a complicated arrangement for the mixer. Obviously the shortcoming of this method is that the second stage has four mixers as compared to the two in the first stage. And since the complexity has increased, matching between all the channels becomes even more important since matching errors can accumulate.

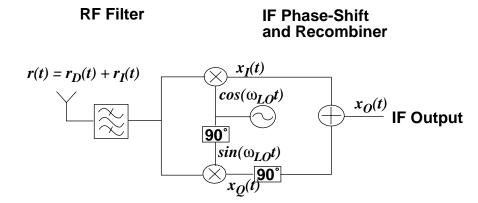

#### FIGURE 4. Example of IR Technique in Dual IF Receiver

Yet another way to perform image rejection is to recombine the signal after each mixing stage [Bau94] as shown in Figure 4. This appears simpler, because we now need only two mixers, one adder, and one 90° phase-shifter, instead of the previous four mixers and two adders. The only problem with this is that the 90° phase-shifter is not trivial to realize, and in fact, can have a phase error of as much as  $\pm 3^{\circ}$  [Alt86]. This is highly layout and process dependent though, and with careful design, can be much less.

FIGURE 5. Another IR Technique for Multiple IF Receivers

Mathematically, real analysis of this kind of system starts with (EQ.1) and (EQ.2) where  $r_D(t)$  is our desired signal,  $r_I(t)$  is the image signal, and r(t) is the combination of these two:

$$\begin{split} x_I(t) &= r(t) \cos \omega_{LO} t \\ &= r_D(t) \cos \omega_{LO} t + r_I(t) \cos \omega_{LO} t \end{split} \tag{EQ 1}$$

$$\begin{split} x_Q(t) &= r(t)\sin\omega_{LO}t\\ &= r_D(t)\sin\omega_{LO}t + r_I(t)\sin\omega_{LO}t \end{split} \tag{EQ 2}$$

This is a mathematically cumbersome way of analyzing an I/Q system. It is far easier to use complex exponentials to represent the signals rather than the preceding functions. We know from elementary complex mathematics that:

$$e^{j\theta} = \cos\theta + j\sin\theta$$

(EQ 3)

Now if we treat  $x_I(t)$  and  $x_Q(t)$  as the real and imaginary parts of a function x(t), we can rewrite (EQ.1) and (EQ.2) as:

$$\begin{split} x(t) &= x_I(t) + jx_Q(t) \\ &= r_D(t)e^{j\omega_{LO}t} + r_I(t)e^{j\omega_{LO}t} \end{split} \tag{EQ 4}$$

For the moment, let us assume that we are amplitude modulating carriers at  $f_{RF}$  and the image  $f_{RF}$  -  $2f_{IF}$  (it turns out that the derivation for frequency modulation is similar [Vie95]). This gives the following for  $r_D(t)$  and  $r_I(t)$ :

$$r_D(t) = a(t)\cos\omega_{RF}t$$

$$r_I(t) = b(t)\cos(\omega_{RF} - 2\omega_{IF})t \tag{EQ 5}$$

Or, in complex notation,

$$r_D(t) = \frac{a(t)}{2} \left[ e^{j\omega_{RF}t} + e^{-j\omega_{RF}t} \right]$$

(EQ 6)

$$r_I(t) = \frac{b(t)}{2} [e^{j(\omega_{RF} - 2\omega_{IF})t} + e^{-j(\omega_{RF} - 2\omega_{IF})t}]$$

(EQ 7)

Where  $f_{IF} = f_{RF} - f_{LO}$ . After substituting this into (EQ.1) and (EQ.2) and removing the high frequency terms, we get:

$$x_I(t) = \frac{1}{2}a(t)\cos\omega_{IF}t + \frac{1}{2}b(t)\cos(-\omega_{IF}t)$$

(EQ 8)

$$x_{Q}(t) = \left(-\frac{1}{2}\right)a(t)\sin\omega_{IF}t - \frac{1}{2}b(t)\sin(-\omega_{IF}t) \tag{EQ 9}$$

or,

$$x(t) = \frac{a(t)}{2}e^{-j\omega_{IF}t} + \frac{b(t)}{2}e^{j\omega_{IF}t}$$

(EQ 10)

Then, if we delay (phase shift)  $x_Q(t)$  by 90°, we get the following for  $x_O(t)$ :

$$x_O(t) = \frac{1}{2}a(t)\cos\omega_{IF}t + \frac{1}{2}b(t)\cos(-\omega_{IF}t) + \frac{1}{2}a(t)\cos\omega_{IF}t - \frac{1}{2}b(t)\cos(-\omega_{IF}t)$$

$$x_O(t) = a(t)\cos\omega_{IF}t \tag{EQ 11}$$

In the complex world, this is equivalent to having positive-pass filter and only looking at the real part of the output. We mentioned before that there could be a possible  $\pm 3^{\circ}$  phase error from a '90°' phase-shifter. This causes some of the image signal to be present in the IF output. Assuming that the phase error ( $\Delta\theta$ ) is completely in the quadrature (sin) channel of the Local Oscillator (LO), we can rewrite  $x_O(t)$  as:

$$\begin{split} x_Q(t) &= r(t)\sin(\omega_{LO}t + \Delta\theta) \\ &= r_D(t)\sin(\omega_{LO}t + \Delta\theta) + r_I(t)\sin(\omega_{LO}t + \Delta\theta) \end{split} \tag{EQ 12}$$

And after substituting the previously defined formulae for  $r_D(t)$  and  $r_I(t)$  in (EQ.5) we get:

$$\begin{split} x_Q(t) &= -\frac{1}{2}a(t)\sin(\omega_{IF}t - \Delta\theta) - \frac{1}{2}b(t)\sin(-\omega_{IF}t - \Delta\theta) \\ &= -\frac{1}{2}a(t)[\sin\omega_{IF}t\cos\Delta\theta - \cos\omega_{IF}t\sin\Delta\theta] - \\ &= \frac{1}{2}b(t)[\sin(-\omega_{IF}t)\cos\Delta\theta - \cos(-\omega_{IF}t)\sin\Delta\theta] \end{split} \tag{EQ 13}$$

Assuming that  $\Delta\theta$  is small so that  $\cos\Delta\theta = 1$  and  $\sin\Delta\theta = \Delta\theta$  yields:

$$x_{Q}(t) = -\frac{1}{2}a(t)[\sin\omega_{IF}t - \Delta\theta\cos\omega_{IF}t] - \frac{1}{2}b(t)[\sin(-\omega_{IF}t) - \Delta\theta\cos(-\omega_{IF}t)]$$

(EQ 14)

And after phase shifting this by 90° and adding to  $x_I(t)$ , we find that  $x_O(t)$  is:

$$x_O(t) = a(t)\cos\omega_{IF}t + \frac{1}{2}\Delta\theta a(t)\sin\omega_{IF}t + \frac{1}{2}\Delta\theta b(t)\sin\omega_{IF}t \qquad \text{(EQ 15)}$$

We can see that not only do we have a phase-shifted copy of the signal in our output, but the image signal also gets aliased in (albeit attenuated by  $\sin \Delta \theta$ )! Typical values of phase error ( $\pm 3^{\circ}$ ) would produce approximately. -25dB of image alias into the signal. This specification is often called the Image Rejection (IR) of a quadrature system.

IR receivers tend to be rare in practical applications because of this mismatch problem. But the superheterodyne receiver remains one of the most popular types of radio receivers today. It is widely used in the growing market for high-frequency telecommunications and satellite communication [Mar95][McD92].

### 2.3 Existing Art - Dual IF Receiver

The dual IF receiver has been the traditional choice for most applications. [Rap94] discusses some of the characteristics of the components of a typical dual IF receiver built mostly out of discrete components.

#### FIGURE 6. Dual IF Receiver

This view of receivers assumes that most of the high frequency components would be discrete, due to coupling and harmonic distortion that would be present in an integrated solution. The drawback of this is that matching is even worse with discrete components than with an integrated circuit. Currently however, RF and high frequency IF circuits are being integrated with good performance [Mac96][Ste95]. This all points towards a more compact view of a receiver, where a two or three chip solution may be all that is required. Also, this receiver has problems with image rejection. The filters in each of the stages have to be able to attenuate image signals that are 65dB more powerful than the desired signal [Zvo96]. The previous image reject schemes that we looked at all increase the complexity of this receiver, and with discrete components, that could mean worse performance due to matching.

Another fact that is addressed is the role of the A/D converter in this receiver. [Rap94] states that if we would like to integrate as much of the receiver as possible, we can use an A/D to convert the band-limited second IF. This may make using a flash A/D converter expensive, since it has to sample at twice the IF with 12 to 13 bit resolution. At any rate, this still doesn't help us with the image rejection problem that this receiver faces.

#### 2.4 Existing Art - Direct Conversion

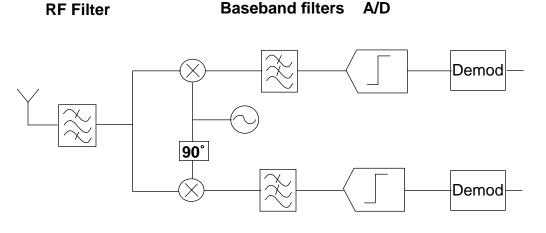

Another architecture that is used is a Homodyne, or Direct Conversion receiver. This is at the other end of the spectrum from dual IF architectures in that there are zero IF stages. And since there are no IF's, the image get mixed to  $2*f_{RF}$  [Sch90a] outlines an implementation of a receiver suitable for the Digital European Cordless Telephone (DECT) standard. This is shown in Figure 6.

FIGURE 7. Direct Conversion Receiver

This receiver performs the A/D conversion at baseband, and the demodulation after that. It has the advantage that there is a reduced number of analog RF components needed. The disadvantages of this receiver are that is sensitive to coupling, including oscillator feedthrough to DC offset at the output of the mixer, flicker noise (1/f noise) and second

harmonic distortion. Direct conversion receivers are still used today due to their simplicity [Sch90a][Has92][McD92].

### 2.5 Existing Art - Single-IF Receivers

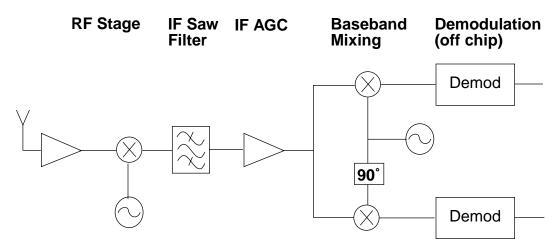

Another receiver that is used the Single-IF receiver [Vie95][Swa96a][Ste95]. The idea behind this receiver is that it is a cross between dual IF and direct conversion architectures, and it can avoid the shortcomings of both. It avoids the DC problems of direct conversion by using an IF and the complexity problems of dual or more IF receivers by only needing one IR filter. A single-IF receiver was developed in [Ste95] and is shown in Figure 7.

FIGURE 8. Single-IF Receiver

This chip doesn't perform data demodulation itself, but provides the inphase (I) and quadrature (Q) channels so that another chip can do the demodulation. This chip still suffers from the image reject problem, and we need a blocking filter after the antenna to attenuate as much of the image as is required. It also suffers from the problem that there might be mismatch in the analog quadrature mixer that causes some of the image to alias on top of the desired signal. The receiver of [Ste95] claims a phase error of 1.2° which

translates to an IR of 36dB. This still means the front-end RF filter still has to filter out 29dB of the image. On top of that, there are still the same problems at the output as for direct conversion receivers (DC offset, LO feedthrough, etc) since the output stage is still analog. All of this points towards the fact that if we can perform A/D conversion somewhere in this receiver chain, we can help minimize some of these problems.

#### 2.6 Receiver Requirements for A/D Converters

As far as the A/D converter for a receiver is concerned, we have many choices. We can use a 2-stage or single-stage Flash A/D converter, but we are limited by the resolution to 10-bits or so.

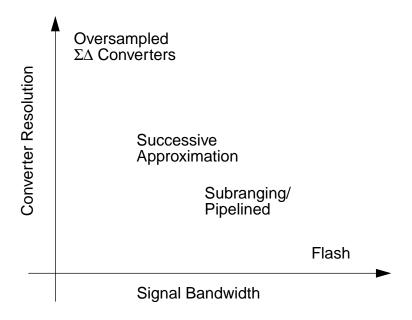

If our desired signal is narrowband, it makes no sense to perform an A/D conversion of the entire frequency band from DC to the IF. By using an Oversampled A/D Converter [Azi96][Can92][Hau91], one can trade bandwidth for resolution. In fact, from [Azi96] we can see a general relation between resolution and bandwidth of A/D converters (Figure 8). Generally speaking, Oversampled  $\Sigma\Delta$  Modulators (or just  $\Sigma\Delta$  Modulators) rely on what the name implies: oversampling a signal. This accomplishes two things; it reduces the quantization noise that is present and it reduces the effective bandwidth of our signal relative to the sampling rate, so anti-alias filters in front of the A/D converter don't need ideal responses. If we oversample significantly (>8 times the Nyquist rate) we can put this filter and the A/D in a feedback loop and 'shape' the quantization noise out of the bandwidth of interest. The choice of filter for this modulator determines where this noise

shaping will be. For example, a lowpass filter means that a notch would appear at DC, and a bandpass filter means that the notch would appear at some  $f_{\rm IF}$  frequency.

FIGURE 9. Resolution vs. Bandwidth for A/D Converters

By using a bandpass  $\Sigma\Delta$  modulator, we can do narrowband A/D conversion at an IF [Sch89], as opposed to doing it at baseband (like a flash, successive approximation, etc.). If we use a standard bandpass  $\Sigma\Delta$  modulator [Sin94][Lon93][Jan93], we can get reasonable performance, but we end up performing an A/D conversion on both the desired signal (at  $f_{IF}$ ) and the image signal (at  $-f_{IF}$ ) when we don't have to.

An added advantage is that since an A/D converter is a sampled system (the frequency response is periodic with the sampling rate), we can undersample the input signal in order to use a higher  $f_{IF}$  with respect to the sampling rate of the  $\Sigma\Delta M$ .

Recently, a new type of bandpass  $\Sigma\Delta$  modulator has been proposed, called a Complex Bandpass  $\Sigma\Delta$  Modulator [Jan94a][Azi95]. This modulator capitalizes on the fact that we

are dealing with a complex signal (I and Q) as the input, so we can get a better notch for the desired signal at  $f_{IF}$ , and a correspondingly worse notch for the image signal at  $f_{IF}$ . Figure 9 outlines a possible receiver. The specifics behind the complex  $\Sigma\Delta$  modulator are explored in depth in the next chapter.

FIGURE 10. Proposed Single-IF Receiver with Complex  $\Sigma\Delta$  Modulator

It is theoretically possible to integrate all these components together on a single chip, but it is not very practical. Switching noise from the A/D converter can very easily be coupled into the sensitive RF front-end components, resulting in a significant increase of Noise Figure (NF) and reduction of Signal to Noise Ratio (SNR). Also, one is limited by the process - the A/D is typically CMOS and the high speed front-end is typically bipolar due to the requirement for high speed/low power circuits operating at 1.9GHz. CMOS front-end circuits have been reported at high frequencies [Kin96][Abo96][Por96], but bipolar processes still offer faster transistors, with higher gains for lower power, and lower NF.

A more realistic partitioning is shown in Figure 9. The 1.9GHz front-end components (Low Noise Amplifier or LNA, Filter & Quadrature Mixer) are shown integrated in a

Bipolar process. The front-end filter is meant to perform rough band-select (for GSM, the receive bandwidth is 25MHz). The whole front-end has been shown as a fully integrated solution, discussed in [Mac96]. The complex  $\Sigma\Delta$  modulator is shown integrated in a high-speed CMOS process. The complex anti-alias filter provides rough channel select, anti-alias filtering (since the A/D is a sampled-data circuit) and isolation between the 'noisy' CMOS switched circuit and the sensitive front-end Bipolar circuits.

#### 2.7 Emerging Standards for PCS

Personal communication devices (like cellular and cordless phones) are becoming more and more used in today's society. In fact, there are an estimated 20 million users of cellular and cordless phones in the United States alone [Pad95]. The important distinction between cellular and cordless systems is that cellular systems are meant to service highly mobile clients within a fairly large cell (10 km or less) with a single base station, while cordless systems typically operate with a single base station/client pair with very limited range (100 metres).

In the next generation of cellular phones, more emphasis is placed on increasing the number of cell phone users in the available spectrum. In these networks, multiple clients are handled by one base station (similar to mobile cellular systems) but the transmit power of the handset is greatly reduced from cellular systems (10mW vs. 600mW) and therefore the cell size is greatly reduced (500 metres). The term PCS is often applied to both microcellular networks, and to digital transmission at an RF of 1.9GHz.

A few of the standards that are being designed for both cellular and cordless are CT2, DECT, DCS-1800 (GSM at a higher RF), IS-95, and PACS. Some specifications on these standards from [Pad95][Cox92] are summarized in Table 1.

TABLE 1. Specifications of some PCS Standards

| Standard                          | CT2                | DECT               | DCS-<br>1800<br>(GSM)          | IS-95              | PACS          |

|-----------------------------------|--------------------|--------------------|--------------------------------|--------------------|---------------|

| Freq. Band (MHz)                  | 864-868            | 1800-1900          | 1710-<br>1785<br>1805-<br>1880 | 869-894<br>824-849 | 1850-<br>1910 |

| Multiple Access                   | TDMA/<br>FDMA      | TDMA/<br>FDMA      | TDMA/<br>FDMA                  | CDMA/<br>FDMA      | TDMA/<br>FDMA |

| Channel Spacing (kHz)             | 100                | 1728               | 200                            | 1250               | 300           |

| Modulation                        | GFSK<br>(BT = 0.5) | GFSK<br>(BT = 0.5) | GMSK<br>(BT = 0.3)             | QPSK               | π/4 QPSK      |

| Bit Rate (kb/s)                   | 72                 | 1152               | 270.833                        | 1228.8<br>(chip)   | 384           |

| Channels/Carrier                  | 1                  | 12                 | 8                              | 40-64              | 8             |

| Portable Xmit<br>Power (avg., mW) | 5                  | 10                 | 125                            | 50                 | 25            |

As we can see from this, a radio receiver should be versatile enough to handle the wide spread of channel bandwidths, modulations and RF carriers if it is to be used internationally. And it should also use as little power as possible, which may be at odds with the previous requirement. But currently, researchers are looking into designing transceivers to operate at the above frequencies, with a maximum power consumption less than 100mW during transmit and receive [Mar95][Vie95].

Receiver Requirements 21

### 2.8 Receiver Requirements

Once a receiver architecture has been settled on, it is important to translate the high-level specifications (like transmit power, channel spacing, etc.) into requirements for each component in the receiver. As we can see from Table 1, three of the five standards that we mentioned have bandwidths in the range of 200kHz. DECT and IS-95 (which uses CDMA) are wider band (more than 1MHz). So, for the rest of this thesis, we will try to prove that a complex  $\Sigma\Delta M$  can be integrated in the next generation radio receivers by using a GSM-like standard as the prototype setup (DCS-1800 is like GSM at a higher RF [Cox92]).

[Zvo96] summarizes some of these important parameters for GSM that were derived from the specification. The maximum Noise Figure (NF) that the receiver can have is 8dB. This is so the SNR for the received signal can be greater than 11dB. The receiver typically has a mechanism of automatic gain control (AGC) which amplifies the input so the minimum bit error rate (BER) is met. This AGC range is generally at least 64dB, which covers the range from the minimum reference sensitivity level (-102dBm to -38dBm).

Other specifications can also be stated for the receiver. Compression characteristics of the components in the receiver should be designed so that large interferers (such as +65dB alternate channel interferers) do not affect the reception of the desired signal, particularly for I/Q demodulators.

The GSM specifications also have requirements for the A/D converter as well as for the front-end receiver. The required performance of the converter can be set to 11 bits per channel by the required 64dB spurious free dynamic range. But with an AGC, the performance of the converter can be less. The BW in which we need this resolution is only 200 kHz. This makes using a  $\Sigma\Delta$  Modulator ideal, since it can give us high resolution in a

Summary 22

narrow band. So, our complex  $\Sigma\Delta M$  design should focus on trying to achieve this resolution in the specified bandwidth.

#### 2.9 Summary

Existing receiver architectures were discussed as variations on the Superheterodyne architecture, the two major choices being direct conversion and dual IF. A compromise between these was also discussed: the Single-IF receiver. This receiver is meant to capitalize on the advantages of both direct conversion and dual IF, while avoiding the pitfalls of both. It is also important to recognize the trade-off in placing the A/D converter in the receiver. Placing it nearer to the antenna reduces the number of analog components, but increases the cost of the A/D.

The requirements of a GSM receiver were discussed, specifically NF and dynamic range. From the general GSM specification, the minimum A/D converter resolution and bandwidth was also stated. We shall see in later sections whether it is possible to design the complex  $\Sigma\Delta M$  to meet these specifications.

CHAPTER 3

## Complex $\Sigma \Delta Modulator$ Theory

"Any sufficiently advanced technology is indistinguishable from magic."

- Arthur C. Clarke

In the previous section we looked at some existing receivers which suggested that there is a need to develop an A/D converter that would help move some of the signal processing to the digital side. This is partly because matching is perfect in DSP, so circuits with ideal responses can be realized.

This chapter focuses on the theory behind a proposed A/D converter called a complex  $\Sigma\Delta$  modulator. This is based on existing lowpass and bandpass  $\Sigma\Delta$  modulators and is shown to have an improvement on bandwidth over these modulators at a given clock rate.

#### 3.1 $\Sigma\Delta$ Modulation

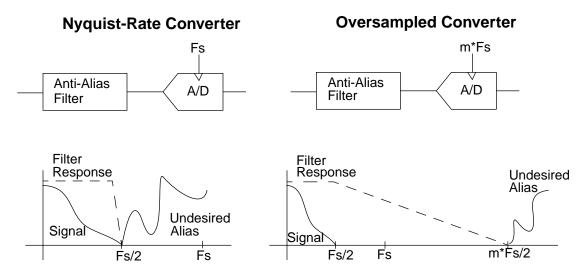

The operation of Sigma-Delta Modulators ( $\Sigma\Delta M$ ) is fairly well understood in the literature [Can92][Can85][Hau91].  $\Sigma\Delta M$  combine two distinct operations: oversampling and noise shaping. It is well known that an A/D converter only has to sample at the Nyquist rate in order to digitize the band of interest (hence the name 'Nyquist Rate Converters'). This, however, means that the front-end anti-alias filter has to have a brick wall response at half

SD Modulation 23

the sampling rate (see Figure 10). But if we oversample the input signal, our anti-alias filter can be fairly relaxed, as is seen in Figure 10. So, instead of being a high-order Chebyshev or Elliptic filter, this anti-alias filter can be as simple as an RC lowpass (if the oversampling is fairly high compared to the bandwidth of the signal).

Oversampling also has another effect on A/D quantization noise. For a sufficiently 'busy' input signal [Can81], one can assume that the quantization noise of the A/D converter is Additive White Gaussian Noise (AWGN) [Hau91]. The total noise power is dependent on the resolution of the A/D converter, but independent of the bandwidth. So, oversampling an A/D converter will spread this noise over a wider bandwidth, which allows more of it to be filtered off in DSP.

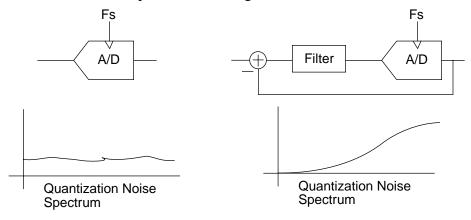

FIGURE 10. Anti-Alias Filter Requirements for Oversampling

Noise shaping refers to moving quantization noise from our band of interest to outside this band. Once again, assuming that the noise is AWGN, we can use feedback to remove noise from low frequencies (say 0-4kHz for voice band) at the cost of increasing the noise at

SD Modulation 24

higher frequencies out of our signal band. This is done by imbedding a filter and the A/D converter in a feedback loop as is seen in Figure 11.

FIGURE 11. Effect of Feedback on Noise Shaping

By combining these two concepts, we arrive at the operation of a  $\Sigma\Delta M$ . Now the question remains: How does one design the filter in order to get the right noise shaping.

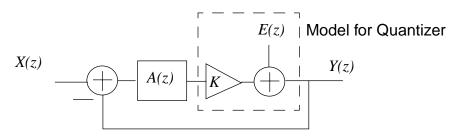

The first thing we can do is develop a linear model of the system in order to mathematically describe it. If we assume that we can represent the modulator as an additive noise source with an input gain of K, we can represent the  $\Sigma\Delta$  modulator as the linear model shown in Figure 12, where E(z) is an AWGN source that represents the noise added by the quantizer (referred to as quantization noise).

#### **Modulator Architecture**

FIGURE 12. Transfer Function Design of 1st-order  $\Sigma\Delta$  Modulator

SD Modulation 25

From this, we can define a Signal Transfer Function (STF) and Noise Transfer Function (NTF) as the gain from the inputs X(z) and E(z) respectively to the output Y(z). The STF only controls the gain that the input signal sees through the A/D converter. The NTF controls the gain that the quantization noise E(z) sees to the output Y(z). Hence, to get noise shaping, we would have to get the NTF to have a gain of zero at some range of frequencies that we are interested in. In other words, we want to place the zeros of the NTF at the narrowband frequencies we would like to quantize.

From the modulator architecture above, we can find the NTF and STF from simple control theory. These are, in terms of the filter A(z):

$$NTF = \frac{Y(z)}{E(z)} = \frac{1}{1 + KA(z)}$$

(EQ 16)

$$STF = \frac{Y(z)}{X(z)} = \frac{KA(z)}{1 + KA(z)}$$

(EQ 17)

To simplify the mathematics, the quantizer gain K is typically assumed to be unity. Here, we can see that the poles of the filter A(z) end up becoming the zeros of the NTF, and the zeros of A(z) become the zeros of the STF. In  $\Sigma\Delta$  modulator design, the NTF zeros are the most important parameter to control since the performance of the modulator is directly related to the magnitude of noise that is within the band we are interested in. In order to insure stability, the poles of the STF and NTF must be within the unit circle in the Z domain. For causality (realizability), we must also make sure the loop is not delay free, hence we usually design A(z) to have at least 1 delay. For example, if we were to replace A(z) with a delaying integrator, we would get the following STF and NTF (assuming K is unity):

SD Modulation 26

$$A(z) = \frac{1}{z-1}$$

$$NTF = \frac{1}{1+A(z)} = \frac{z-1}{z}$$

$$STF = \frac{A(z)}{1+A(z)} = \frac{1}{z}$$

(EQ 18)

In the Z domain, the STF and NTF look like:

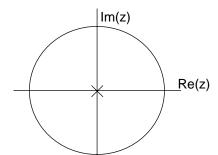

#### **STF Pole-Zero Plot**

#### **NTF Pole-Zero Plot**

FIGURE 13. Pole-Zero Plot for STF and NTF for 1st-Order  $\Sigma\Delta$  Modulator

We have shown a simple first order (with one pole and one zero) NTF and STF but more complicated and higher order NTFs and STFs can be realized through filter optimization [Jan94b][Ris94]. We have also seen that we can 'shape' the quantization noise away from DC (lowpass  $\Sigma\Delta M$ ), but by choosing the appropriate poles and zeros for the filter in the  $\Sigma\Delta M$  feedback loop, we can also shape the noise away from some intermediate frequency. These are normally termed Bandpass  $\Sigma\Delta M$  (BP $\Sigma\Delta M$ ) and are well discussed in the current literature [Sch89][Jan92][Sin94][Lon93][Jan93]. The procedure for designing the NTF and STF for BP $\Sigma\Delta M$  is the same as for lowpass  $\Sigma\Delta M$ .

Complex Filter Theory 27

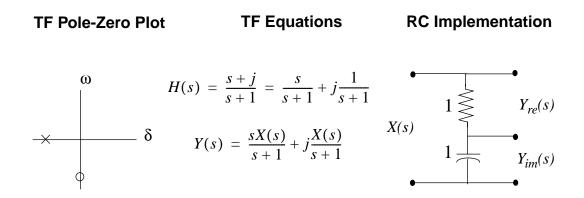

# 3.2 Complex Filter Theory

When designing filters (passive or active), a designer chooses the poles and zeros in order to achieve a desired response, in terms of passband ripple and stopband attenuation. However, in order to realize a real-valued TF, the designer is constrained to having conjugate poles and zeros. If the poles and zeros in the TF are non-conjugate, then the TF ends up having complex coefficients, and therefore a complex-valued filter output [Sne82][All85][Liu86].

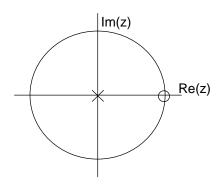

FIGURE 14. Simple Passive Complex Filter

For instance, to realize a given  $H(s) = H_{re}(s) + jH_{im}(s)$ , we can use the system in Figure 14 that has a real input and 2 outputs. The fact that these two outputs correspond to

Complex Filter Theory 28

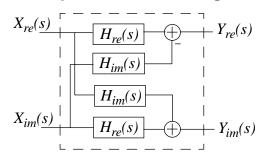

the real and imaginary part mean they represent a complex signal. One can now extend this to more complicated systems. A general complex filter is shown below in Figure 15.

#### **Complex Filter Block Diagram**

FIGURE 15. Generalized Complex Filter (assuming ideal transfer functions)

In the above filter diagram,  $H_{re}(s)$  and  $H_{im}(s)$  are real-valued transfer functions. This architecture might seem overly complicated (having twice as many filter components as two real-valued filters for each channel) but  $H_{re}(s)$  and  $H_{im}(s)$  usually have the same poles, so much of the hardware can be shared. To show how a complex transfer function is derived from this block diagram, we solve for  $Y_{re}(s)$  and  $Y_{im}(s)$ :

$$Y_{re}(s) = H_{re}(s)X_{re}(s) - H_{im}(s)X_{im}(s)$$

$$Y_{im}(s) = H_{re}(s)X_{im}(s) + H_{im}(s)X_{re}(s)$$

(EQ 19)

We can represent  $X_{re}(s)$ ,  $X_{im}(s)$ ,  $H_{re}(s)$  and  $H_{im}(s)$  as complex transfer functions just by multiplying the imaginary part by the complex number j. This gives us complex H(s) and X(s):

$$H(s) = H_{re}(s) + jH_{im}(s)$$

$$X(s) = X_{re}(s) + jX_{im}(s)$$

(EQ 20)

We can see (after some algebraic manipulation) that:

$$Y_{re}(s) = Re[H(s)X(s)]$$

$$Y_{im}(s) = Im[H(s)X(s)]$$

(EQ 21)

So we can also combine  $Y_{re}(s)$  and  $Y_{im}(s)$  into a complex signal.

$$Y(s) = Y_{re}(s) + jY_{im}(s) = H(s)X(s)$$

(EQ 22)

In complex numbers, the imaginary part can be thought of as orthogonal to the real part. Similarly in communication systems, two signals which are orthogonal to each other can be thought of as a complex pair. This makes complex filters especially suited for I/Q communication systems. One may now ask why complex filters aren't used more in communication systems. This is primarily because with conventional monolithic components, it is possible to get as much as 3% mismatch between the I and Q channels (which translates to an image rejection of 25dB). With complex filters, the same mismatch can alter the TF much more, since it is asymmetric (as will be shown later).

## 3.3 Mismatch Effects in Complex Filters

It is easiest to study the effects of mismatch in complex filters by studying an example. [All85] provides an in depth discussion of mismatch, which will be summarized here. We

can take the example complex system of Figure 15, and redraw it if we assume that each transfer function is distinct. This is outlined below in Figure 16.

FIGURE 16. Generalized Complex Filter (assuming component mismatch)

Let us assume that the nominal transfer function of the complex filter is  $H_{NOM}(s)$ . Then we can divide the error in the complex filter into a "common mode" TF, and a "differential" TF [All85]. The "common mode" error ( $\Delta H_{CM}(s)$ ) affects both the real and imaginary channels equally, so it can be applied directly to the input to determine its contribution to the output Y(s). The "differential" error ( $\Delta H_{DIFF}(s)$ ) causes the signal at the input X(s) to appear at its complex conjugate at the output. What is more important is that it causes signals at the conjugate of X(s) to appear directly in the output Y(s). In terms of the TF from Figure 16, this gives the following:

$$\Delta H_{CM}(s) = \frac{H_{re, 1}(s) + H_{re, 2}(s)}{2} + j \frac{H_{im, 1}(s) + H_{im, 2}(s)}{2} - H_{NOM}(s)$$

$$\Delta H_{DIFF}(s) = \frac{H_{re, 1}(s) - H_{re, 2}(s)}{2} + j \frac{H_{im, 1}(s) - H_{im, 2}(s)}{2}$$

(EQ 23)

Figure 17 can be shown to be equivalent to Figure 16 with the transfer functions defined by (EQ.23).

FIGURE 17. Complex Filter with Explicit Error Transfer Functions

For this case, the common mode error is given by  $\Delta H_{CM}(s)$ , the differential error is  $\Delta H_{DIFF}(s)$  and  $\overline{(.)}$  is meant to represent the conjugation operation. We are most concerned about the differential error, since it causes out of band signals to alias inband. For example, take a look at an ideal complex signal  $x(t) = e^{j\omega t}$ . This signal only has power at  $+j\omega$ , but the signal  $y(t) = e^{-j\omega t}$  has power at  $-j\omega$ , the image frequency. If there is any differential error, this image signal propagates to the output along with the original signal. Depending on the structure and layout of the complex filter, mismatch could result in significant performance degradation. One of the problems is that it is hard to quantify this error, without knowing the exact values of each component in the filter. It will be shown in later sections what effects this mismatch has on filters used in a  $\Sigma\Delta M$ .

# 3.4 Complex $\Sigma\Delta$ Modulation

In a BP $\Sigma\Delta M$ , we already stated that the filter in the feedback loop (in Figure 12) has a bandpass response. If we were to replace this with a complex bandpass filter, we realize

complex, and therefore asymmetric NTF and STF [Jan94a][Azi95][Swa96b]. This  $\Sigma\Delta M$  can be analyzed as a complex filter, in that the input is complex (I/Q) and the outputs are single-bit streams, also complex. The obvious advantage to this approach is that a  $\Sigma\Delta M$  can be designed which has good response in positive frequencies, in exchange for worse response at negative frequencies. The desired signal is modulated to positive frequencies while the image goes to negative frequencies, so this would be advantageous.

The reason this is a good idea can be seen by the 'Gerzon & Craven Noise Shaping Theorem' [Ger89] which states that for a given NTF,

$$\int_{0}^{1} \log \left| NTF(e^{j\pi f}) \right| df \ge 0 \tag{EQ 24}$$

Where *f* is the normalized frequency variable. For minimum phase systems, this integral evaluates to 0. This theorem assumes that the transfer function is real-valued, hence has the same magnitude response in both positive and negative frequencies. But for the complex TF case, we can no longer make that assumption. So, for the general case, the theorem should be written as:

$$\int_{-1}^{1} \log \left| NTF(e^{j\pi f}) \right| df \ge 0 \tag{EQ 25}$$

For minimum phase systems (which is typically what most NTF are designed for), this theorem states that if we would like a wider or deeper notch, we have to pay for it by increasing the out-of-band gain so that the integral evaluates to zero. For example in Figure 18, we can see that a simple 1st order lowpass modulator has 6dB out of band gain.

A 2nd order lowpass has a less noise near DC (deeper notch), but the out of band gain increases to 12dB.

FIGURE 18. 1st and 2nd Order Lowpass Modulator NTFs

It is known [Lee87] that for a single-bit quantizer, increasing the out of band gain past a certain point (approximately 1.5) can make the modulator unstable. If we use a complex filter to place more zeros in the passband of the modulator and fewer in the image band, we can see that the out of band gain is still the same, but we have effectively created a deeper notch at the frequency we are interested in. In other words, we have conserved the area below log(NTF) by shifting more of it to one band, instead of sharing it between two different bands.

Complex  $\Sigma\Delta M$  are also useful in multi-band systems [Azi95], where one can design each parallel modulator to have NTF notches at different frequencies. As well as that, complex  $\Sigma\Delta M$  also gain a stability vs. bandwidth advantage over real-valued BP $\Sigma\Delta M$ , in that a 4th-order complex modulator can have the same noise-shaping response as an 8th-order real modulator (see Figure 19), yet with a higher order modulator, it is harder to guarantee stability. Similarly for the same order of modulator, the complex modulator is not

restricted to having conjugate NTF zeros, and therefore can have a better notch at the desired frequency.

#### Real 8th-order NTF (unstable)

FIGURE 19. Complex vs. Real NTFs

The design of a complex  $\Sigma\Delta M$  can be done in a couple of different ways. One way is to place the poles and zeros of the NTF and STF (for stability, poles must be inside the unit circle in the Z-domain), as was done in the previous NTF pole-zero plot. Then an optimizer can be run on this pole-zero placement to determine the optimal NTF and STF, given certain constraints on them (discussed in succeeding sections).

Another method is to transform a real-valued TF into a complex-valued TF. This is already done with BP $\Sigma\Delta M$  by using the following transform [Lon93]:

$$z = -\hat{z}^2 \tag{EQ 26}$$

So, by using this transform,

$$\frac{z-1}{z} \Rightarrow \frac{\hat{z}^2 + 1}{\hat{z}^2} \tag{EQ 27}$$

This transform can work for any function of z, but is typically used on 1st and 2nd order lowpass  $\Sigma\Delta$  Modulators that meet very specific requirements (NTF zeros at 1 and poles at 0 in the Z-domain). And this transform places the zeros at j and -j in the z-domain (corresponding to  $f_s/4$  and  $3*f_s/4$  where  $f_s$  is the sampling frequency of the system). A more general bandpass transformation could be:

$$z = \hat{z}^2 - 2Re \left\{ e^{j\theta} r_1 \right\} \hat{z} - \left| r_1 \right|^2 + r_1$$

(EQ 28)

where  $r_1$  is a root and  $\theta$  is the angle (in radians) at which the poles and zeros are rotated from their original placement. Even though the NTF is stable (i.e. all the poles are within the unit circle), this does not guarantee that the  $\Sigma\Delta$  Modulator itself is stable [Sch89][Ris94].

The idea of transformation can be readily generalized to complex  $\Sigma\Delta M$ . One way of thinking about it is that we are taking a lowpass  $\Sigma\Delta$  NTF pole-zero plot and rotating it in the Z-domain. Generally, this can be written as:

$$z = \hat{z}e^{-j\theta} \tag{EQ 29}$$

where  $\theta$  is the angle of rotation in the Z-domain. For the special case of  $\theta = \pi/2$  (f<sub>s</sub>/4),

$$z = -j\hat{z}$$

(EQ 30)

This is advantageous because it is a simple transformation that can be applied to any lowpass  $\Sigma\Delta M$ . But, once again, this transformation does not guarantee stability. For example in Figure 20, the two NTF are the same, except one is rotated by 90° in the Z-domain. Simulations show that the complex modulator with the rotated pole-zero constellation is unstable. Unfortunately there is no known way to guarantee stability with

a complex  $\Sigma\Delta M$  except by combining NTF design guidelines (which will be outlined in succeeding sections) with extensive simulation.

FIGURE 20. Effect of Complex Transform on NTF Stability

In the end, the preferred method is to optimize a lowpass  $\Sigma\Delta M$  and use the previous transform (EQ.30) to get the complex equivalent. This method will be discussed in the next section.

## 3.5 Mismatch Issues in Complex $\Sigma \Delta M$

One important issue to deal with is mismatch between the I and Q channels of the complex  $\Sigma\Delta$  modulator. In fact, this is an important concern with any I/Q system. We have shown previously (in Chapter 2) that any phase mismatch in the oscillator signal results in an attenuated copy of the image folding onto the desired signal. The same derivation can be done for gain mismatch between the I and Q channels of a quadrature system. And it can be shown that for a 1% gain mismatch between the I and Q channels of a quadrature system (e.g. the quadrature mixer), the image is copied onto the signal with 40dB attenuation [Sne89].

In the complex  $\Sigma\Delta M$  that was designed, we may have more than just gain mismatches between the I and Q channels, because we have cross coupling, in order to realize complex poles and zeros. And we already have stated that for a complex system, mismatch causes

the image to be folded into the signal. This can be disastrous for a complex  $\Sigma\Delta M$ , where any mismatch causes quantization noise at the image frequency (remember we are dealing with a non-symmetric frequency response) to be aliased inband (the deep notch at  $f_s/4$ ). Even if the image quantization noise is attenuated by 40dB before being aliased inband, it can seriously degrade the performance of the modulator. The best example to show this is a modulator that contains all the poles and zeros at  $f_s/4$  (the desired signal frequency) and none at  $f_s/4$  (the image frequency). For this modulator, we choose the poles and zeros to be:

$$Poles = \pm 0.1 + 0.8j, \pm 0.2 + 0.7j$$

$$NTFzeros = e^{j\frac{\pi}{2}}(quadruple)$$

$$STFzeros = \pm 0.1 + 0.8j$$

$$STFgain = 0.25$$

The architecture consists of 4 complex integrators. The frequency responses of these modulators for perfect matching and for 1% random mismatch are shown below in Figure 21.

FIGURE 21. Response of Example Complex  $\Sigma\Delta M$  for 0% and 1% Coefficient Mismatch

The SNR of the ideal modulator is 76dB (in a 1 MHz BW) and only 56dB for the mismatched modulator. From this, we conclude that the average SNR degradation is around 20dB which is a loss of approximately 3.5 bits! Obviously we need to design some kind of fix or workaround for this problem, otherwise using a complex  $\Sigma\Delta$  modulator in a communication system would not be practical.

The reason for this SNR loss in complex  $\Sigma\Delta$  modulators was explained in [Jan96a]. The differential error that was discussed before in complex filters can be expressed as an Image Noise Transfer Function (INTF) and an Image Signal Transfer Function (ISTF). They combine to produce an overall modulator output:

$$Y(z) = G(z)X(z) + H(z)E(z) + G_{I}(z)\overline{X(z)} + H_{I}(z)\overline{E(z)}$$

(EQ 31)

Where G(z), H(z),  $G_I(z)$  and  $H_I(z)$  are the STF, NTF, ISTF, and INTF respectively. These transfer functions represent the gain of the image noise and signal respectively to the inband output of the modulator. The INTF is of most concern, since we could place a complex filter in front of the modulator to attenuate the image signal to the point where the ISTF wouldn't degrade performance. Techniques are discussed in later sections about compensating for the INTF.

## 3.6 Dealing with Mismatch - Notching Image Noise

One technique for controlling the INTF was developed and described in [Jan96a]. This involves placing a NTF zero at the image frequency (for the example in the previous section, this means a zero at 6MHz). So, basically, we notch out some of the noise at the image so that less of it gets aliased into the desired signal because of the INTF (Figure 22). In a 4th-order structure, we can realize this image zero at any stage. The question is: which stage is it better to realize this zero in? The first, middle or last?

FIGURE 22. Notching Image Noise in NTF

This question was also answered in [Jan96a] where it was determined that creating the image zero in the last stage before the quantizer results in less SNR degradation. The

reason for this was stated by an explanation of input referring the noise. In the modulator, the noise at the input to the quantizer is basically white. Input referring it through each preceding stage (infinite gain at the signal frequency) creates a notch in the noise. Any mismatch in the first stages of the modulator are disastrous because they alias image noise into the signal band. If we notch out this noise first (by placing an image pole in the final stage before the quantizer), we have succeeded in attenuating the image noise, so mismatch in the first stage becomes less of a problem.

## 3.7 Dealing with Mismatch - Post Compensation

Another way of dealing with mismatch in a complex  $\Sigma\Delta M$  (or in any complex system for that matter) is to do some gain and phase adjusting after the complex system. For example, let us assume that the ideal output from a complex system is:

$$Y(z) = Y_{ro}(z) + jY_{im}(z)$$

(EQ 32)

And that our actual output is:

$$Y'(z) = Y_{re}(z) + j(aY_{im}(z))$$

(EQ 33)

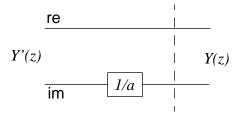

We can compensate for this by adding a gain of 1/a to the imaginary channel as is seen in Figure 23.

FIGURE 23. Gain Compensation for Complex Filter Mismatch

Now let us look at phase mismatches. Say we had a phase mismatch of  $\Delta \phi$  between  $Y_{re}(z)$  and  $Y_{im}(z)$ . Mathematically this would look like:

$$Y'(z) = Y_{re}(z) + je^{j\Delta\phi}Y_{im}(z)$$

(EQ 34)

For  $\Delta \phi = 0$ , this reduces to the ideal output shown in (EQ.32) . For a non zero  $\Delta \phi$ , we can rewrite Y'(z) as:

$$\begin{split} Y'(z) &= Y_{re}(z) + j(\cos\Delta\phi + j\sin\Delta\phi)Y_{im}(z) \\ &= Y_{re}(z) - \sin\Delta\phi Y_{im}(z) + j\cos\Delta\phi Y_{im}(z) \end{split} \tag{EQ 35}$$

Assuming that we know what  $\Delta \phi$  is, we can compensate for this by cancelling the  $Y_{im}(z)$  term in the real part of Y'(z), while adjusting the gain of the imaginary part. This compensation system is shown in Figure 24.

FIGURE 24. Phase Compensation for Complex Filter Mismatches

We should reiterate that this type of mismatch compensation is based on knowing the magnitude of the mismatch to begin with, which is why it is known as non-adaptive DSP compensation. There are ways of doing adaptive compensation [Li97] which are discussed in succeeding chapters.

# 3.8 Complex ΣΔM Transfer Function Design

In order to design a good STF and NTF, it is important to adhere to certain guidelines in order to realize TF stability and realizability. Generally, the out of band and in band gain are designed to adhere to certain criteria. The out of band gain is most important for the NTF and is defined as the TF gain which is well outside the bandwidth of the modulator (usually, the magnitude response of the NTF is flat in the out of band region). The in band gain is defined as the TF gain within the specified bandwidth that the modulator is designed for.

It is not intuitively obvious which NTF are stable and which are unstable, but a guideline was proposed by Lee in [Lee87] for 1-bit quantizers which states that the maximum out-of-band gain of the NTF should be:

$$|H(z)| \le 2 = 6 \text{ dB} \tag{EQ 36}$$

6dB of out of band gain is fairly high as well, which is why  $\Sigma\Delta M$  designers usually optimize for less than 5dB. We can show that there are stable modulator NTF (like the lowpass  $\Sigma\Delta$  modulator in Figure 20) which have an out-of-band gain of 12dB. [Ris94] offers another measure by showing that stability of a modulator is dependent on the probability density function (pdf) of the quantizer error. In most cases, this is assumed to have a gaussian distribution. Risbo also showed that for high order modulators (3rd-order lowpass), this pdf assumption is very accurate. This measure of stability was not used for the design of the modulator so it won't be discussed in detail.

Also, to ensure realizability, the feedback loop in the modulator must not be delay free, hence the requirement:

$$H(\infty) = 1 \tag{EQ 37}$$

The guidelines for designing the STF are more relaxed since its zeros and gain have no effect on the modulator loop and therefore no effect on stability. The STF has the same poles as the NTF, and one relaxed guideline to follow is to keep the in band gain at unity or:

$$|G(z)|=1, |\omega|<\omega_0$$

(Eq 38)

This guideline is not necessary, although if the gain is too high, then reduced dynamic range of the modulator can be the result because the STF amplifies interferers as well as the desired signal.

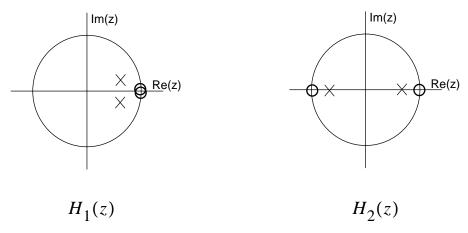

The method that was used to design the STF and NTF for a complex modulator was by optimizing a lowpass  $\Sigma\Delta M$  by providing initial pole and zero placements and using the preceding constraints. Then we could transform it into a complex BP $\Sigma\Delta M$  using the previous complex transformation (EQ.30). The filter optimizer that was used to optimize the STF and NTF was filtorX, a least-pth optimizer for S-domain and Z-domain filters [Ous90]. The criteria for optimization was to meet a certain in band NTF gain, in band STF gain, and out of band NTF gain. As prototype examples, two designs were attempted; a complex 4th-order and a complex 6th-order. For each of these designs, the complex TF consisted of one complex conjugate pole-zero pair. In order to get filtorX to optimize correctly, the STF and NTF were split into two TF: one with the 'conjugate' pole & zero (although for the lowpass prototype case, this means a pole/zero at 0° and 180°) and the other with the rest of the poles and zeros (conjugates for the lowpass case). Mathematically, this looks like:

$$H(z) = H_1(z)H_2(z)$$

$$H_1(z) = \frac{(z-1)^2}{(z^2 + bz + c^2)}$$

$H_2(z) = \frac{z^2 - 1}{z^2 - a^2}$

The poles and zeros of this set of equations look like:

Then the resulting optimized TF were transformed and multiplied together to get the final complex NTF and STF. Using this procedure, the following poles & zeros were obtained for the 6th-order modulator, optimizing for an NTF out of band gain of 5dB, an in band gain of 0 and an STF in band gain of 0dB:

$$Poles = \pm 0.578j, \pm 0.121 + 0.982j, \pm 0.173 + 0.834j$$

$$NTFzeros = e^{\pm j\frac{\pi}{2}}, e^{j\left(\frac{\pi}{2} \pm 0.036\right)}, e^{j\left(\frac{\pi}{2} \pm 0.015\right)}$$

$$STFzeros = 0, \pm 0.221 + 0.864j, \pm 0.122 + 0.988j$$

$$STFgain = 0.563$$

This gave an STF gain of 0 dB in band (where in band is defined as 400kHz around  $f_s/4$  which is 20MHz), an NTF gain of 5.1dB out of band, and an NTF notch depth of 95dB (relative to NTF out-of-band magnitude) for an OSR of 200. The response of this modulator is shown below in Figure 25 for a sampling rate  $f_s = 80$ MHz. There is a notch at

the image frequency the reason being that with complex filters, mismatch causes signals at the image frequency (-20MHz in this case) to be 'folded' onto the desired signal at 20MHz as was already explained previously.