## Signal-dependent timing jitter in continuous-time $\Sigma\Delta$ modulators

J.A. Cherry, W.M. Snelgrove and P. Schvan

Indexing terms: Sigma-delta modulation, Analogue-digital conversion. Modulators

A previously unpublished mechanism of signal-to-noise ratio (SNR) loss specific to continuous-time  $\Sigma\Delta$  modulators is illustrated. It arises from increased quantiser resolution time for small-amplitude quantiser inputs, and is related to metastability.

Clock jitter in  $\Sigma\Delta$  modulators: In sampled-data systems, a time jitter in the sampling clock ('sampling jitter' or 'clock jitter') leads to non-uniform sampling, which adds noise to the sampled signal. A clock jitter in Nyquist-rate analogue-to-digital converters (ADCs) thus leads to a loss in the SNR (signal-to-noise ratio) and hence in the converter resolution [1]. Likewise, a sampling jitter in a discrete-time  $\Sigma\Delta$  ADC increases the total error power in the quantiser output [2]. For a sampling time deviation which is an uncorrelated Gaussian process with variance  $\sigma_j^2$ , this power is proportional to  $\sigma_j^2/OSR^2$ , where OSR is the oversampling ratio; in comparison, the quantisation noise power for an order-M converter is inversely proportional to  $OSR^{2M+1}$ . The tolerable level of clock jitter decreases with increasing OSR, since eventually jitter noise power will exceed quantisation noise power.

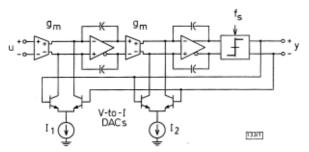

$\Sigma\Delta$  modulators that employ continuous-time circuitry [3, 4] are popular for high speed applications. A typical continuous-time design is depicted in Fig. 1, which is similar to that in [5]. Its feedback DACs convert voltage to current pulses which remain at a constant level throughout a clock period. In such circuits, the integral of the current over the clock period determines modulator behaviour, and this integral varies linearly with timing variations, i.e. clock jitter. In contrast, in a typical discrete-time, e.g. switched capacitor (SC), design, the variation in the amount of charge transferred per clock cycle due to the clock jitter is relatively low because the majority of the charge is transferred at the beginning of a clock period. Hence, continuous-time designs are more sensitive to clock jitter than SC designs [6].

Fig. 1 Second-order continuous-time  $\Sigma\Delta$  modulator

Jitter due to small quantiser inputs: Even with a perfectly uniform sampling clock, an insidious type of timing jitter can creep into a design, such as that of Fig. 1. The one-bit quantiser operates as a voltage comparator with a reference level of zero. A non-negative quantiser input voltage produces a +1 output whence a positive full-period current pulse emanates from the one bit DACs, while a negative input produces a -1 output and a negative DAC current pulse.

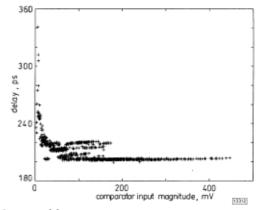

Ideally, the comparator would make a decision a fixed amount of time after the sampling clock edge. However, a practical comparator has a finite gain, hence very small comparator inputs lead to a longer time before the output switches fully to  $\pm 1$ . We define 'loop delay' as the length of time between the sampling clock edge and the DAC current pulse edge. Fig. 2 shows the loop delay against comparator input voltage magnitude for a transistor-level simulation of the circuit in Fig. 1 designed to operate with a 1GHz sampling clock. Indeed, loop delay is constant for large inputs, but rises for increasingly small inputs.

The quantiser input has a zero-mean Gaussian-type shape [2] for modulators of order 2 and above. For these modulators, the quantiser input is essentially uncorrelated with the overall circuit input and appears 'random'; thus, quantiser inputs near  $0\,\mathrm{V}$  will occur at times that appear random. Since 'jitter' usually implies a random error, it is appropriate to denote the variable loop delay due to variable quantiser decision time as a 'signal-dependent timing jitter'. This is a subtle manifestation of the classic metastability problem in digital latches.

Fig. 2 Quantiser delay against quantiser input

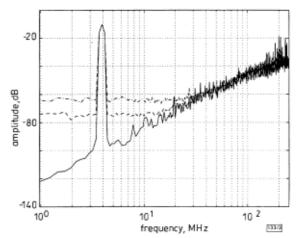

Fig. 3 Output bit stream periodograms

——— fixed quantiser delay

---- quantiser with some signal-dependent jitter

----- quantiser with more signal-dependent jitter

Impact on SNR: Fig. 3 shows the effect of this type of jitter on the noise-shaping behaviour of a  $\Sigma\Delta$  modulator. A computer program that implements Fig. 1 mathematically was employed, with the quantiser delay modelled as

$$delay = d_0 + \frac{d_1}{|v_{in}|^{x_1}} \tag{1}$$

where  $v_{\scriptscriptstyle IN}$  is the quantiser input voltage and  $d_0$ ,  $d_1$ , and  $x_1$  are parameters. For the curve in Fig. 2, estimated values are  $d_0=200\,\mathrm{ps}$ ,  $x_1=2$ , and  $d_1=0.2\,\mathrm{ps}\cdot\mathrm{V}^2$ . 32 averaged Hanning-windowed 4096-point periodograms of the output bit stream are shown in Fig. 3 for these parameter values, plus two additional cases:  $d_1=0$  and  $d_1=20\,\mathrm{ps}\cdot\mathrm{V}^2$ .  $d_1=0$  corresponds to a quantiser with a fixed (unjittered) delay; the SNR for an OSR of 64 is 77.4 dB. The other two cases correspond to a quantiser with a signal-dependent jitter. The spectrum becomes flat (white) at DC; while a finite op-amp gain could also cause this, the spectrum would exhibit greater harmonic content in that case. The SNRs are 55.7 and 45.0 dB for  $d_1=0.2$  and  $d_1=20$ , respectively. Clearly, signal-dependent jitter is detrimental to converter resolution.

Circumventing the problem: One or more pre-amplification stages could be inserted immediately prior to the quantiser, or the quantiser gain itself could be increased, reducing the probability of the quantiser input being too close to zero to resolve quickly. Or, as in [5], a latch might be inserted between the quantiser output and the DACs. This latch could be clocked, for example, one half sample after the quantiser, which gives the quantiser up to half a sample to settle. The DAC current pulse edge would then depend only on the jitter in the latch clock.

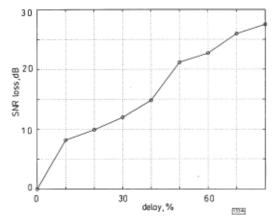

Fig. 4 Effect of loop delay on SNR

The problem with either method, or even both combined, is that increasing the loop delay, even by a fixed amount, is detrimental to the SNR [3]. Fig. 4 shows how much the SNR is lost against fixed quantiser delay for the circuit of Fig. 1, where the delay is expressed as a percentage of the sampling clock period and the OSR is 64. It is seen that a latch that introduces half a sample delay, as was apparently implemented in [5], leads to an SNR loss of 21dB. It may be that a signal-dependent jitter causes less SNR loss than introducing a fixed loop delay; a compromise that depends on the architecture and system parameters must usually be sought.

© IEE 1997 28 April 1997

Electronics Letters Online No: 19970779

J.A. Cherry and W.M. Snelgrove (Department of Electronics, Carleton University, 1125 Colonel By Drive, Ottawa, Ontario, K1S 5B6, Canada)

P. Schvan (Nortel Technology, PO Box 3511, Station C, Ottawa, Ontario, K1Y 4H7, Canada)

## References

- 1 HARRIS, S.: 'The effects of sampling clock jitter on Nyquist sampling analog-to-digital converters, and on oversampling delta-sigma ADCs', J. Audio Eng. Soc., 1990, 38, (7/8), pp. 537–542

- 2 BOSER, B.E., and WOOLEY, B.A.: 'The design of sigma-delta modulation analog-to-digital converters', *IEEE J. Solid-State Circuits*, 1988, 23, (12), pp. 1298–1308

- 3 SHOAEI, O.: 'Continuous-time delta-sigma A/D converters for high speed applications'. PhD thesis, Carleton University, Ottawa, Canada, 1995

- 4 SCHREIER, R., and ZHANG, B.: 'Delta-sigma modulators employing continuous-time circuitry', *IEEE Trans. Circuits Syst. I*, 1996, **43**, (4), pp. 324–332

- 5 JENSEN, J.F., RAGHAVAN, G., COSAND, A.E., and WALDEN, R.H.: 'A 3.2 GHz second-order delta-sigma modulator implemented in InP HBT technology', IEEE J. Solid-State Circuits, 1995, 30, (10), pp. 1119– 1127

- 6 VAN DER ZWAN, E.J., and DIJKMANS, E.C.: 'A 0.2mW CMOS ΣΔ modulator for speech coding with 80dB dynamic range', *IEEE J. Solid-State Circuits*, 1996, **31**, (12), pp. 1873–1880